Analog-to-Digital Converter (ADC) RM0046

596/936 Doc ID 16912 Rev 5

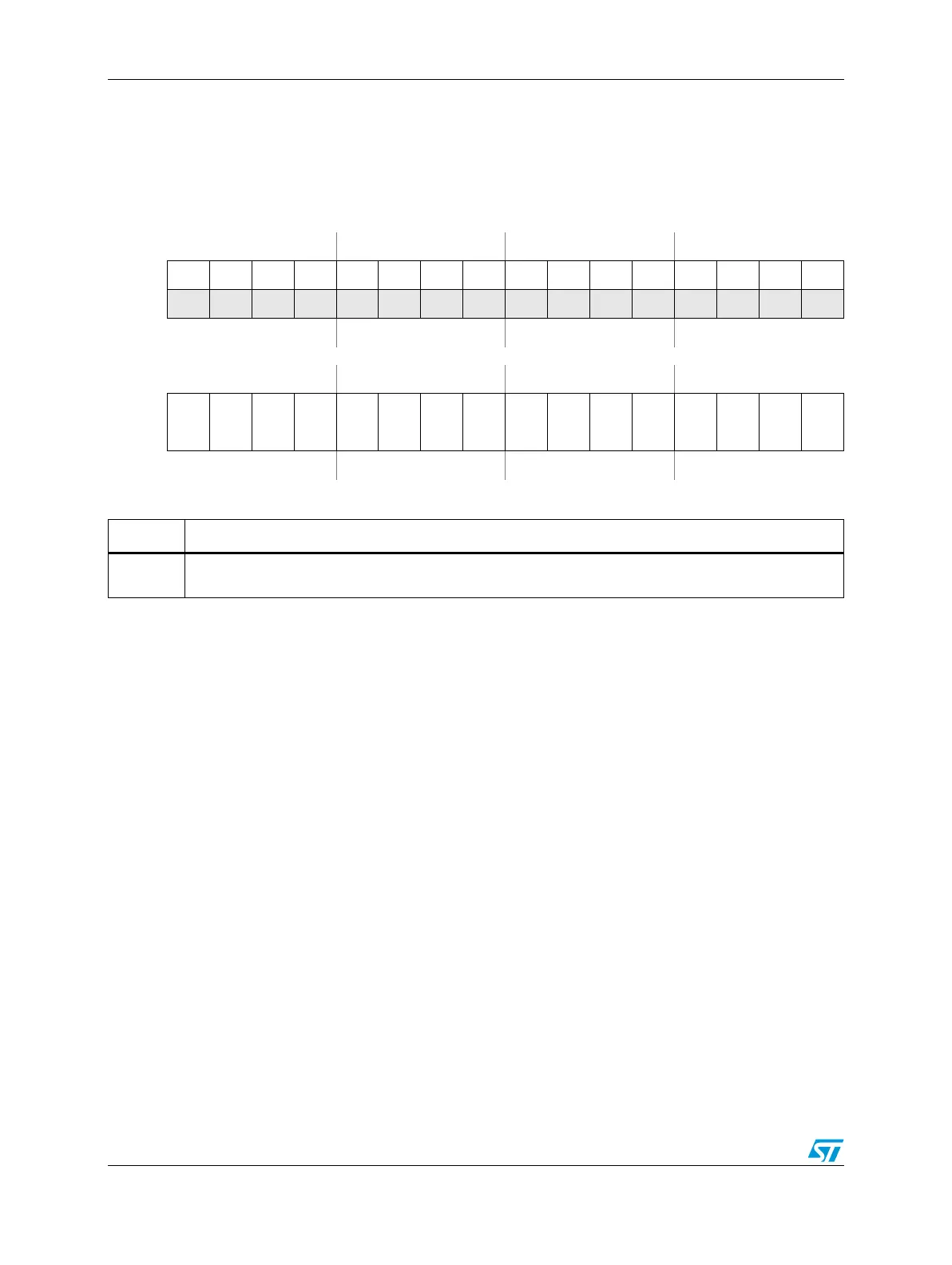

DMA Channel Select Register (DMAR[0])

DMAR0 = Enable bits for channel 0 to 15 (precision channels)

Figure 293. DMA Channel Select Register 0 (DMAR0)

Address:

Base + 0x0044 Access: User read/write

0123456789101112131415

R00000000 00000 000

W

Reset0000000000000000

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

DMA

15

DMA

14

DMA

13

DMA

12

DMA

11

DMA

10

DMA

9

DMA

8

DMA

7

DMA

6

DMA

5

DMA

4

DMA

3

DMA

2

DMA

1

DMA

0

W

Reset0000000000000000

Table 302. DMARx field descriptions

Field Description

DMAn

DMA enable

When set (DMAn = 1), channel n is enabled to transfer data in DMA mode.

Loading...

Loading...