RM0046 Flash Memory

Doc ID 16912 Rev 5 339/936

17.3.6 Registers description

The Flash user registers mapping is shown in Table 146. Except as noted, registers and

offsets are identical for the code Flash and data Flash blocks.

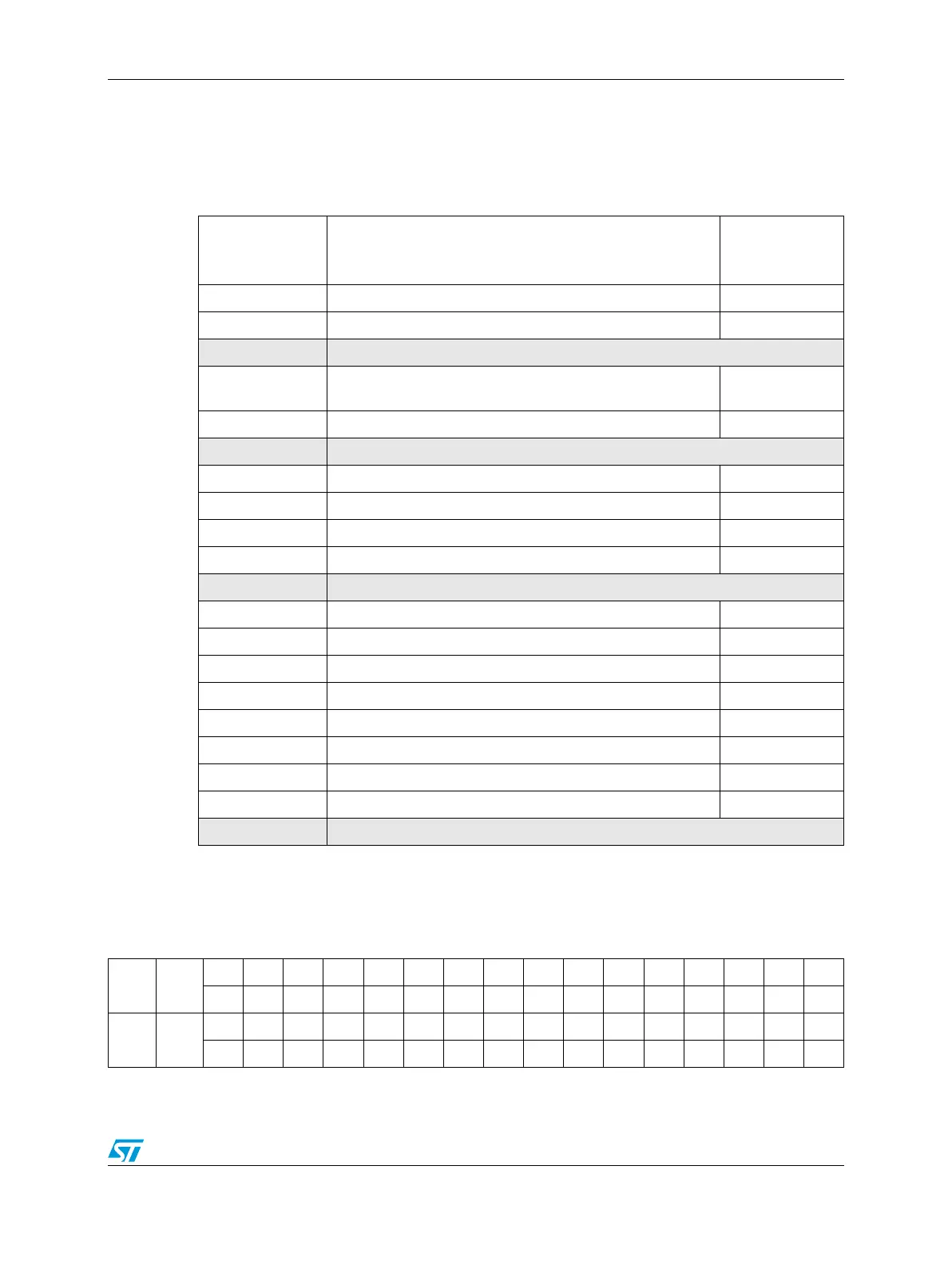

17.3.7 Register map

Table 146. Flash registers

Offset from

xxxx_BASE

(0xFFFE_C000)

Register Location

0x0000 on page 17-342

0x0004

Low/mid Address Space Block Locking Register (LML)

on page 17-346

0x0008 Reserved

0x000C

Secondary Low/mid Address Space Block Lock Register

(SLL)

on page 17-349

0x0010 Low/mid Address Space Block Select Register (LMS) on page 17-351

0x0014 Reserved

0x0018 Address Register (ADR) on page 17-352

0x001C Platform Flash Configuration Register 0 (PFCR0)

(1)

1. This register is not implemented on the data Flash block.

on page 17-353

0x0020 Platform Flash Configuration Register 1 (PFCR1)

(1)

on page 17-357

0x0024 Platform Flash Access Protection Register (PFAPR)

(1)

on page 17-359

0x0028 Reserved

0x003C User Test Register 0 (UT0) on page 17-360

0x0040 User Test Register 1 (UT1) on page 17-362

0x0044 User Test Register 2 (UT2)

(1)

on page 17-363

0x0048 User Multiple Input Signature Register 0 (UMISR0) on page 17-363

0x004C User Multiple Input Signature Register 1 (UMISR1) on page 17-364

0x0050 User Multiple Input Signature Register 2 (UMISR2)

(1)

on page 17-365

0x0054 User Multiple Input Signature Register 3 (UMISR3)

(1)

on page 17-365

0x0058 User Multiple Input Signature Register 4 (UMISR4)

(1)

on page 17-366

0x005C–0x3FFF

Reserved

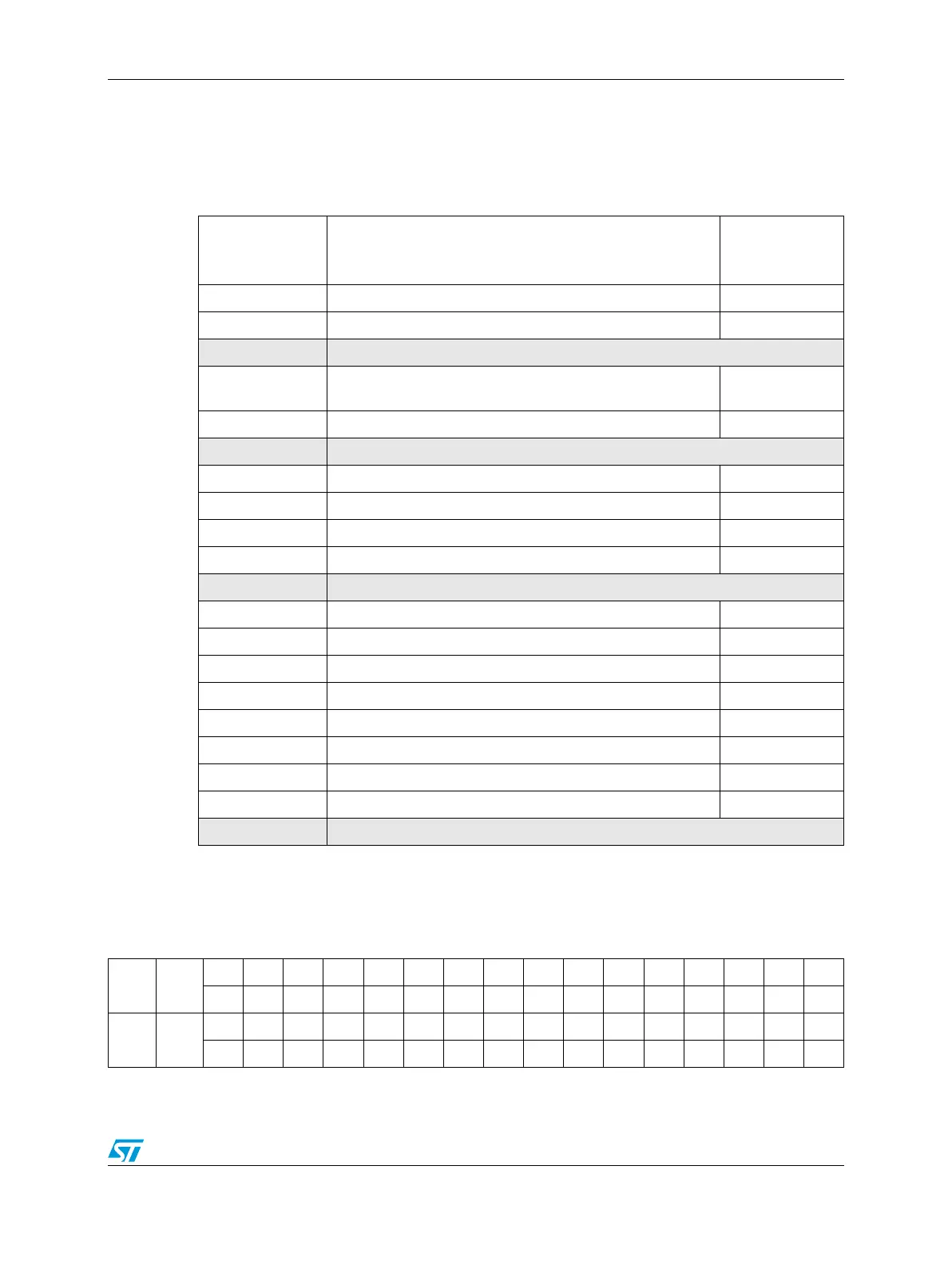

Table 147. Flash 256 KB bank0 register map

Address

offset

Register

name

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

0x00MCREDC0000SIZE2SIZE1SIZE00LAS2LAS1LAS0000MAS

EERRWE00PEASDONEPEG0000PGMPSUSERSESUSEHV

Loading...

Loading...