System Timer Module (STM) RM0046

792/936 Doc ID 16912 Rev 5

STM Count Register (STM_CNT)

The STM Count Register (STM_CNT) holds the timer count value.

Table 424. STM_CR field descriptions

Field Description

CPS[7:0]

Counter Prescaler

Selects the clock divide value for the prescaler (1 - 256).

0x00 Divide system clock by 1.

0x01 Divide system clock by 2.

...

0xFF Divide system clock by 256.

FRZ

Freeze

Allows the timer counter to be stopped when the device enters debug mode.

0 STM counter continues to run in debug mode.

1 STM counter is stopped in debug mode.

TEN

Timer Counter Enabled

0 Counter is disabled.

1 Counter is enabled.

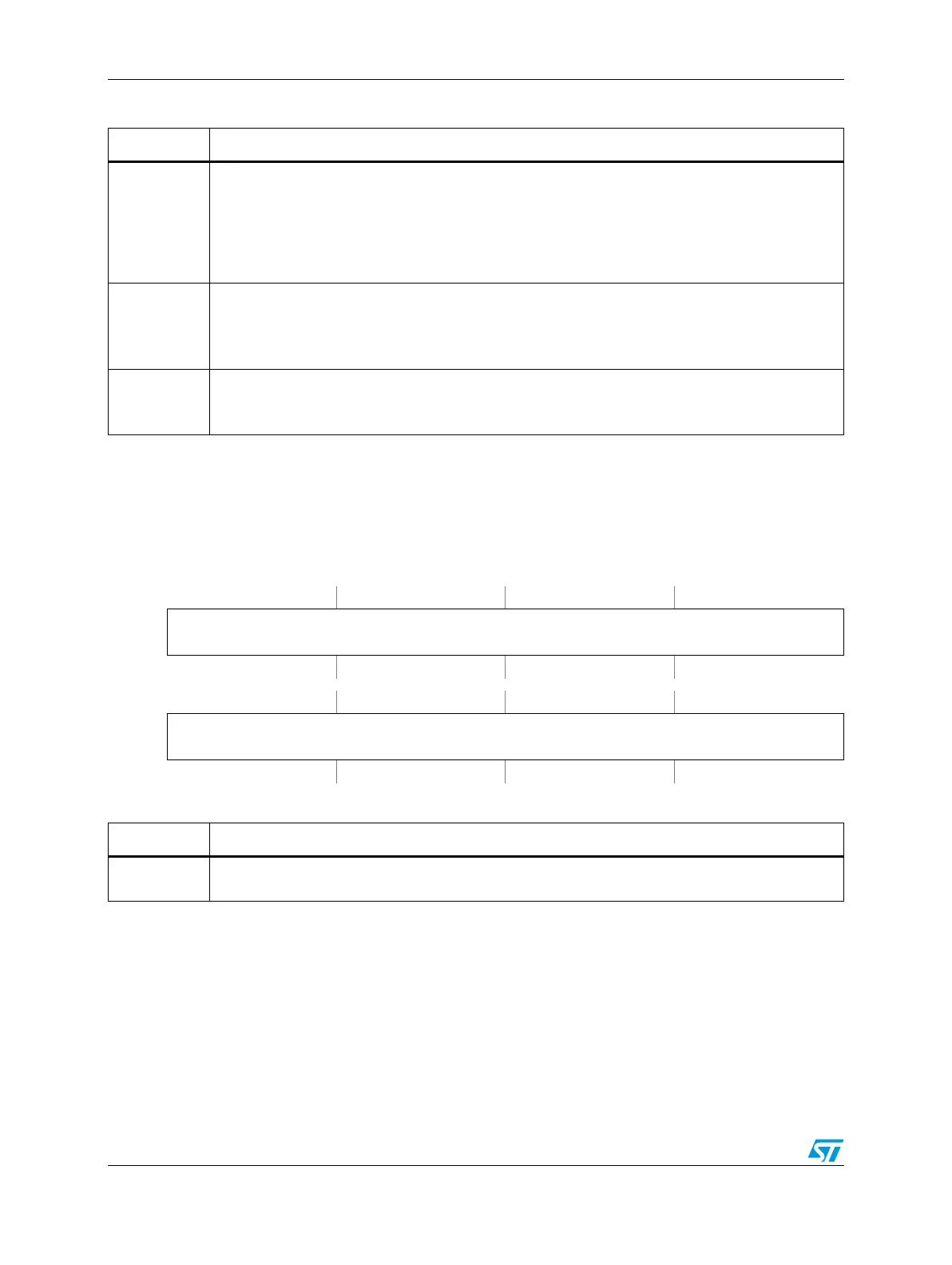

Figure 466. STM Count Register (STM_CNT)

Address:

Base + 0x0004 Access: User read/write

0123456789101112131415

R

CNT

W

Reset0000000000000000

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

CNT

W

Reset0000000000000000

Table 425. STM_CNT field descriptions

Field Description

CNT

Timer count value used as the time base for all channels. When enabled, the counter increments at

the rate of the system clock divided by the prescale value.

Loading...

Loading...