FlexCAN RM0046

552/936 Doc ID 16912 Rev 5

When the BCC bit is negated, RX15MASK is used as acceptance mask for the Identifier in

Message Buffer 15. When the FEN bit in the MCR is set (FIFO enabled), the RX15MASK

also applies to element 7 of the ID filter table. This register has the same structure as the Rx

Global Mask Register. It must be programmed while the module is in Freeze Mode, and

must not be modified when the module is transmitting or receiving frames.

Error Counter Register (ECR)

This register has two 8-bit fields that reflect the value of two FlexCAN error counters:

● Transmit Error Counter (Tx_Err_Counter field)

● Receive Error Counter (Rx_Err_Counter field)

The rules for increasing and decreasing these counters are described in the CAN protocol

and are completely implemented in the FlexCAN module. Both counters are read only

except in Test Mode or Freeze Mode, where they can be written by the CPU.

Writing to the Error Counter Register while in Freeze Mode is an indirect operation. The data

is first written to an auxiliary register and then an internal request/acknowledge procedure

across clock domains is executed. All this is transparent to the user, except for the fact that

the data will take some time to be actually written to the register. If desired, software can poll

the register to discover when the data was actually written.

FlexCAN responds to any bus state as described in the protocol, e.g., transmit ‘Error Active’

or ‘Error Passive’ flag, delay its transmission start time (‘Error Passive’) and avoid any

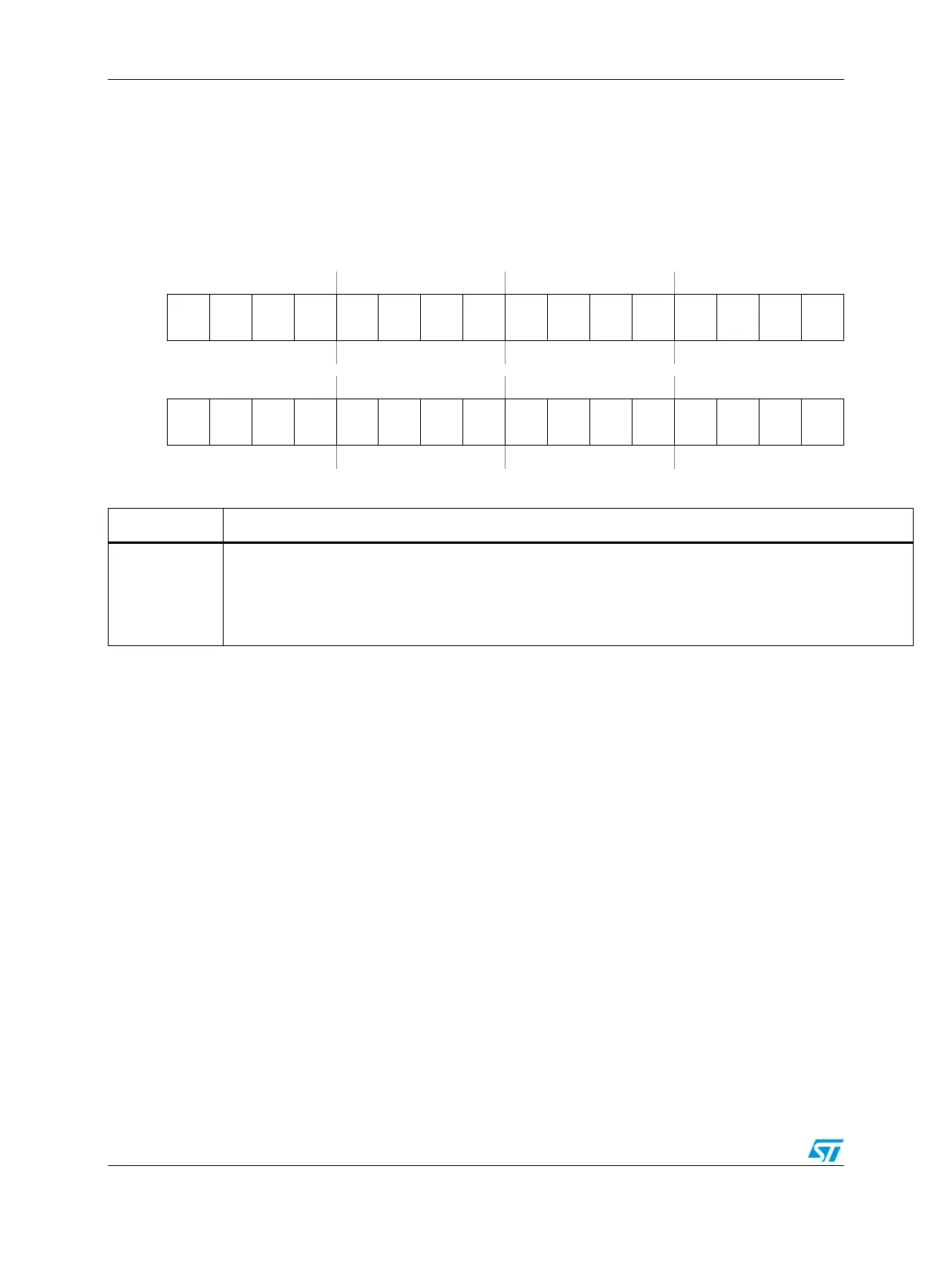

Figure 270. Rx Buffer 15 Mask register (RX15MASK)

Address:

Base + 0x0018 Access: User read/write

0123456789101112131415

R

MI31 MI30 MI29 MI28 MI27 MI26 MI25 MI24 MI23 MI22 MI21 MI20 MI19 MI18 MI17 MI16

W

Reset1111111111111111

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

MI15 MI14 MI13 MI12 MI11 MI10 MI9 MI8 MI7 MI6 MI5 MI4 MI3 MI2 MI1 MI0

W

Reset1111111111111111

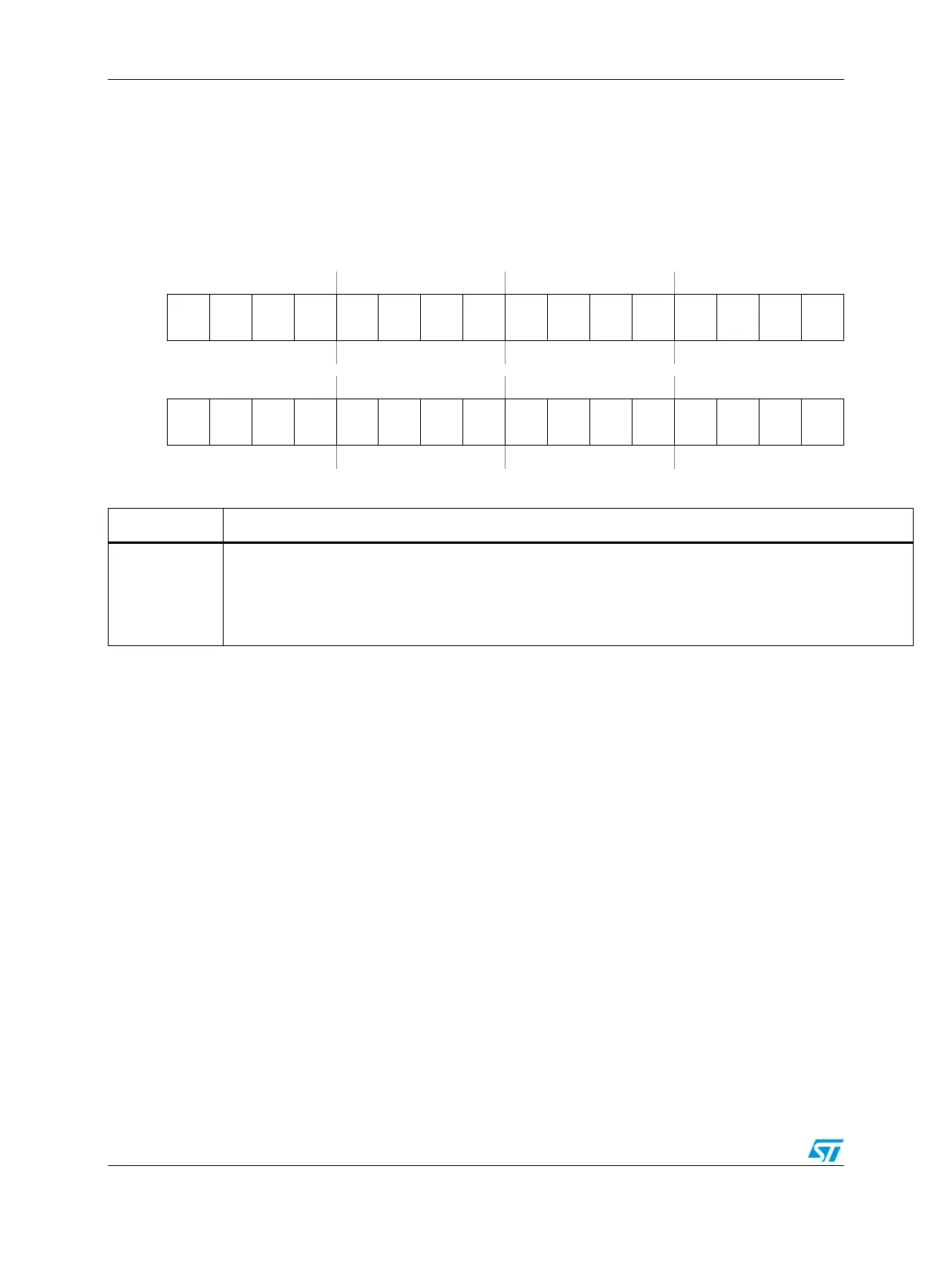

Table 279. RX15MASK field description

Field Description

0–31

MI31–MI0

Mask Bits

For normal Rx MBs, the mask bits affect the ID filter programmed on the MB. For the Rx FIFO, the mask bits

affect all bits programmed in the filter table (ID, IDE, RTR).

0 The corresponding bit in the filter is “don’t care.”

1 The corresponding bit in the filter is checked against the one received.

Loading...

Loading...