RM0046 Nexus Development Interface (NDI)

Doc ID 16912 Rev 5 899/936

Additionally, the DBCR0

EDM

bit is forced to ‘1’ internally while single-stepping to prevent

Debug events from generating Debug interrupts. Also, during a debug session, the DBSR is

frozen from updates due to debug events regardless of DBCR0

EDM

. They may still be

modified during a debug session via a single-stepped mtspr instruction if DBCRO

EDM

is

programmed to a ‘0’, or via OnCE access if DBCR0

EDM

is set.

e200z0h OnCE Control Register (OCR)

The e200z0h OnCE Control Register is a 32-bit register used to force the e200z0h core into

debug mode and to enable / disable sections of the e200z0h OnCE control logic. The

control bits are read/write. These bits are only effective while OnCE is enabled (jd_en_once

asserted). The OCR is shown in Figure 518.

Table 470 provides bit definitions for the OnCE Control Register.

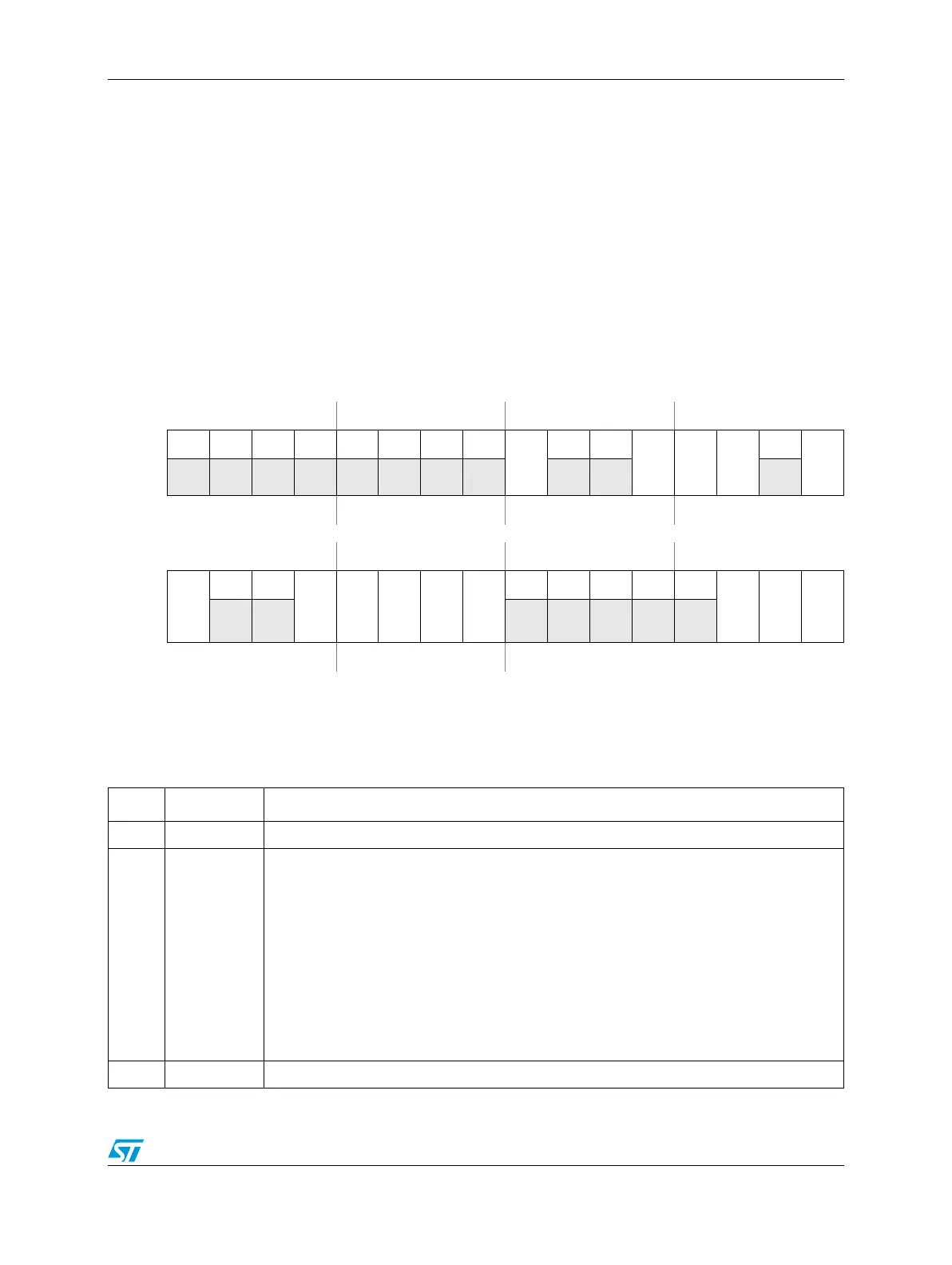

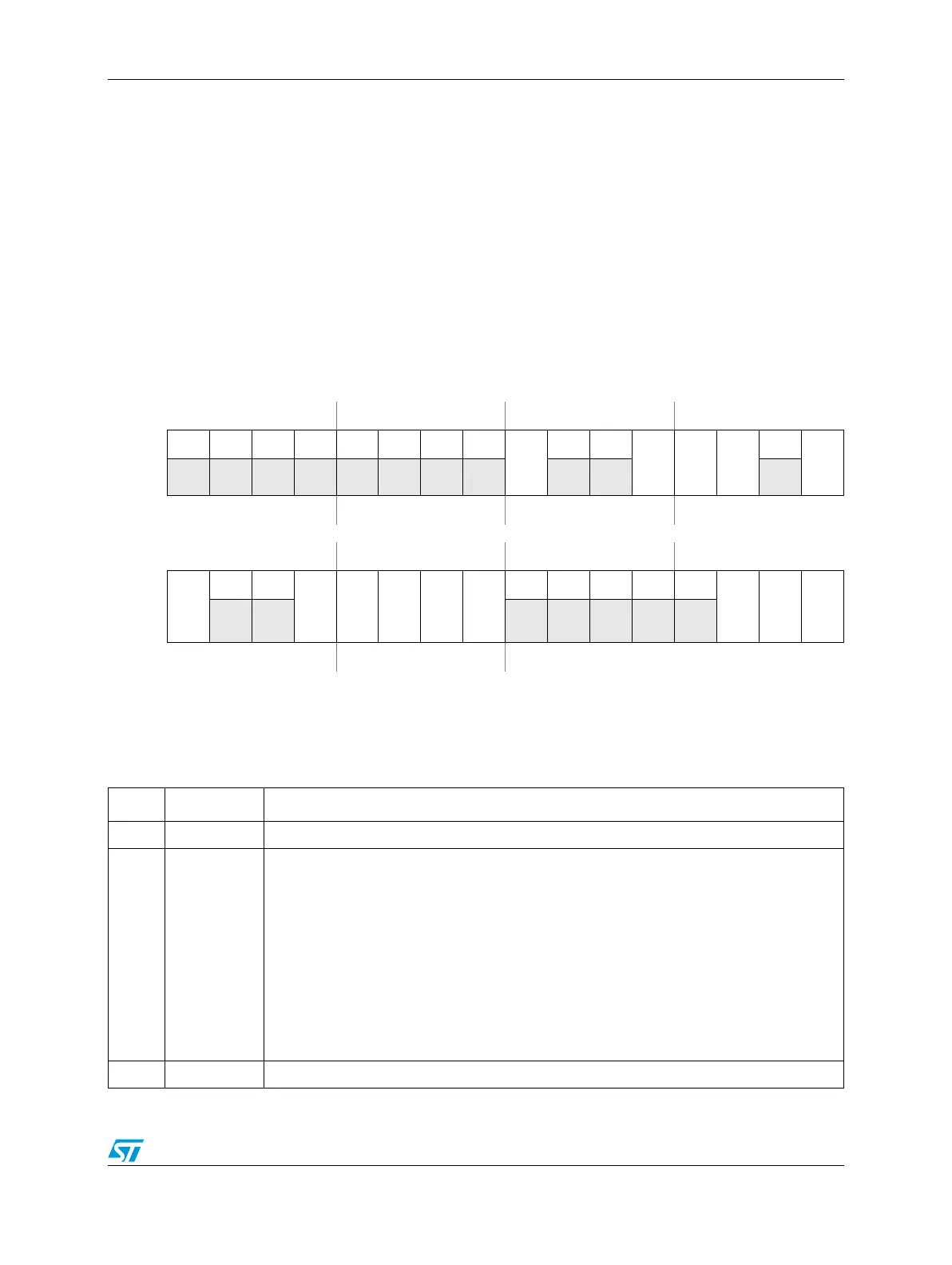

Figure 518. OnCE Control Register

0123456789101112131415

R00000000

I_DMDIS

00

I_DVLE

I_DI

I_DM

0

I_DE

W

Reset

(1)

0001000000000000

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

D_DMDIS

00

D_DW

D_DI

D_DM

D_DG

D_DE

00000

WKUP

FDB

DR

W

Reset0000000000000000

1. 0xo000_0000 on m_por, j_trst_b, or entering Test_logic_Reset state

Table 470. OnCE Control Register Bit Definitions

Bit(s) Name Description

0:7 — Reserved

8I_DMDIS

(1)

Instruction Side Debug MMU Disable Control Bit (I_DMDIS)

0 – MMU not disabled for debug sessions

1 – MMU disabled for debug sessions

This bit may be used to control whether the MMU is enabled normally, or whether the

MMU is disabled during a debug session for Instruction Accesses. When enabled, the

MMU functions normally. When disabled, for Instruction Accesses, no address translation

is performed (1:1 address mapping), and the TLB VLE, I,M, and E bits are taken from the

OCR bits I_VLE, I_DI, I_DM, and I_DE bits. The W and G bits are assumed ‘0’. The SX

and UX access permission control bits are set to‘1’ to allow full access. When disabled, no

TLB miss or TLB exceptions are generated for Instruction accesses. External access

errors can still occur.

9:10 — Reserved

Loading...

Loading...