Nexus Development Interface (NDI) RM0046

900/936 Doc ID 16912 Rev 5

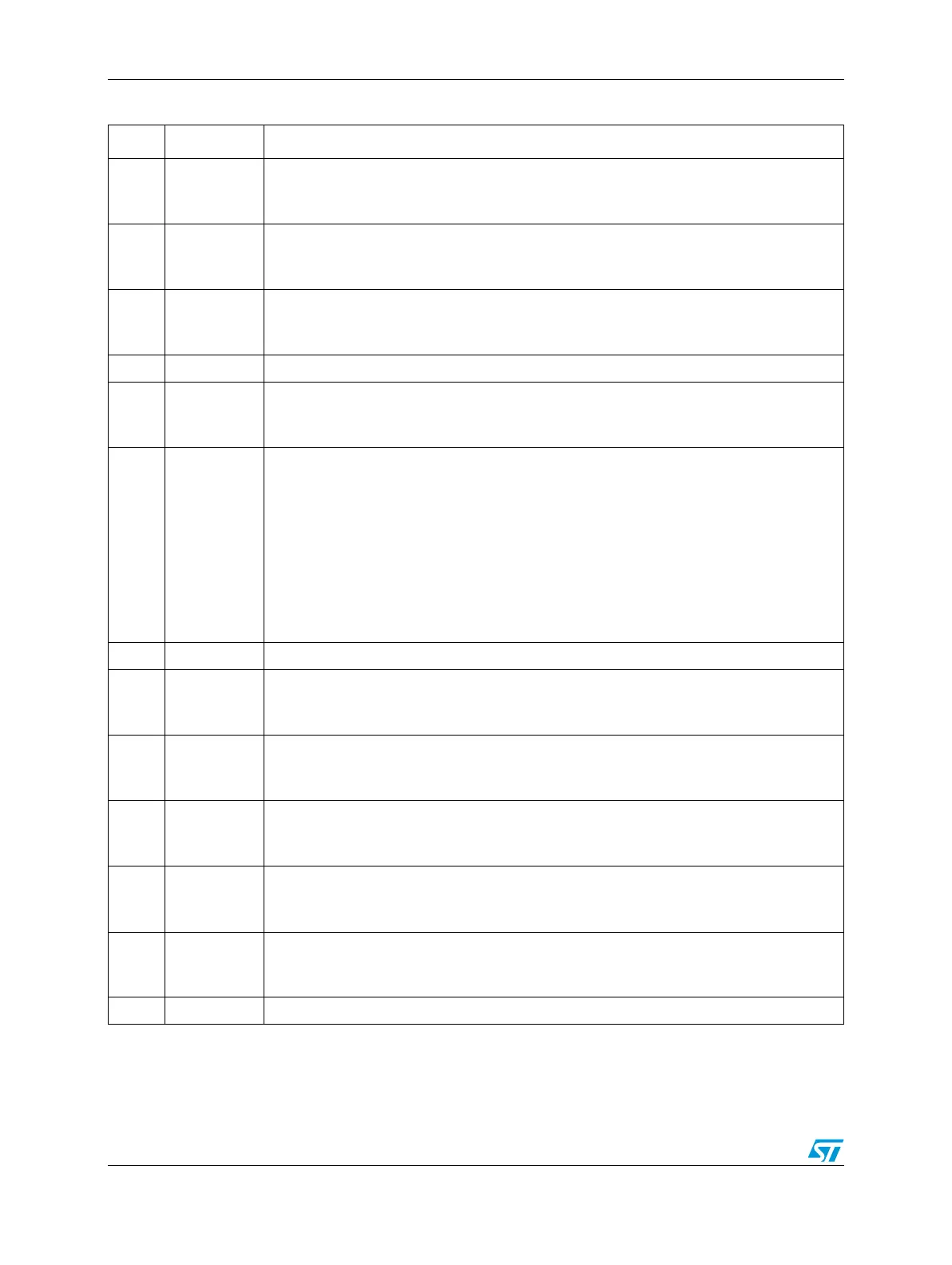

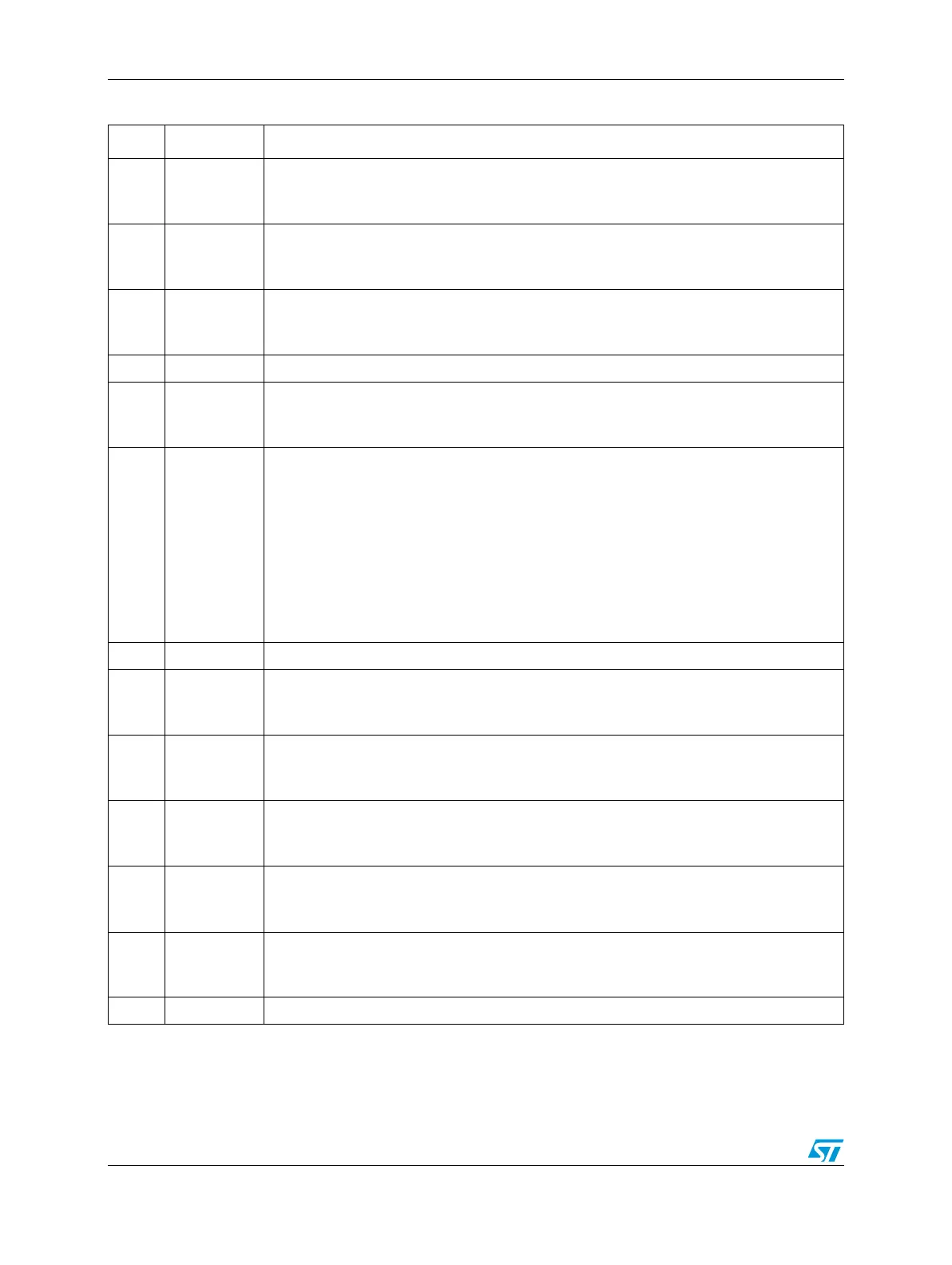

11 I_DVLE

(1)

Instruction Side Debug TLB ‘VLE’ Attribute Bit (I_DVLE)

This bit is used to provide the ‘VLE’ attribute bit to be used when the MMU is disabled

during a debug session.

12 I_DI

(1)

Instruction Side Debug TLB ‘I’ Attribute Bit (I_DI)

This bit is used to provide the ‘I’ attribute bit to be used for Instruction accesses when the

MMU is disabled for Instruction accesses during a debug session.

13 I_DM

(1)

Instruction Side Debug TLB ‘M’ Attribute Bit (I_DM)

This bit is used to provide the ‘M’ attribute bit to be used for Instruction accesses when the

MMU is disabled for Instruction accesses during a debug session.

14 — Reserved

15 I_DE

(1)

Instruction Side Debug TLB ‘E’ Attribute Bit (I_DE)

This bit is used to provide the ‘E’ attribute bit to be used for Instruction accesses when the

MMU is disabled for Instruction accesses during a debug session.

16 D_DMDIS

(1)

Data Side Debug MMU Disable Control Bit (D_DMDIS)

0 – MMU not disabled for debug sessions

1 – MMU disabled for debug sessions

This bit may be used to control whether the MMU is enabled normally, or whether the

MMU is disabled during a debug session for Data Accesses. When enabled, the MMU

functions normally. When disabled, for Data Accesses, no address translation is

performed (1:1 address mapping), and the TLB WIMGE bits are taken from the OCR bits

D_DW, D_DI, D_DM, D_DG, and D_DE bits. The SR, SW, UR, and UW access

permission control bits are set to‘1’ to allow full access. When disabled, no TLB miss or

TLB exceptions are generated for Data accesses. External access errors can still occur.

17:18 — Reserved

19 D_DW

(1)

Data Side Debug TLB ‘W’ Attribute Bit (D_DW)

This bit is used to provide the ‘W’ attribute bit to be used for Data accesses when the

MMU is disabled for Data accesses during a debug session.

20 D_DI

(1)

Data Side Debug TLB ‘I’ Attribute Bit (D_DI)

This bit is used to provide the ‘I’ attribute bit to be used for Data accesses when the MMU

is disabled for Data accesses during a debug session.

21 D_DM

(1)

Data Side Debug TLB ‘M’ Attribute Bit (D_DM)

This bit is used to provide the ‘M’ attribute bit to be used for Data accesses when the MMU

is disabled for Data accesses during a debug session.

22 D_DG

(1)

Data Side Debug TLB ‘G’ Attribute Bit (D_DG)

This bit is used to provide the ‘G’ attribute bit to be used for Data accesses when the MMU

is disabled for Data accesses during a debug session.

23 D_DE

(1)

Data Side Debug TLB ‘E’ Attribute Bit (D_DE)

This bit is used to provide the ‘E’ attribute bit to be used for Data accesses when the MMU

is disabled for Data accesses during a debug session.

24:28 — Reserved

Table 470. OnCE Control Register Bit Definitions (continued)

Bit(s) Name Description

Loading...

Loading...