System Status and Configuration Module (SSCM) RM0046

244/936 Doc ID 16912 Rev 5

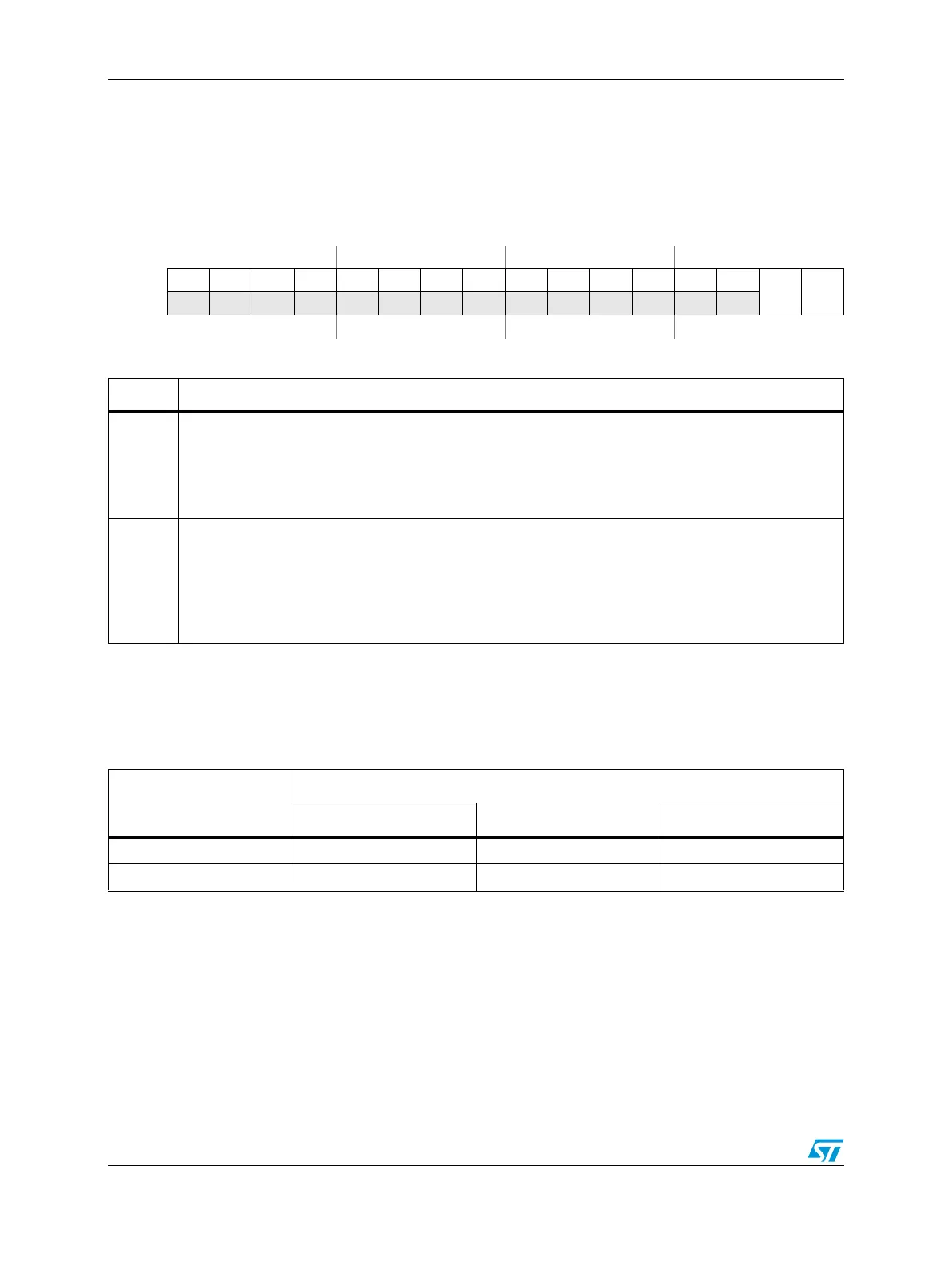

Error Configuration (ERROR) register

The Error Configuration register is a read-write register that controls the error handling of

the system.

Note: Transfers to Peripheral Bus resources may be aborted even before they reach the Peripheral

Bus (i.e., at the PRIDGE level). In this case, the PAE and RAE register bits will have no

effect on the abort.

Figure 92. Error Configuration (ERROR) register

Address:

Base + 0x0006 Access: User read/write

0123456789101112131415

R00000000000000

PA E R AE

W

Reset0000000000000000

Table 82. ERROR field descriptions

Field Description

PA E

Peripheral Bus Abort Enable

This bit enables bus aborts on any access to a peripheral slot that is not used on the device. This feature

is intended to aid in debugging when developing application code.

1: Illegal accesses to non-existing peripherals produce a Prefetch or Data Abort exception.

0: Illegal accesses to non-existing peripherals do not produce a Prefetch or Data Abort exception.

RAE

Register Bus Abort Enable

This bit enables bus aborts on illegal accesses to off-platform peripherals. Illegal accesses are defined

as reads or writes to reserved addresses within the address space for a particular peripheral. This

feature is intended to aid in debugging when developing application code.

1: Illegal accesses to peripherals produce a Prefetch or Data Abort exception.

0: Illegal accesses to peripherals do not produce a Prefetch or Data Abort exception.

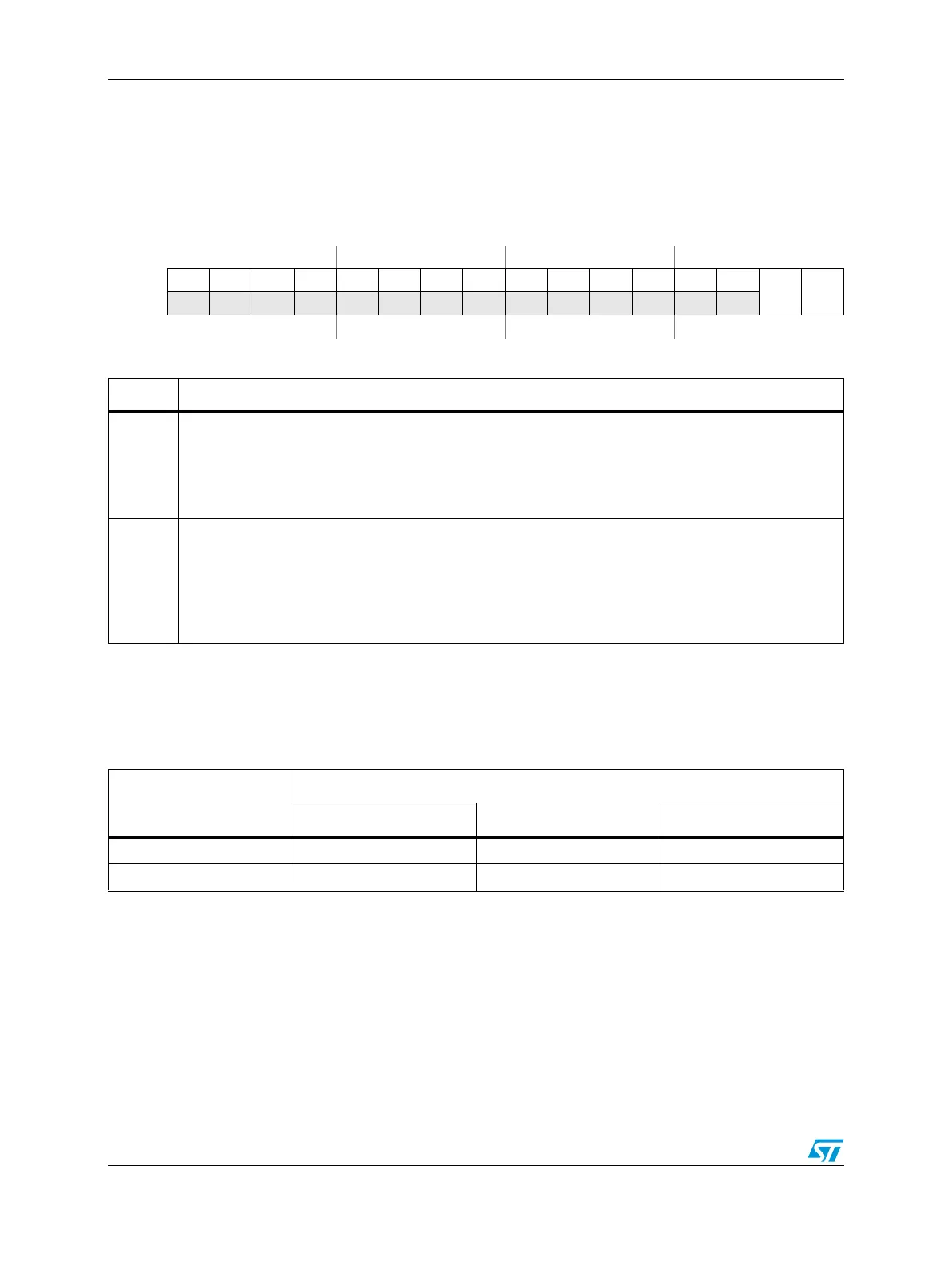

Table 83. ERROR allowed register accesses

Access type

Access width

8-bit 16-bit 32-bit

Read Allowed Allowed Allowed

Write Allowed Allowed Not allowed

Loading...

Loading...