Clock Description RM0046

114/936 Doc ID 16912 Rev 5

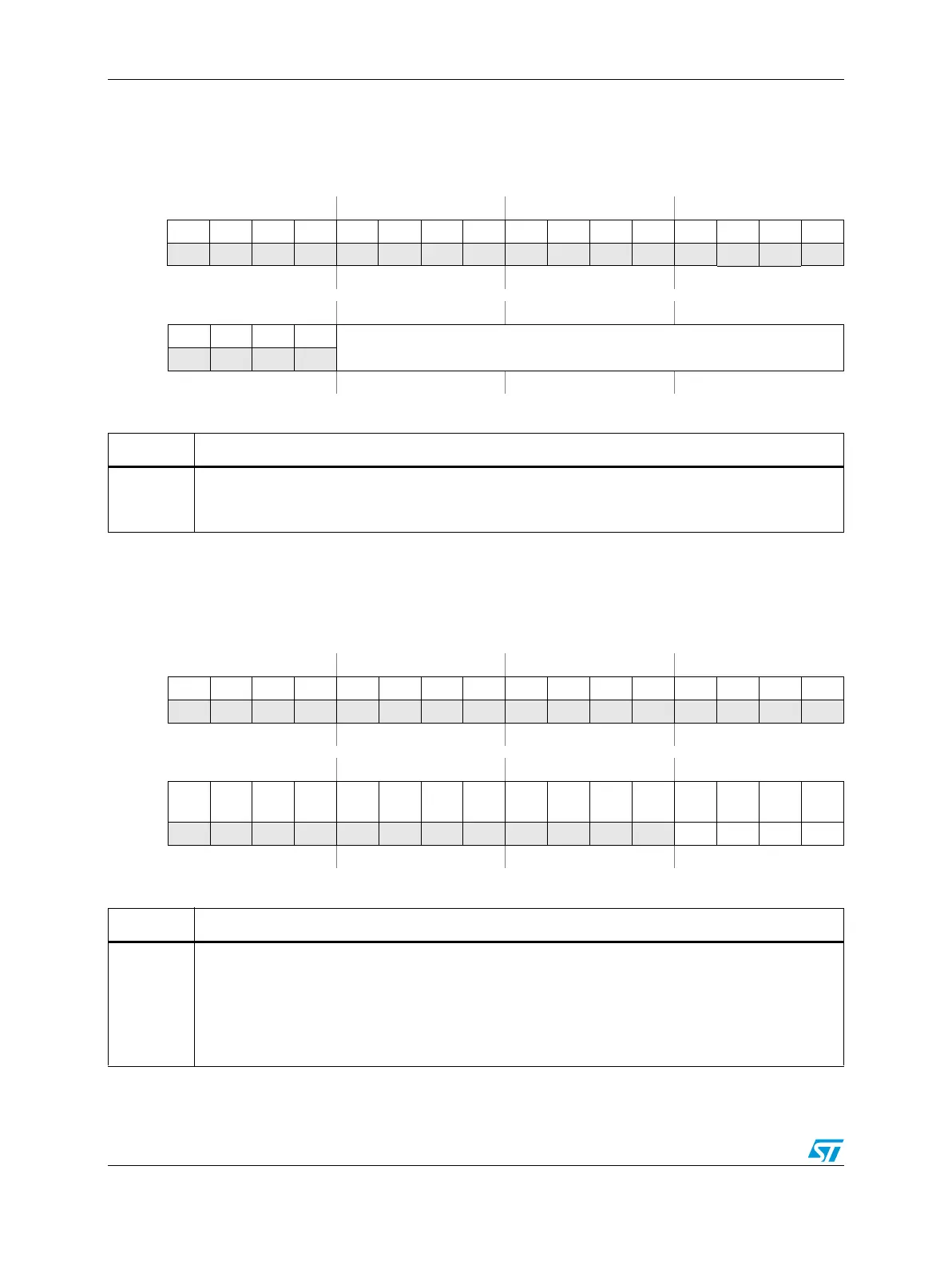

Low Frequency Reference Register FMPLL_0 (CMU_0_LFREFR_A)

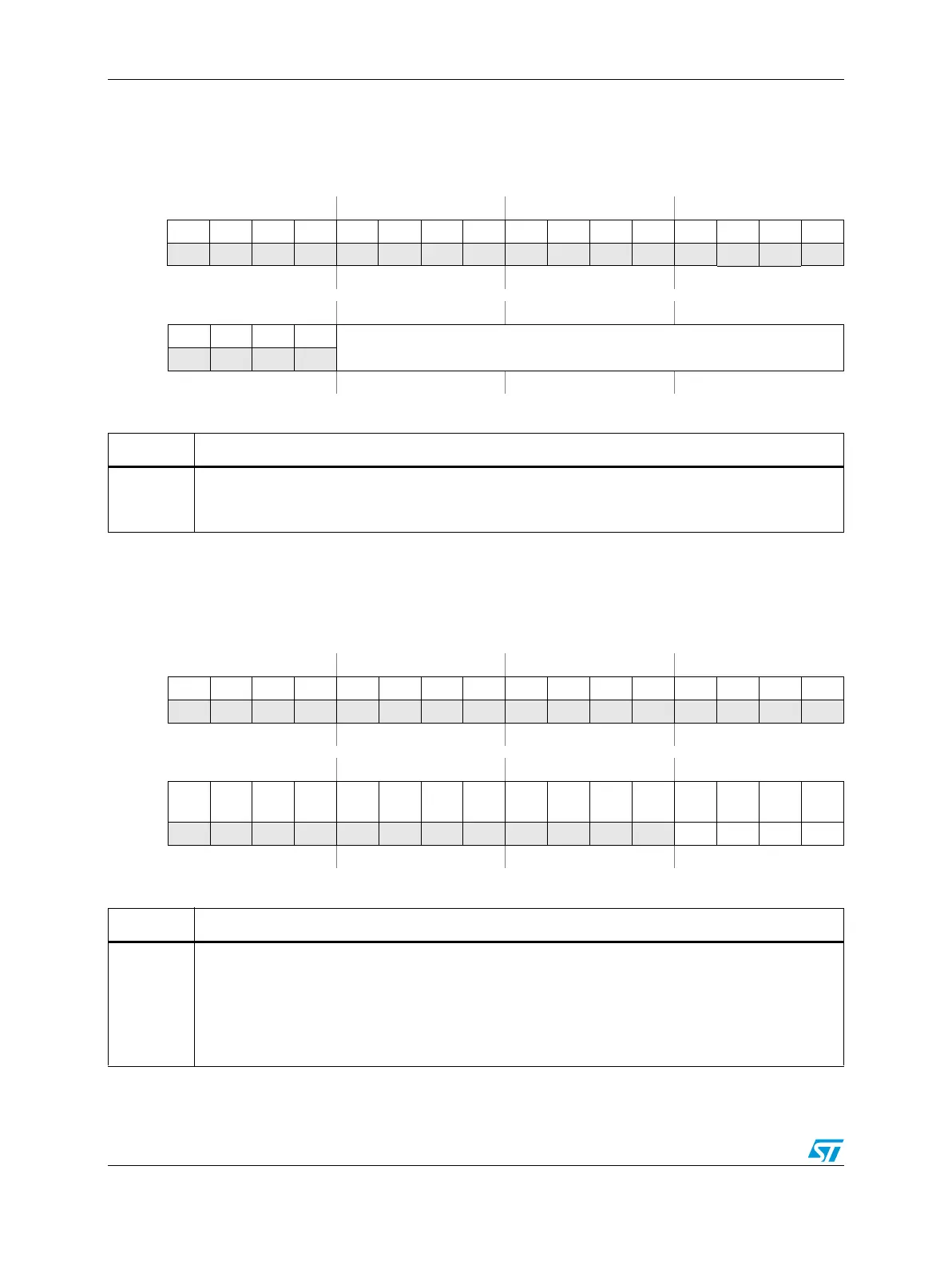

Interrupt Status Register (CMU_0_ISR)

Figure 23. Low Frequency Reference Register FMPLL_0 (CMU_0_LFREFR_A)

Address:

Base + 0x000C Access: User read/write

0123456789101112131415

R00000000 00000 000

W

Reset0000000000000000

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R0000

LFREF[11:0]

W

Reset0000000000000000

Table 21. CMU_0_LFREFR_A fields descriptions

Field Description

LFREF_A

Low Frequency reference value

These bits determine the low reference value for the FMPLL_0. The reference value is given by:

(LFREF_A[11:0]/16) * (f

RC

/4).

Figure 24. Interrupt Status Register (CMU_0_ISR)

Address:

Base + 0x0010 Access: User read/write

0123456789101112131415

R00000000 00000 000

W

Reset0000000000000000

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R00000000 0000

FLCI

_0

FHHI

_0

FLLI

_0

OLRI

W

w1c w1c w1c w1c

Reset0000000000000000

Table 22. CMU_0_ISR field descriptions

Field Description

FLCI_0

FMPLL_0 Clock frequency less than reference clock interrupt

This bit is set by hardware when CK_FMPLL_0 frequency becomes lower than reference clock

frequency (f

RC

/4) value and CK_FMPLL_0 is ‘ON’ and the PLL locked as signaled by the ME. It can

be cleared by software by writing 1.

0: No FLC event

1: FLC event pending

Loading...

Loading...