RM0046 Flash Memory

Doc ID 16912 Rev 5 357/936

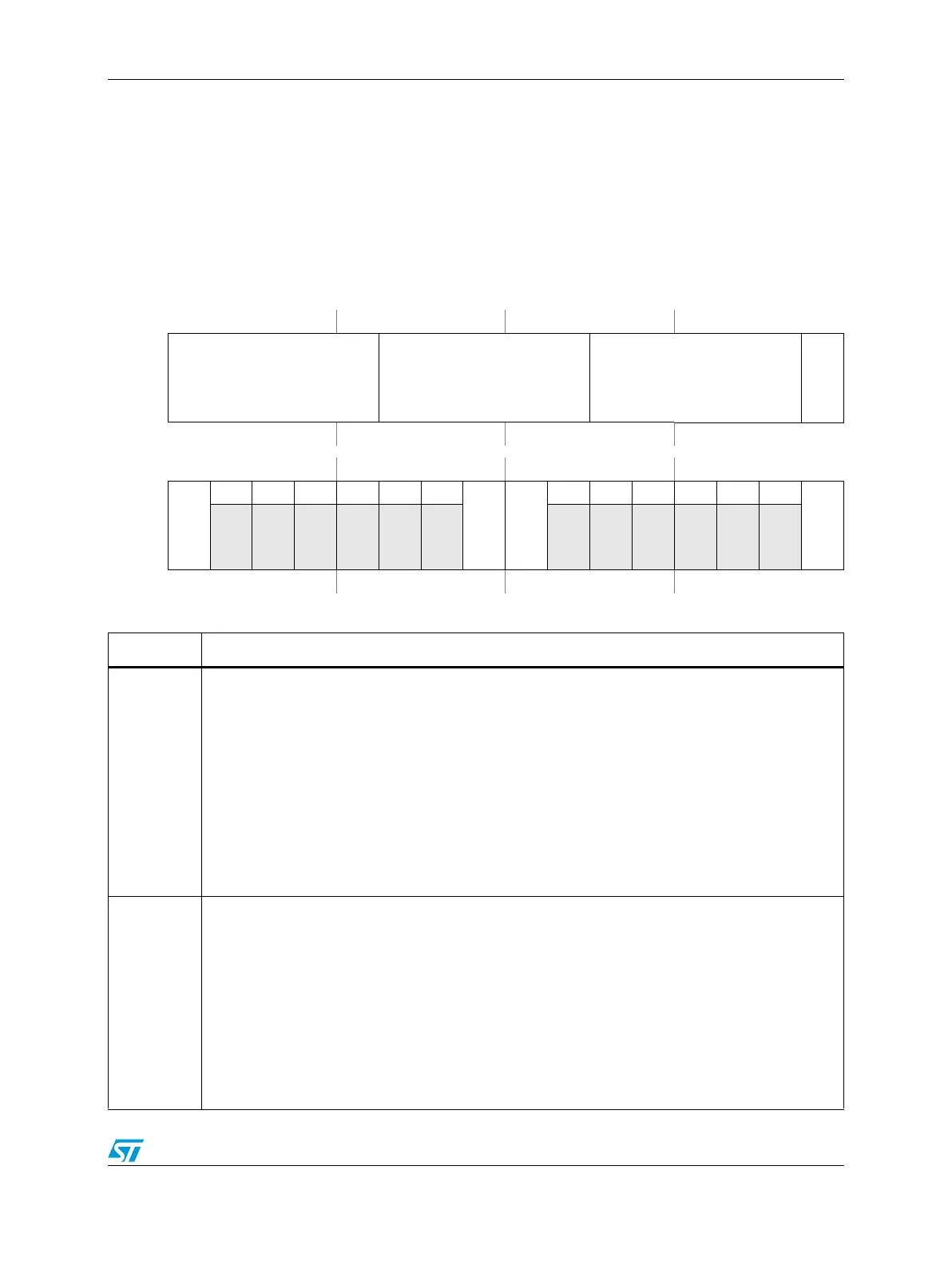

Platform Flash Configuration Register 1 (PFCR1)

The Platform Flash Configuration Register 1 (PFCR1) defines the configuration associated

with Flash memory bank1. This corresponds to the data Flash. The register is described in

Figure 161 and Table 1 5 7.

Note: This register is not implemented on the data Flash block.

Figure 161. Platform Flash Configuration Register 1 (PFCR1)

Address:

Base + 0x0020 Access: User read/write

0123456789101112131415

R

BK1_APC BK1_WWSC BK1_RWSC

BK1_RWWC

W

Reset0100001000010001

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

BK1_RWWC

000000

B1_P1_BFE

BK1_RWWC

000000

B1_P0_BFE

W

Reset1000000010000001

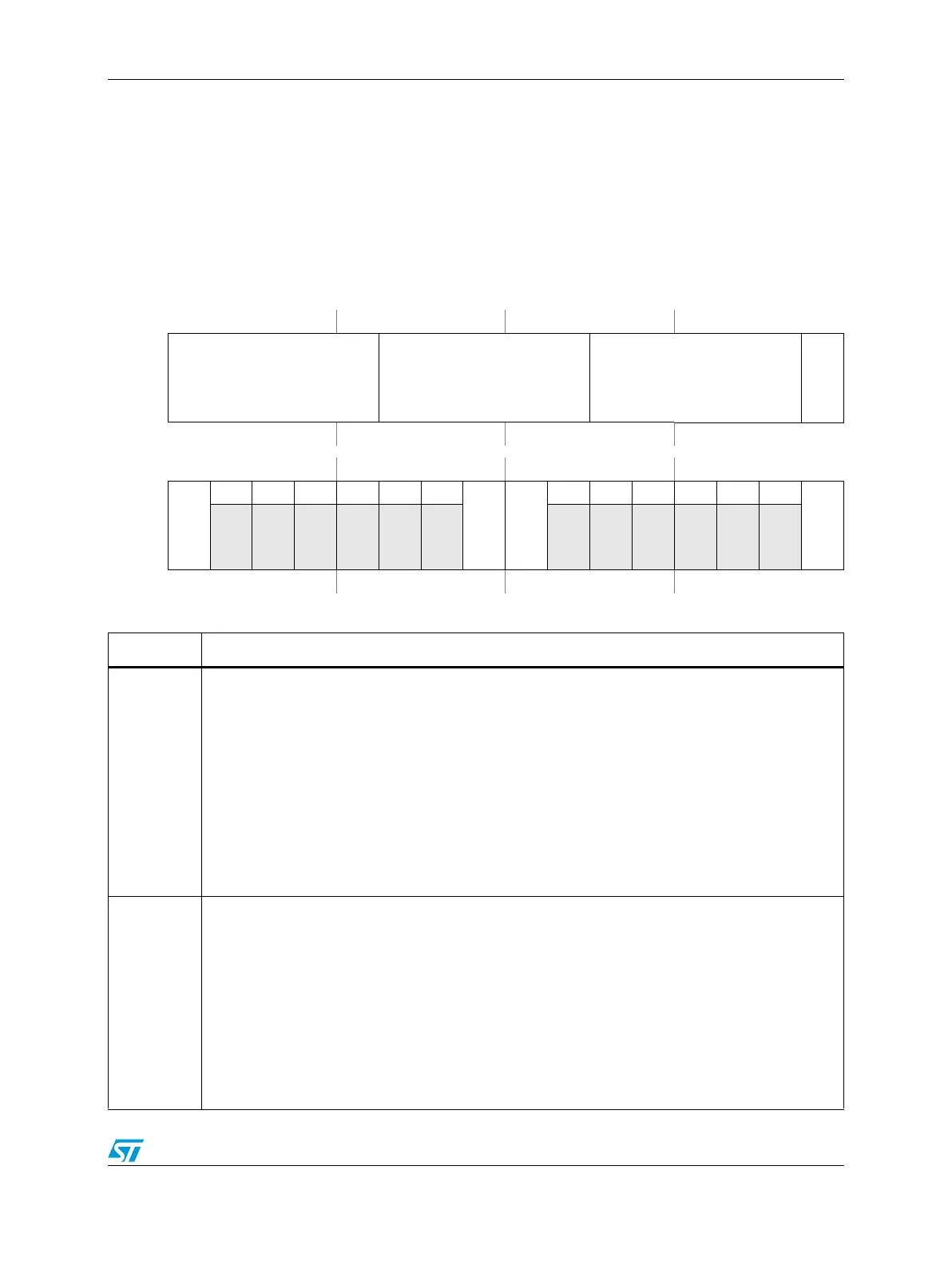

Table 157. PFCR1 field descriptions

Field Description

0-4

BK1_APC

Bank1 Address Pipelining Control

This field controls the number of cycles between Flash array access requests. This field must be set

to a value appropriate to the operating frequency of the PFlash. Higher operating frequencies

require non-zero settings for this field for proper Flash operation. This field is set to 0b00010 by

hardware reset.

00000 Accesses may be initiated on consecutive (back-to-back) cycles.

00001 Access requests require one additional hold cycle.

00010 Access requests require two additional hold cycles.

...

11110 Access requests require 30 additional hold cycles.

11111 Access requests require 31 additional hold cycles.

5-9

BK1_WWSC

Bank1 Write Wait State Control

This field controls the number of wait states to be added to the Flash array access time for writes.

This field must be set to a value appropriate to the operating frequency of the PFlash. Higher

operating frequencies require non-zero settings for this field for proper Flash operation. This field is

set to an appropriate value by hardware reset. This field is set to 0b00010 by hardware reset.

00000 No additional wait states are added.

00001 1 additional wait state is added.

00010 2 additional wait states are added.

...

111111 31 additional wait states are added.

Loading...

Loading...