Nexus Development Interface (NDI) RM0046

898/936 Doc ID 16912 Rev 5

The Once Decoder receives as input the 10-bit command from the OCMD, and status

signals from the processor, and generates all the strobes required for reading and writing

the selected OnCE registers.

Single stepping of instructions is performed by placing the CPU in debug mode, scanning in

appropriate information into the CPUSCR, and setting the Go bit (with the EX bit cleared)

with the RS field indicating either the CPUSCR or No Register Selected. After executing a

single instruction, the CPU will re-enter debug mode and await further commands. During

single-stepping, exception conditions may occur if not properly masked by debug firmware

(interrupts, machine checks, bus error conditions, etc.) and may prevent the desired

instruction from being successfully executed. The OSR

ERR

bit is set to indicate this

condition. In these cases, values in the CPUSCR will correspond to the first instruction of

the exception handler.

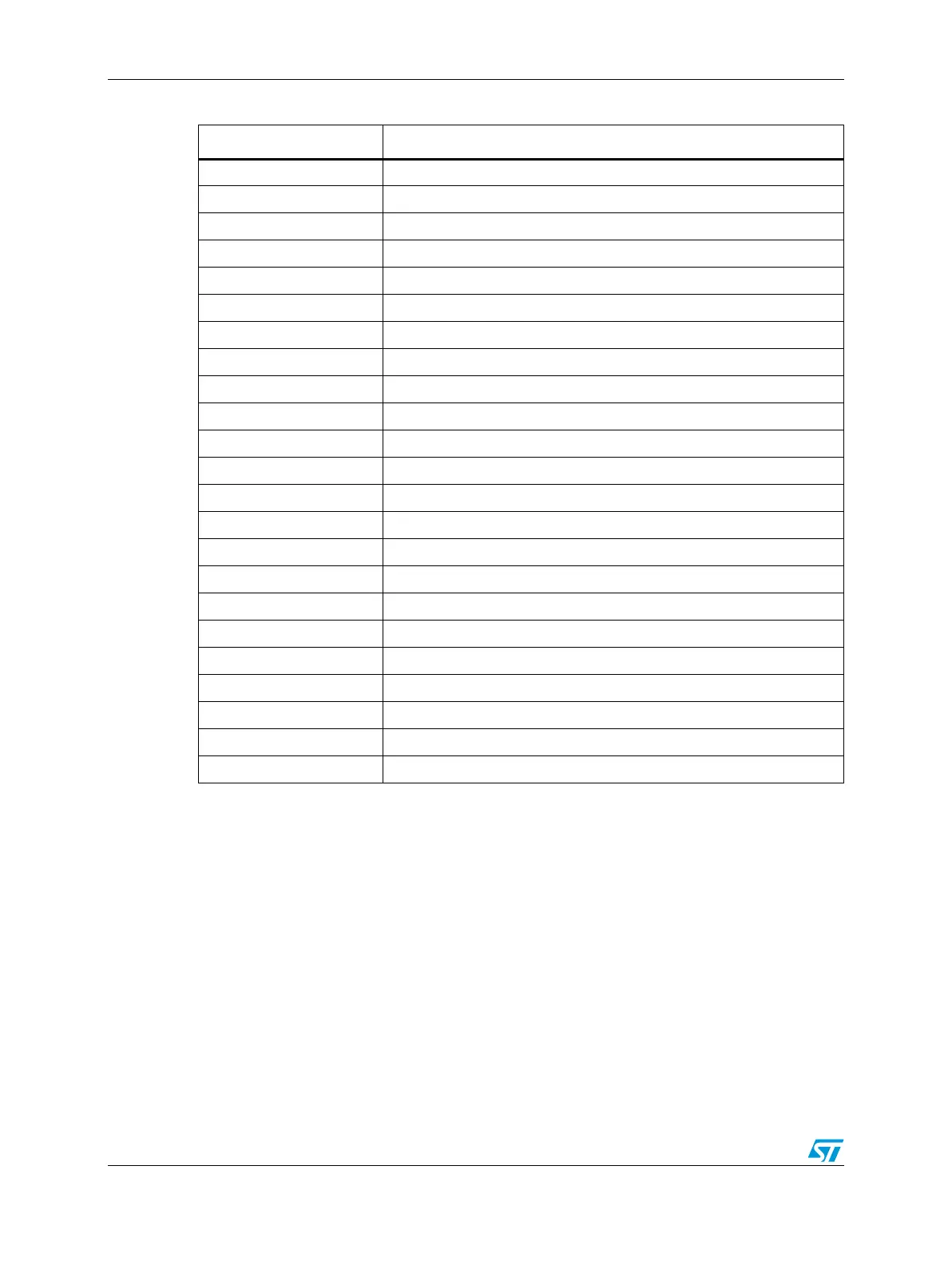

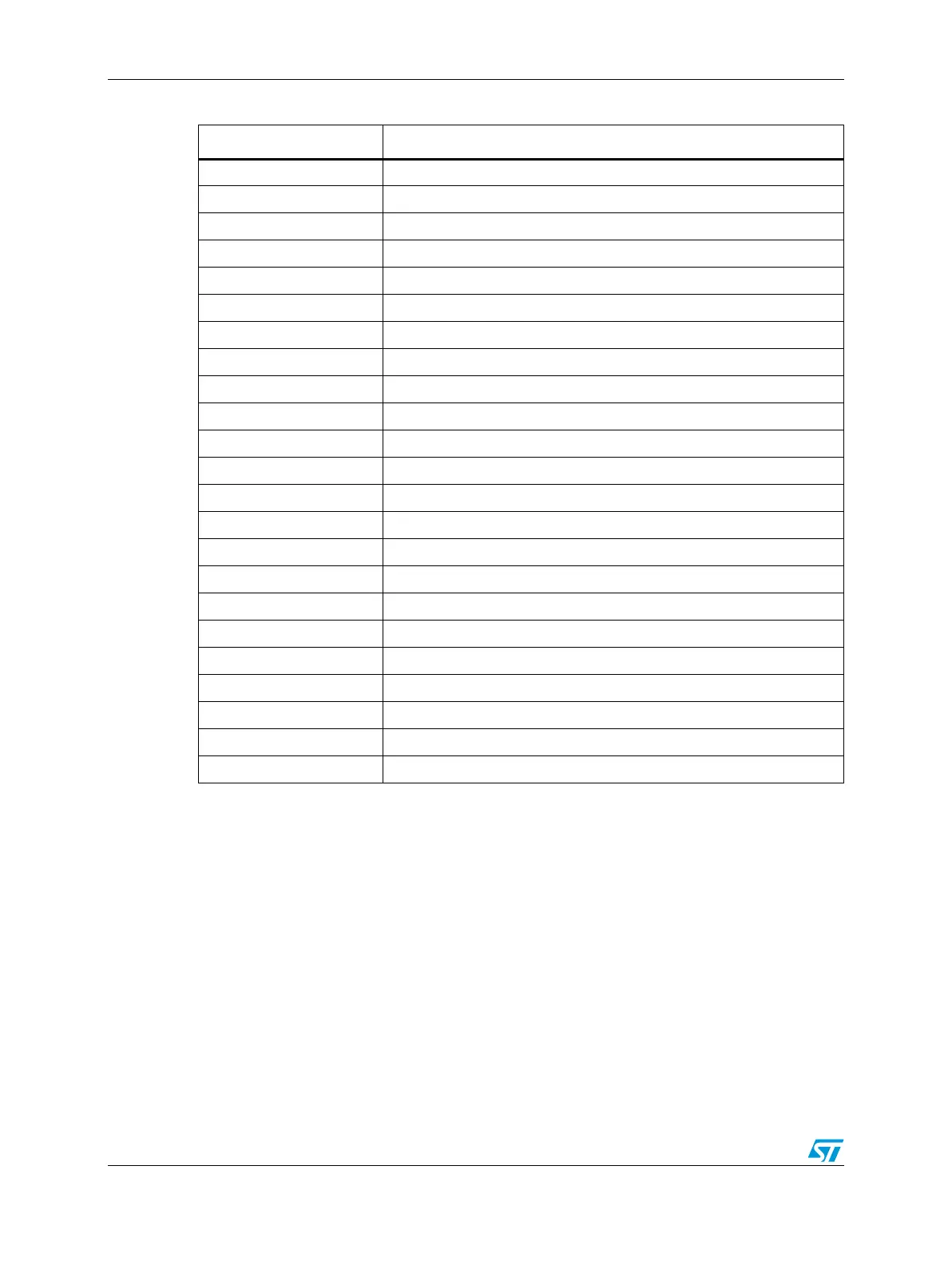

010 0111 Data Value Compare 2 (DVC2)

010 1000 – 010 1011 Reserved

010 1100 Reserved (DBCNT)

010 1101 – 010 1111 Reserved

011 0000 Debug Status Register (DBSR)

011 0001 Debug Control Register 0 (DBCR0)

011 0010 Debug Control Register 1 (DBCR1)

011 0011 Debug Control Register 2 (DBCR2)

011 0100 Reserved (DBCR3)

011 0101 Debug Control Register 4 (DBCR4)

011 0110 – 011 1110 Reserved (do not access)

011 1111 Debug External Resource Control (DBERC0)

100 0000 – 101 0111 Test Register Selects [0:23] (j_test_regsel{0:23])

101 1000 – 101 1111 Reserved (do not access)

110 0000 – 110 1110 Reserved (do not access)

110 1111 Shared Nexus Control Register Select

111 0000 – 111 1001 General Purpose register selects [0:9] (j_gp_regsel[0:9])

111 1010 (Reserved)

111 1011 (Reserved)

111 1100 (Reserved)

111 1101 (Reserved)

111 1110 Enable_OnCE

(1)

111 1111 Bypass

1. Causes assertion of the j_en_once_regsel output.

Table 469. e200z0h OnCE Register Addressing (continued)

RS[0:6] Register Selected

Loading...

Loading...