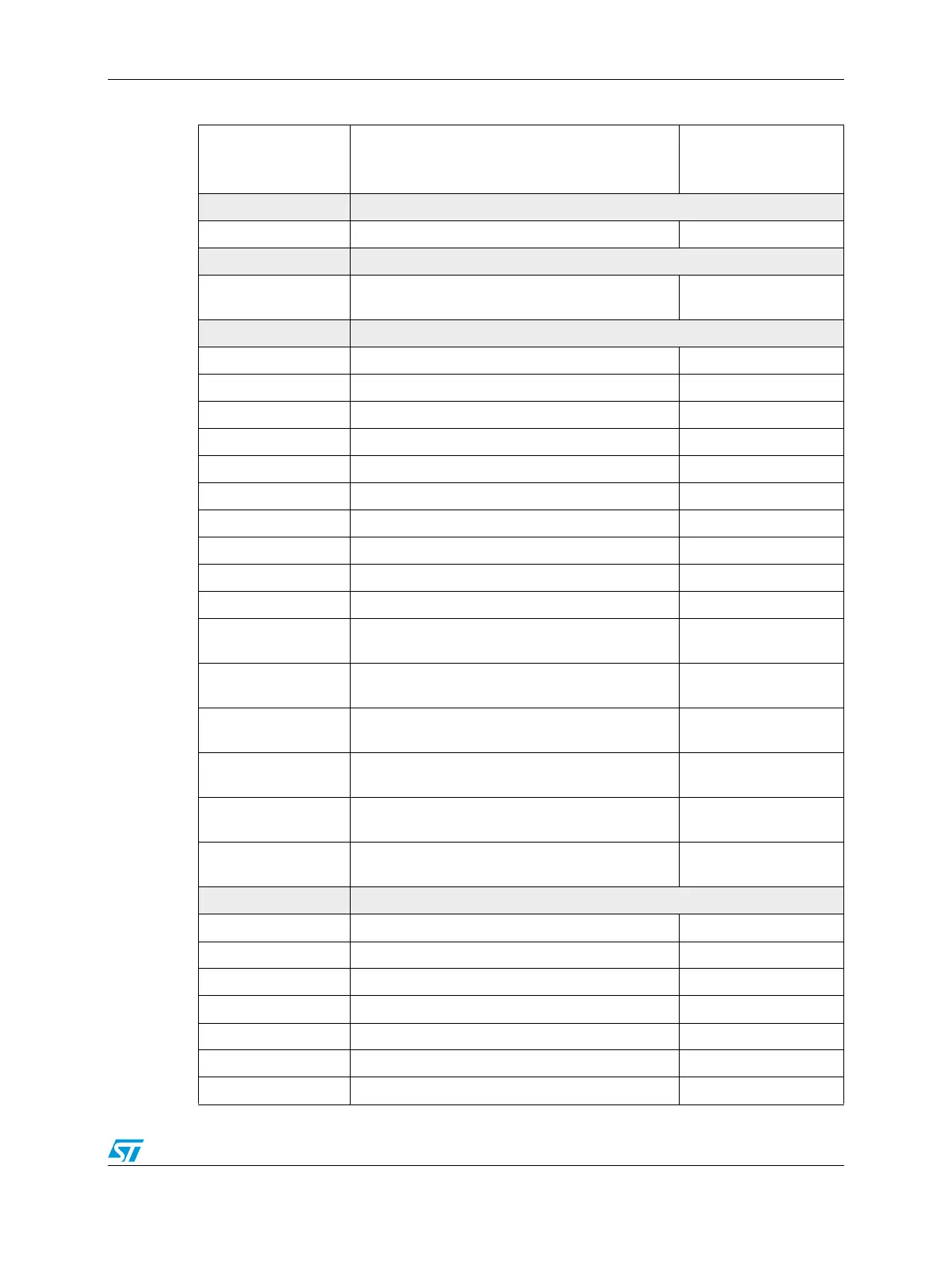

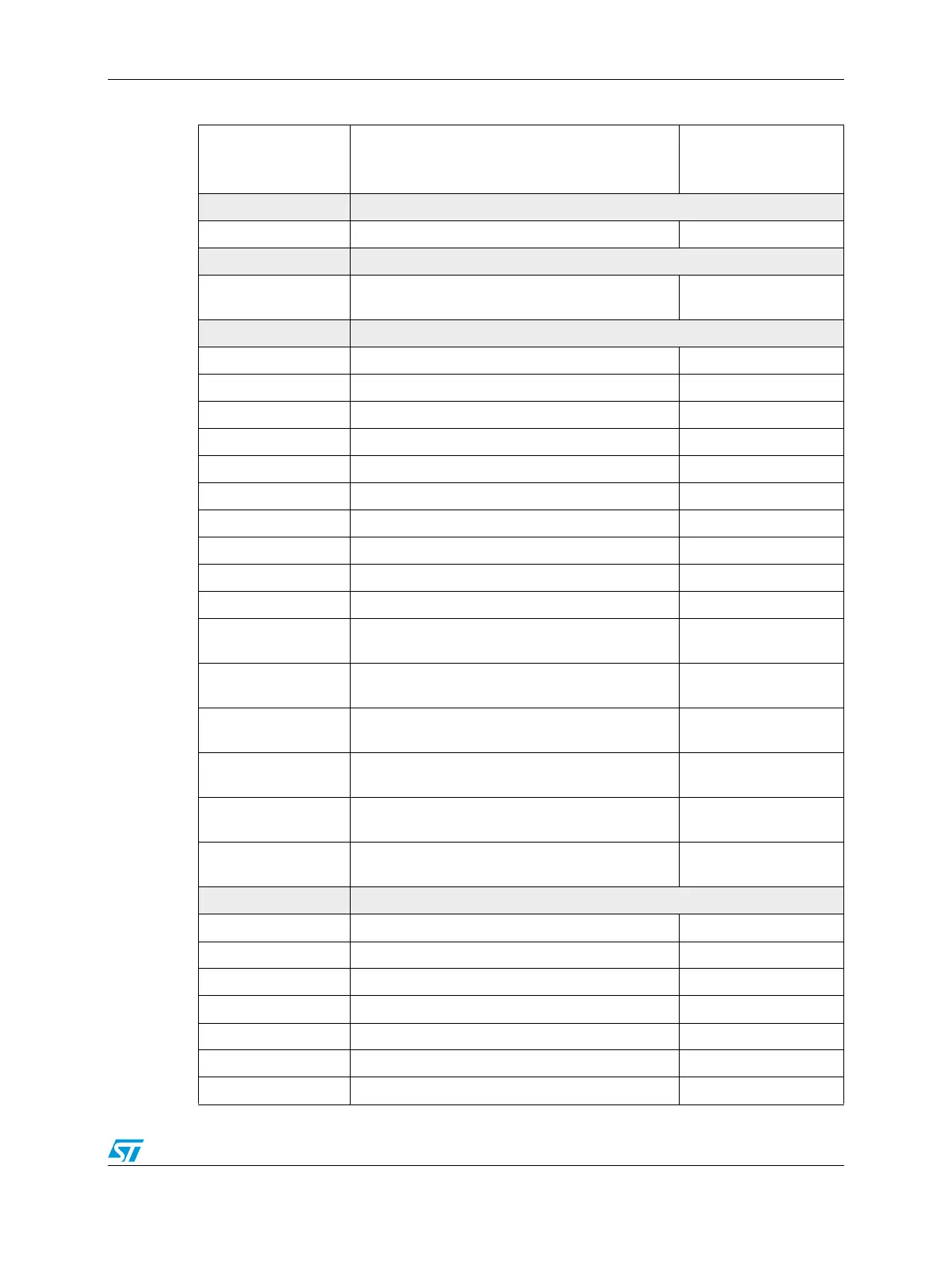

RM0046 Enhanced Direct Memory Access (eDMA)

Doc ID 16912 Rev 5 385/936

0x0028 Reserved

0x002C EDMA_ERL—eDMA Error Register on page 18-397

0x0030 Reserved

0x0034

EDMA_HRSL—eDMA Hardware Request Status

Register

on page 18-397

0x0038–0x00FF Reserved

0x0100 EDMA_CPR0—eDMA Channel 0 Priority Register on page 18-398

0x0101 EDMA_CPR1—eDMA Channel 1 Priority Register on page 18-398

0x0102 EDMA_CPR2—eDMA Channel 2 Priority Register on page 18-398

0x0103 EDMA_CPR3—eDMA Channel 3 Priority Register on page 18-398

0x0104 EDMA_CPR4—eDMA Channel 4 Priority Register on page 18-398

0x0105 EDMA_CPR5—eDMA Channel 5 Priority Register on page 18-398

0x0106 EDMA_CPR6—eDMA Channel 6 Priority Register on page 18-398

0x0107 EDMA_CPR7—eDMA Channel 7 Priority Register on page 18-398

0x0108 EDMA_CPR8—eDMA Channel 8 Priority Register on page 18-398

0x0109 EDMA_CPR9—eDMA Channel 9 Priority Register on page 18-398

0x010A

EDMA_CPR10—eDMA Channel 10 Priority

Register

on page 18-398

0x010B

EDMA_CPR11—eDMA Channel 11 Priority

Register

on page 18-398

0x010C

EDMA_CPR12—eDMA Channel 12 Priority

Register

on page 18-398

0x010D

EDMA_CPR13—eDMA Channel 13 Priority

Register

on page 18-398

0x010E

EDMA_CPR14—eDMA Channel 14 Priority

Register

on page 18-398

0x010F

EDMA_CPR15—eDMA Channel 15 Priority

Register

on page 18-398

0x0110–0x0FFF Reserved

0x1000 TCD00—Transfer Control Descriptor 0 on page 18-399

0x1020 TCD01—Transfer Control Descriptor 1 on page 18-399

0x1040 TCD02—Transfer Control Descriptor 2 on page 18-399

0x1060 TCD03—Transfer Control Descriptor 3 on page 18-399

0x1080 TCD04—Transfer Control Descriptor 4 on page 18-399

0x10A0 TCD05—Transfer Control Descriptor 5 on page 18-399

0x10C0 TCD06—Transfer Control Descriptor 6 on page 18-399

Table 175. eDMA memory map (continued)

Offset from

EDMA_BASE

(0xFFF4_4000)

Register Location

Loading...

Loading...