Enhanced Direct Memory Access (eDMA) RM0046

404/936 Doc ID 16912 Rev 5

224

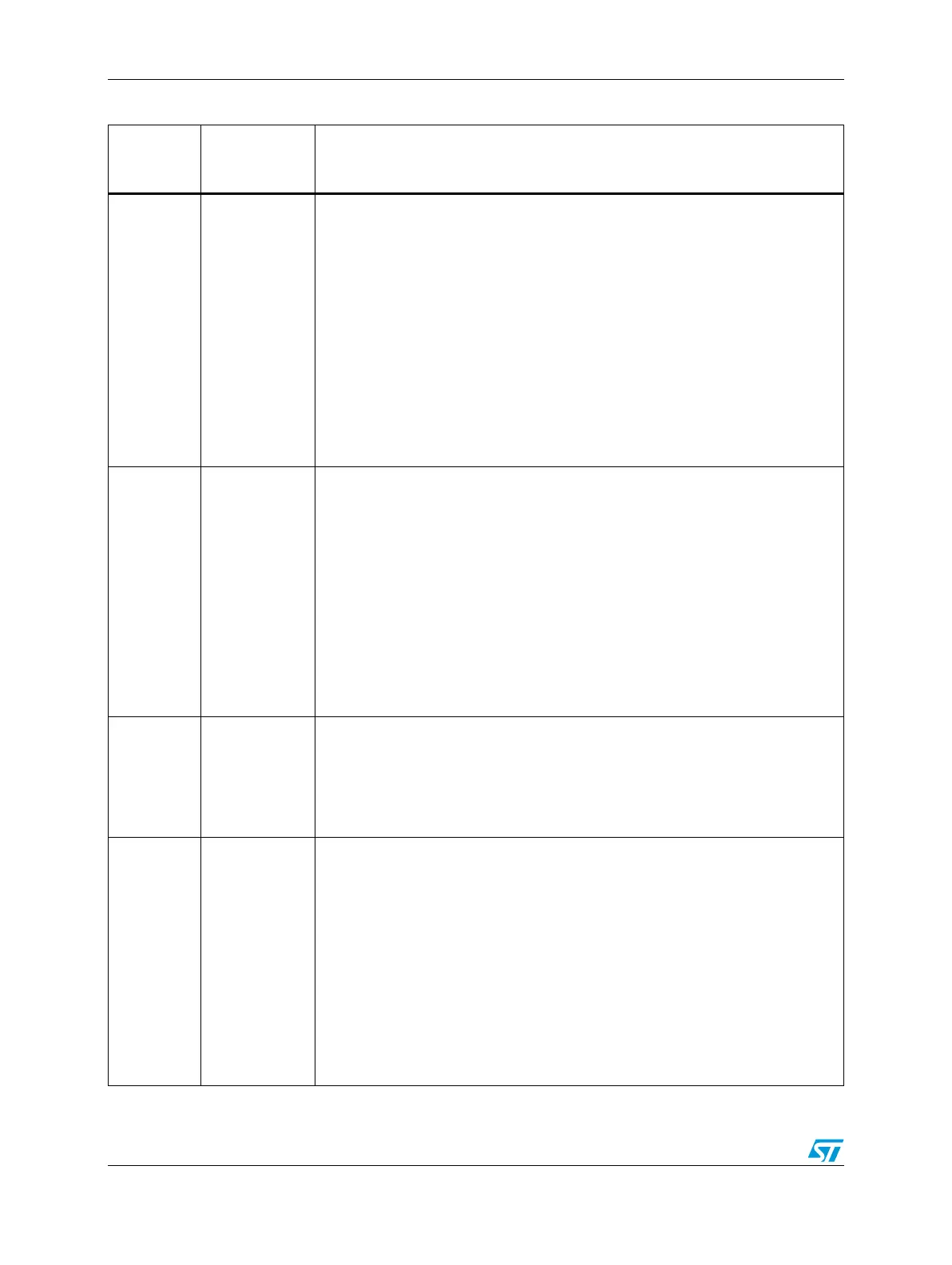

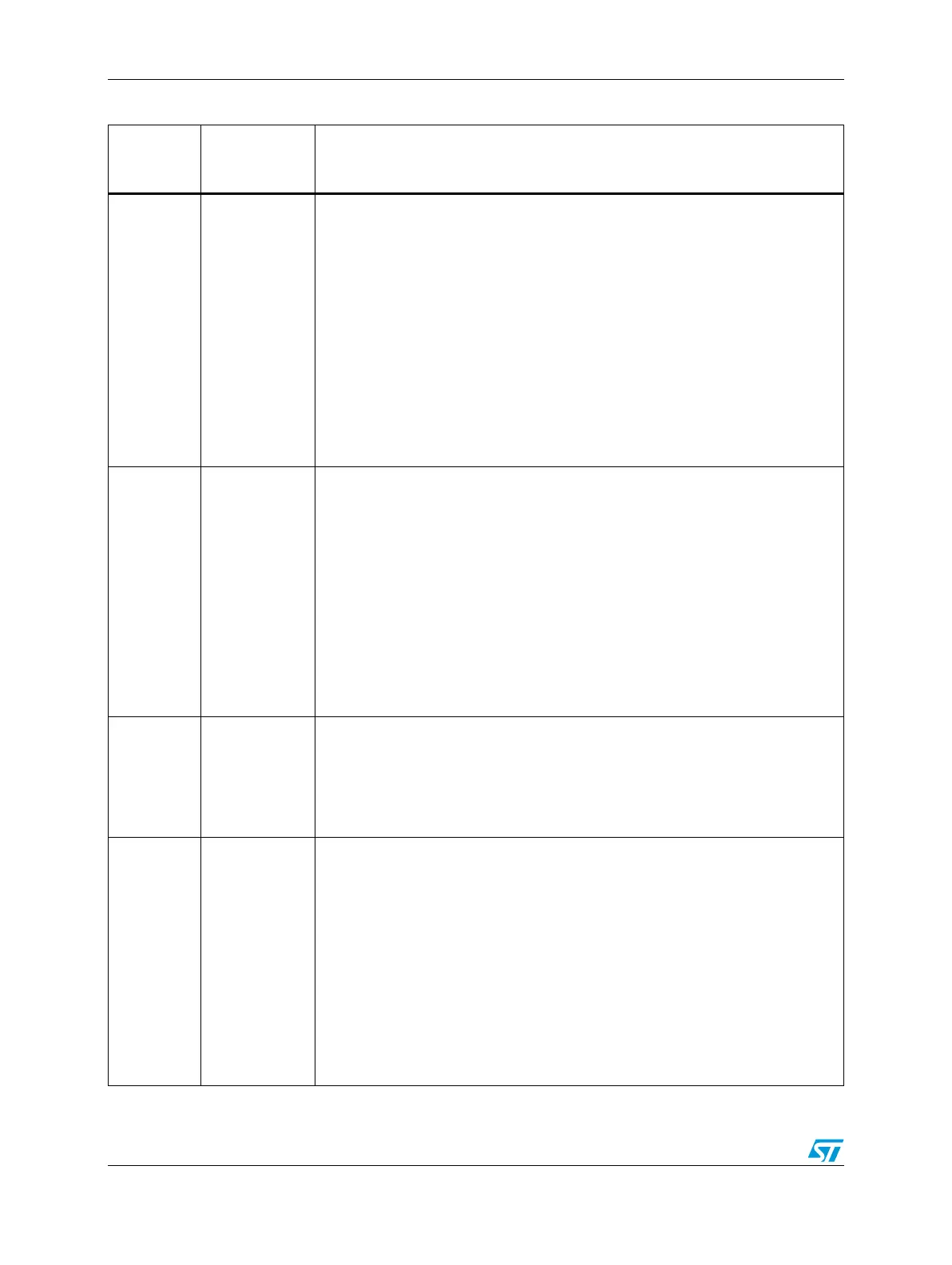

0x1C [0]

BITER.E_LINK

Enables channel-to-channel linking on minor loop complete. As the channel

completes the inner minor loop, this flag enables the linking to another channel,

defined by BITER.LINKCH[0:5]. The link target channel initiates a channel service

request via an internal mechanism that sets the TCD.START bit of the specified

channel. If channel linking is disabled, the BITER value is extended to 15 bits in

place of a link channel number. If the major loop is exhausted, this link mechanism

is suppressed in favor of the MAJOR.E_LINK channel linking.

0 The channel-to-channel linking is disabled.

1 The channel-to-channel linking is enabled.

When the TCD is first loaded by software, this field must be set equal to the

corresponding CITER field, otherwise a configuration error is reported. As the major

iteration count is exhausted, the contents of this field is reloaded into the CITER

field.

225–230

0x1C [1:6]

BITER

[0:5]

or

BITER.LINKCH

[0:5]

Beginning or starting “major” iteration count or link channel number.

If channel-to-channel linking is disabled (TCD.BITER.E_LINK = 0), then

– No channel-to-channel linking (or chaining) is performed after the inner minor

loop is exhausted. TCD bits [225:239] form a 15-bit BITER field.

Otherwise

– After the minor loop is exhausted, the eDMA engine initiates a channel service

request at the channel, defined by BITER.LINKCH[0:5], by setting that channel’s

TCD.START bit.

When the TCD is first loaded by software, this field must be set equal to the

corresponding CITER field, otherwise a configuration error is reported. As the major

iteration count is exhausted, the contents of this field is reloaded into the CITER

field.

231–239

0x1C [7:15]

BITER

[6:14]

Beginning or starting major iteration count. As the transfer control descriptor is first

loaded by software, this field must be equal to the value in the CITER field. As the

major iteration count is exhausted, the contents of this field is reloaded into the

CITER field.

If the channel is configured to execute a single service request, the initial values of

BITER and CITER must be 0x0001.

240–241

0x1C [16:17]

BWC

[0:1]

Bandwidth control. This two-bit field provides a mechanism to effectively throttle

the amount of bus bandwidth consumed by the eDMA. In general, as the eDMA

processes the inner minor loop, it continuously generates read/write sequences

until the minor count is exhausted. This field forces the eDMA to stall after the

completion of each read/write access to control the bus request bandwidth seen

by the system bus crossbar switch (XBAR).

To minimize start-up latency, bandwidth control stalls are suppressed for the first

two system bus cycles and after the last write of each minor loop.

00 No eDMA engine stalls

01 Reserved

10 eDMA engine stalls for four cycles after each r/w

11 eDMA engine stalls for eight cycles after each r/w

Table 193. TCDn field descriptions (continued)

Bits

Word Offset

[n:n]

Field Name Description

Loading...

Loading...