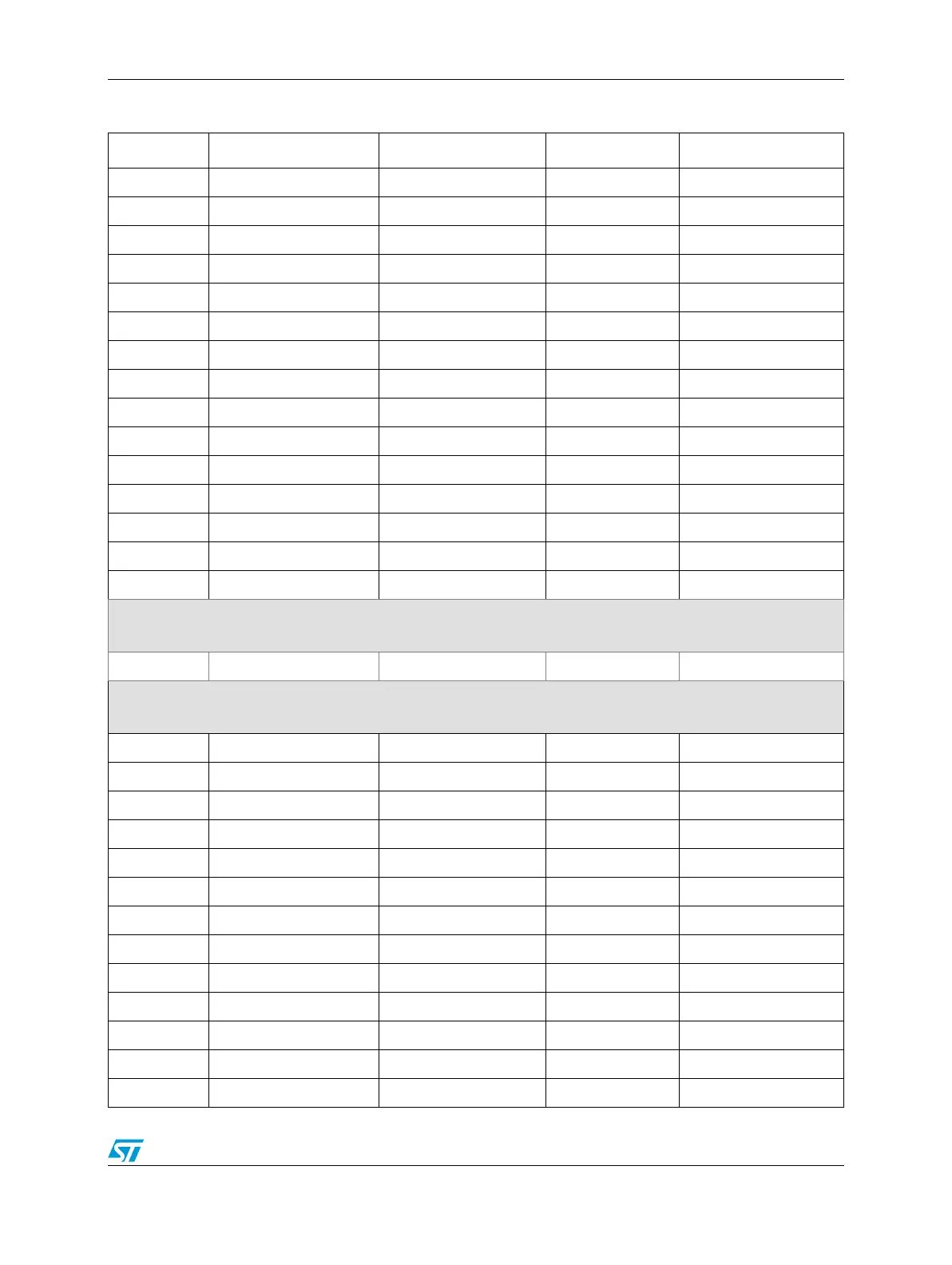

RM0046 Registers Under Protection

Doc ID 16912 Rev 5 917/936

SIUL IFMC11 32 0x102C bits[0:31]

SIUL IFMC12 32 0x1030 bits[0:31]

SIUL IFMC13 32 0x1034 bits[0:31]

SIUL IFMC14 32 0x1038 bits[0:31]

SIUL IFMC15 32 0x103C bits[0:31]

SIUL IFMC16 32 0x1040 bits[0:31]

SIUL IFMC17 32 0x1044 bits[0:31]

SIUL IFMC18 32 0x1048 bits[0:31]

SIUL IFMC19 32 0x104C bits[0:31]

SIUL IFMC20 32 0x1050 bits[0:31]

SIUL IFMC21 32 0x1054 bits[0:31]

SIUL IFMC22 32 0x1058 bits[0:31]

SIUL IFMC23 32 0x105C bits[0:31]

SIUL IFMC24 32 0x1060 bits[0:31]

SIUL IFCP 32 0x1080 bits[0:31]

Power Management Unit—Base address: 0xC3FE_8080

1 register to protect

PMU VREG_CTL 32 0x0000 bits[0:31]

MC Mode Entry—Base address: 0xC3FD_C000

39 registers to protect

MC ME ME_ME 32 0x0008 bits[0:31]

MC ME ME_IM 32 0x0010 bits[0:31]

MC ME ME_TEST_MC 32 0x0024 bits[0:31]

MC ME ME_SAFE_MC 32 0x0028 bits[0:31]

MC ME ME_DRUN_MC 32 0x002C bits[0:31]

MC ME ME_RUN0_MC 32 0x0030 bits[0:31]

MC ME ME_RUN1_MC 32 0x0034 bits[0:31]

MC ME ME_RUN2_MC 32 0x0038 bits[0:31]

MC ME ME_RUN3_MC 32 0x003C bits[0:31]

MC ME ME_HALT0_MC 32 0x0040 bits[0:31]

MC ME ME_STOP0_MC 32 0x0048 bits[0:31]

MC ME ME_RUN_PC0 32 0x0080 bits[0:31]

MC ME ME_RUN_PC1 32 0x0084 bits[0:31]

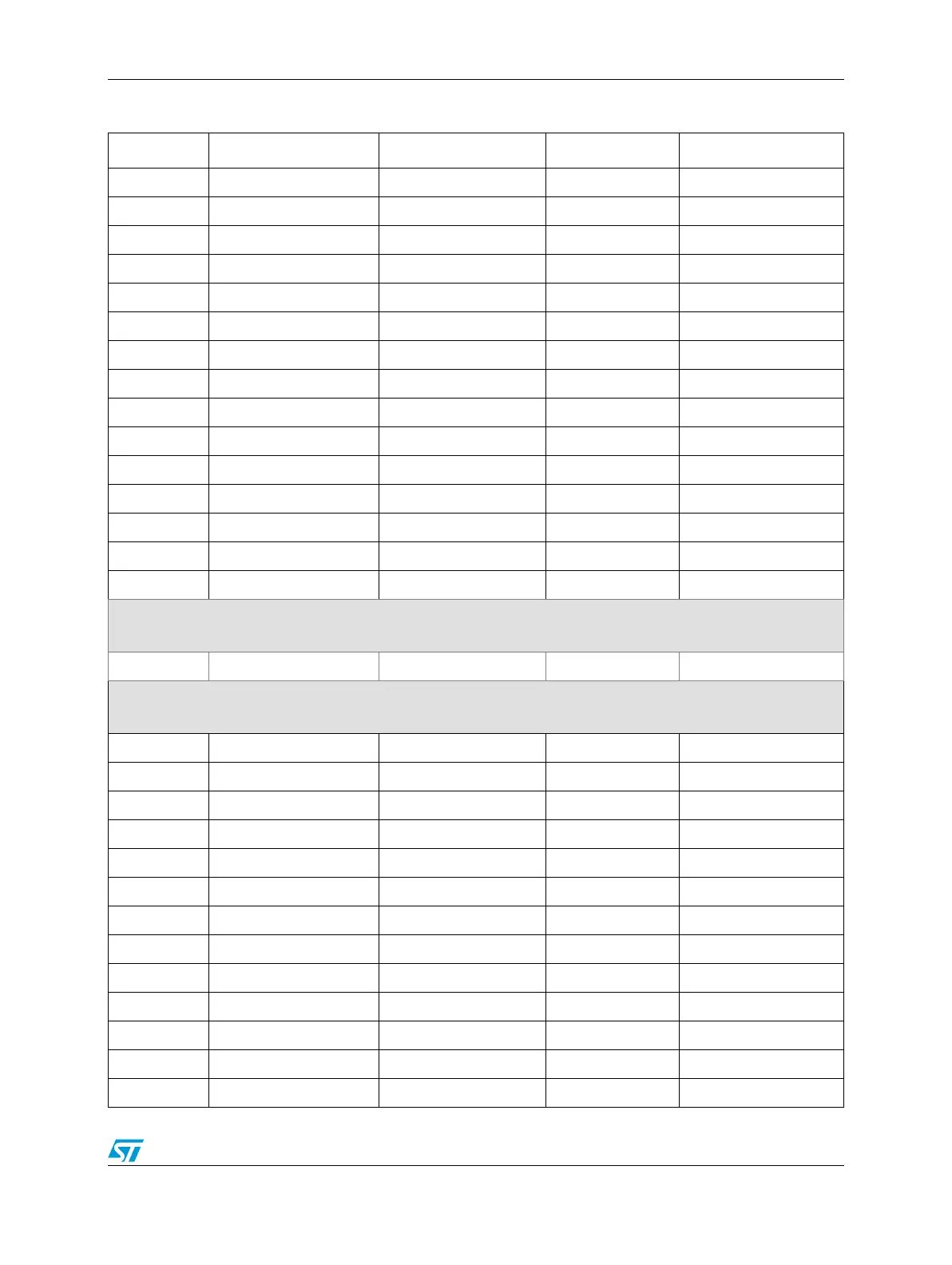

Table 475. Registers under protection (continued)

Module Register Register size (bits) Register offset Protected bitfields

Loading...

Loading...