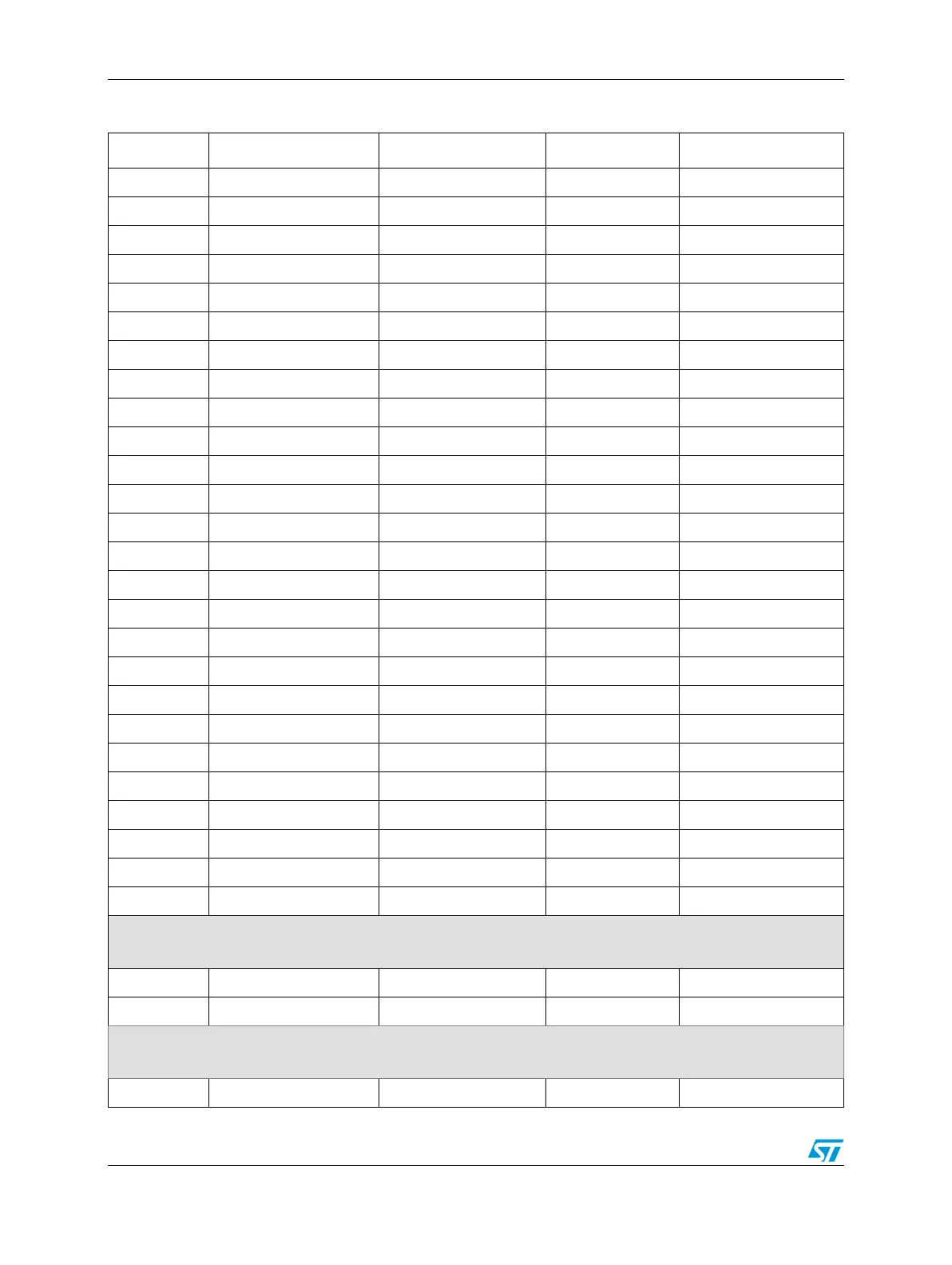

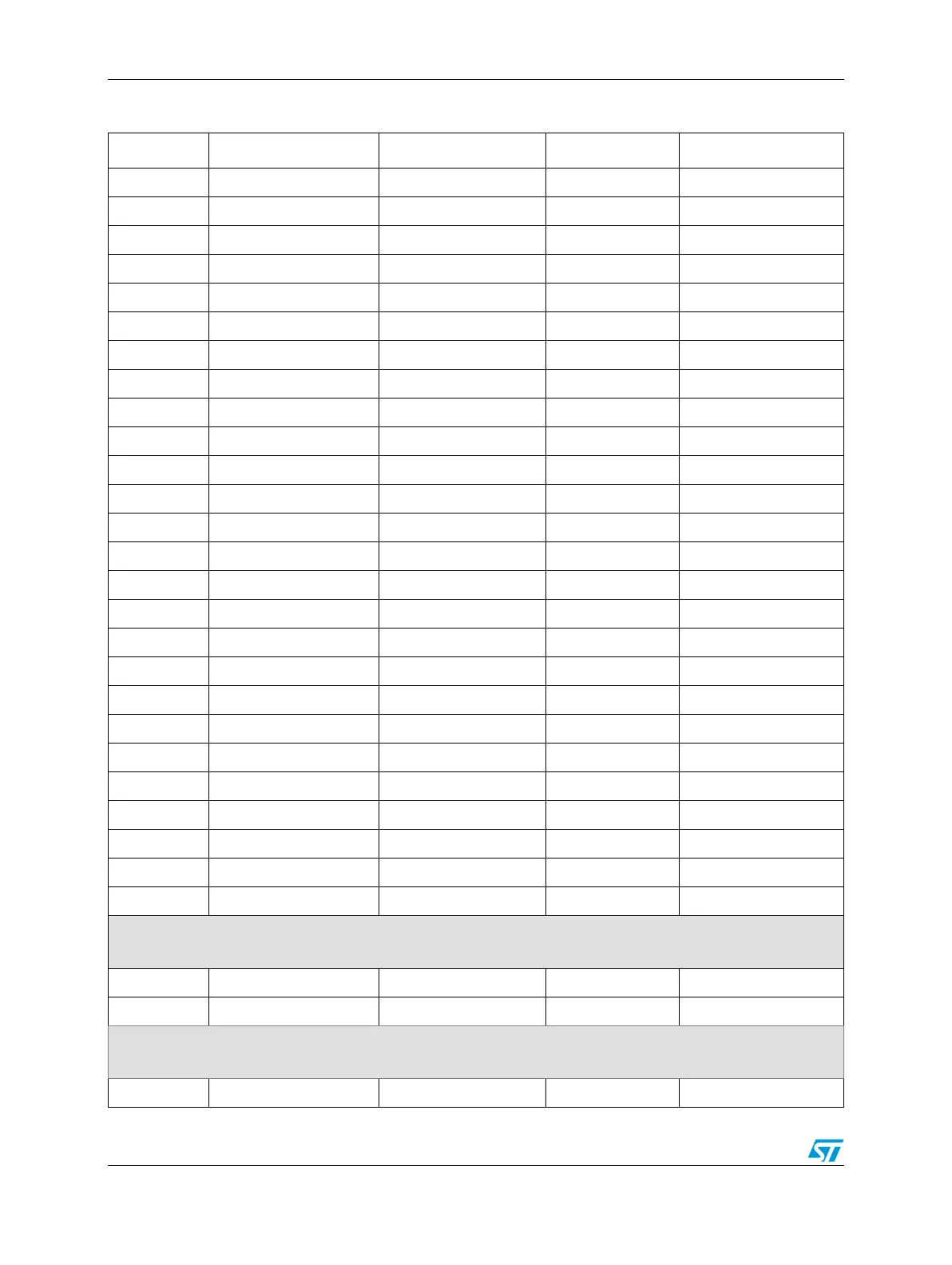

Registers Under Protection RM0046

918/936 Doc ID 16912 Rev 5

MC ME ME_RUN_PC2 32 0x0088 bits[0:31]

MC ME ME_RUN_PC3 32 0x008C bits[0:31]

MC ME ME_RUN_PC4 32 0x0090 bits[0:31]

MC ME ME_RUN_PC5 32 0x0094 bits[0:31]

MC ME ME_RUN_PC6 32 0x0098 bits[0:31]

MC ME ME_RUN_PC7 32 0x009C bits[0:31]

MC ME ME_LP_PC0 32 0x00A0 bits[0:31]

MC ME ME_LP_PC1 32 0x00A4 bits[0:31]

MC ME ME_LP_PC2 32 0x00A8 bits[0:31]

MC ME ME_LP_PC3 32 0x00AC bits[0:31]

MC ME ME_LP_PC4 32 0x00B0 bits[0:31]

MC ME ME_LP_PC5 32 0x00B4 bits[0:31]

MC ME ME_LP_PC6 32 0x00B8 bits[0:31]

MC ME ME_LP_PC7 32 0x00BC bits[0:31]

MC ME ME_PCTL[4] 8 0x00C4 bits[0:31]

MC ME ME_PCTL[5] 8 0x00C5 bits[0:31]

MC ME ME_PCTL[6] 8 0x00C6 bits[0:31]

MC ME ME_PCTL[16] 8 0x00D0 bits[0:7]

MC ME ME_PCTL[26] 8 0xC0DA bits[0:7]

MC ME ME_PCTL[32] 8 0xC0E0 bits[0:7]

MC ME ME_PCTL[35] 8 0xC0E3 bits[0:7]

MC ME ME_PCTL[38] 8 0xC0E6 bits[0:7]

MC ME ME_PCTL[41] 8 0xC0E9 bits[0:7]

MC ME ME_PCTL[48] 8 0xC0F0 bits[0:7]

MC ME ME_PCTL[49] 8 0xC0F1 bits[0:7]

MC ME ME_PCTL[92] 8 0xC11C bits[0:7]

MC Clock Generation Module—Base address: 0xC3FE_0000

2 registers to protect

MC CGM CGM_OC_EN 8 0x0370 bits[0:7]

MC CGM CGM_OCDS_SC 8 0x0374 bits[0:7]

XOSC—Base address: 0xC3FE_0000

1 register to protect

XOSC OSC_CTL 32 0x0000 bits[0:31]

Table 475. Registers under protection (continued)

Module Register Register size (bits) Register offset Protected bitfields

Loading...

Loading...