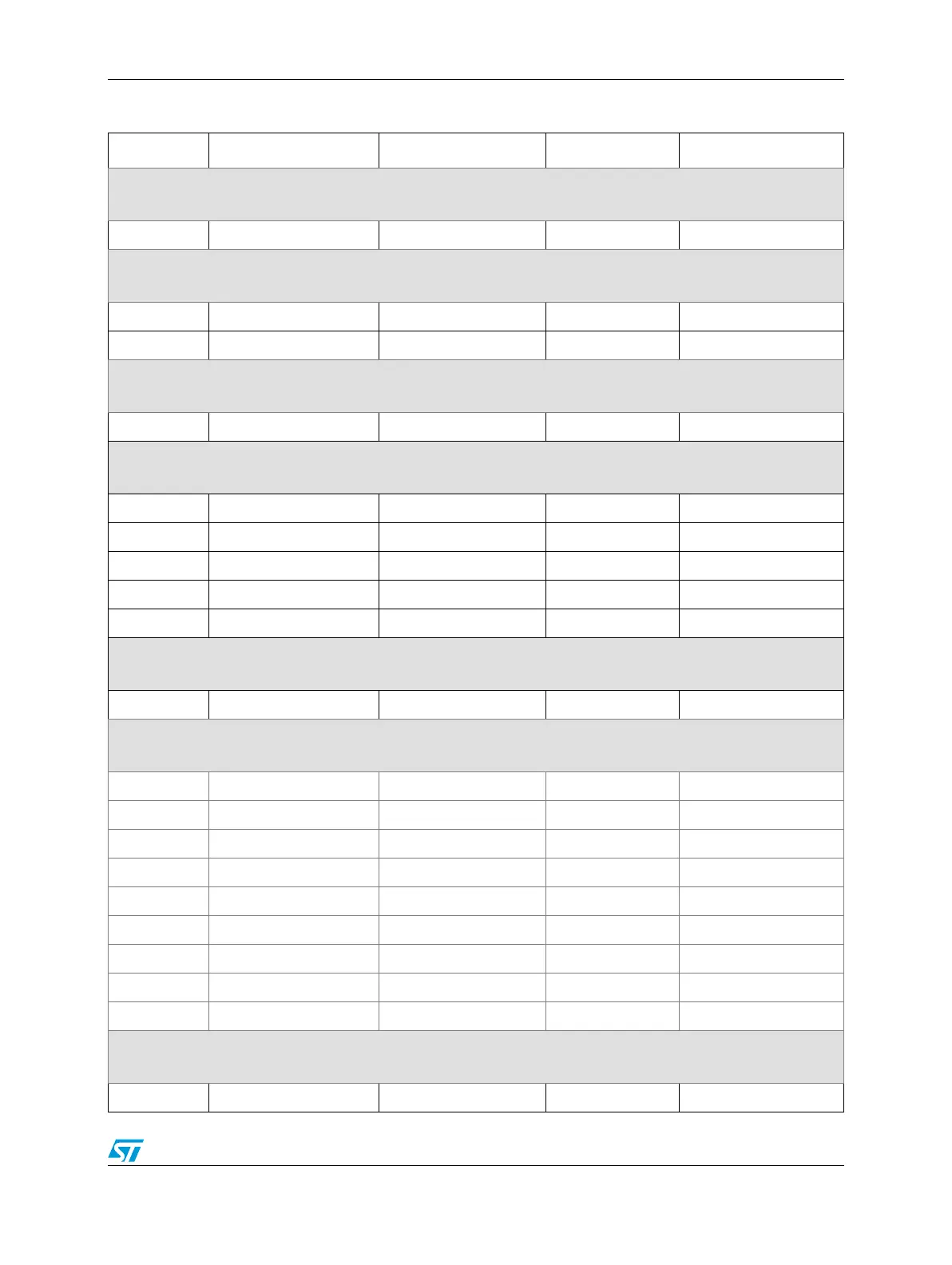

RM0046 Registers Under Protection

Doc ID 16912 Rev 5 919/936

IRC_OSC—Base address: 0xC3FE_0060

1 register to protect

IRC_OSC RC_CTL 32 0x0000 bits[0:31]

FM PLL 0—Base address: 0xC3FE_00A0

2 registers to protect

FMPLL 0 CR 32 0x0000 bits[0:31]

FMPLL 0 MR 32 0x0004 bits[0:31]

CMU 0—Base address: 0xC3FE_0100

1 register to protect

CMU 0 CMU_CSR 32 0x0000 bits[0:31]

MC Reset Generation Module—Base address: 0xC3FE_4000

5 registers to protect

MC RGM RGM_FERD 16 0x0004 bits[0:15]

MC RGM RGM_DERD 16 0x0006 bits[0:15]

MC RGM RGM_FEAR 16 0x0010 bits[0:15]

MC RGM RGM_FESS 16 0x0018 bits[0:15]

MC RGM RGM_FBRE 16 0x001C bits[0:15]

MCPower Control Unit—Base address: 0xC3FE_8000

1 register to protect

MC PCU PCONF2 32 0x0008 bits[0:31]

PIT_RTI—Base address: 0xC3FF_0000

9 registers to protect

PIT_RTI PIT_RTI_PITMCR 32 0x0000 32-bit

PIT_RTI PIT_RTI_LDVAL0 32 0x0100 32-bit

PIT_RTI PIT_RTI_TCTRL0 32 0x0108 32-bit

PIT_RTI PIT_RTI_LDVAL1 32 0x0110 32-bit

PIT_RTI PIT_RTI_TCTRL1 32 0x0118 32-bit

PIT_RTI PIT_RTI_LDVAL2 32 0x0120 32-bit

PIT_RTI PIT_RTI_TCTRL2 32 0x0128 32-bit

PIT_RTI PIT_RTI_LDVAL3 32 0x0130 32-bit

PIT_RTI PIT_RTI_TCTRL3 32 0x0138 32-bit

ADC 0—Base address: 0xFFE0_0000

10 registers to protect

ADC 0 CLR0 32 0x0000 32-bit

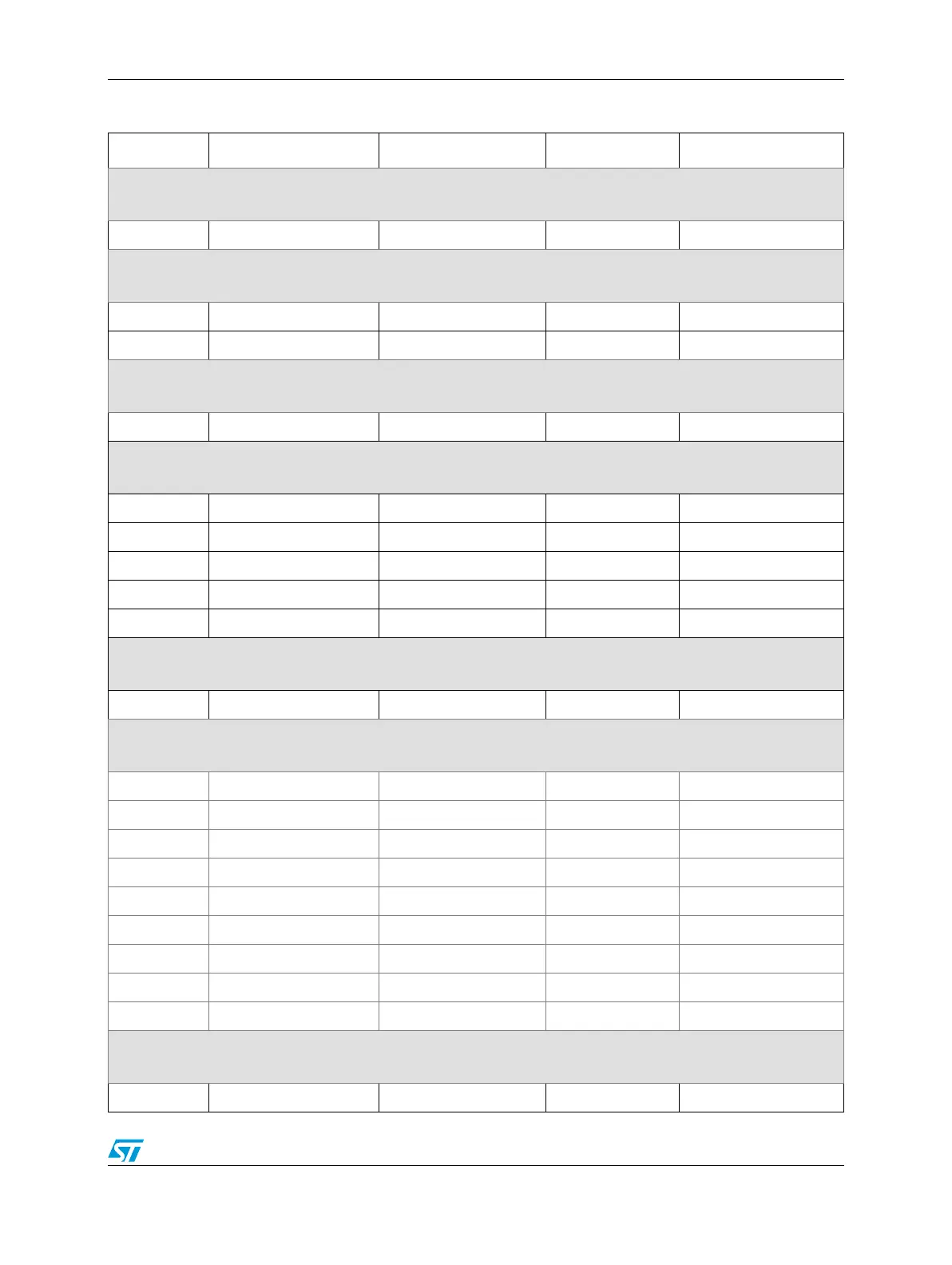

Table 475. Registers under protection (continued)

Module Register Register size (bits) Register offset Protected bitfields

Loading...

Loading...