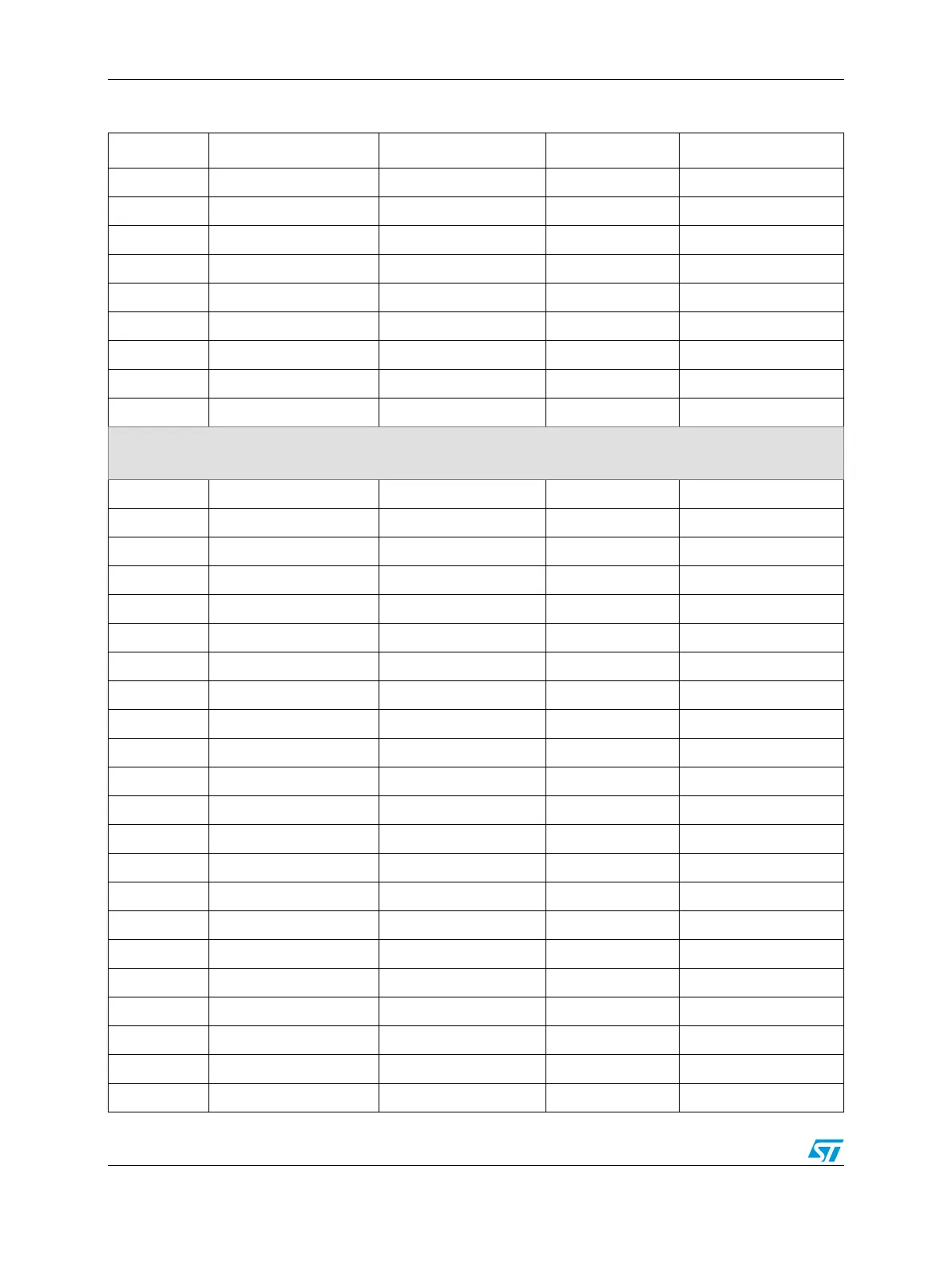

Registers Under Protection RM0046

920/936 Doc ID 16912 Rev 5

ADC 0 CLR1 32 0x0004 32-bit

ADC 0 CLR2 32 0x0008 32-bit

ADC 0 CLR3 32 0x000C 32-bit

ADC 0 CLR4 32 0x0010 32-bit

ADC 0 TRC0 32 0x0034 32-bit

ADC 0 TRC1 32 0x0038 32-bit

ADC 0 TRC2 32 0x003C 32-bit

ADC 0 TRC3 32 0x0040 32-bit

ADC 0 PREREG 32 0x00A8 32-bit

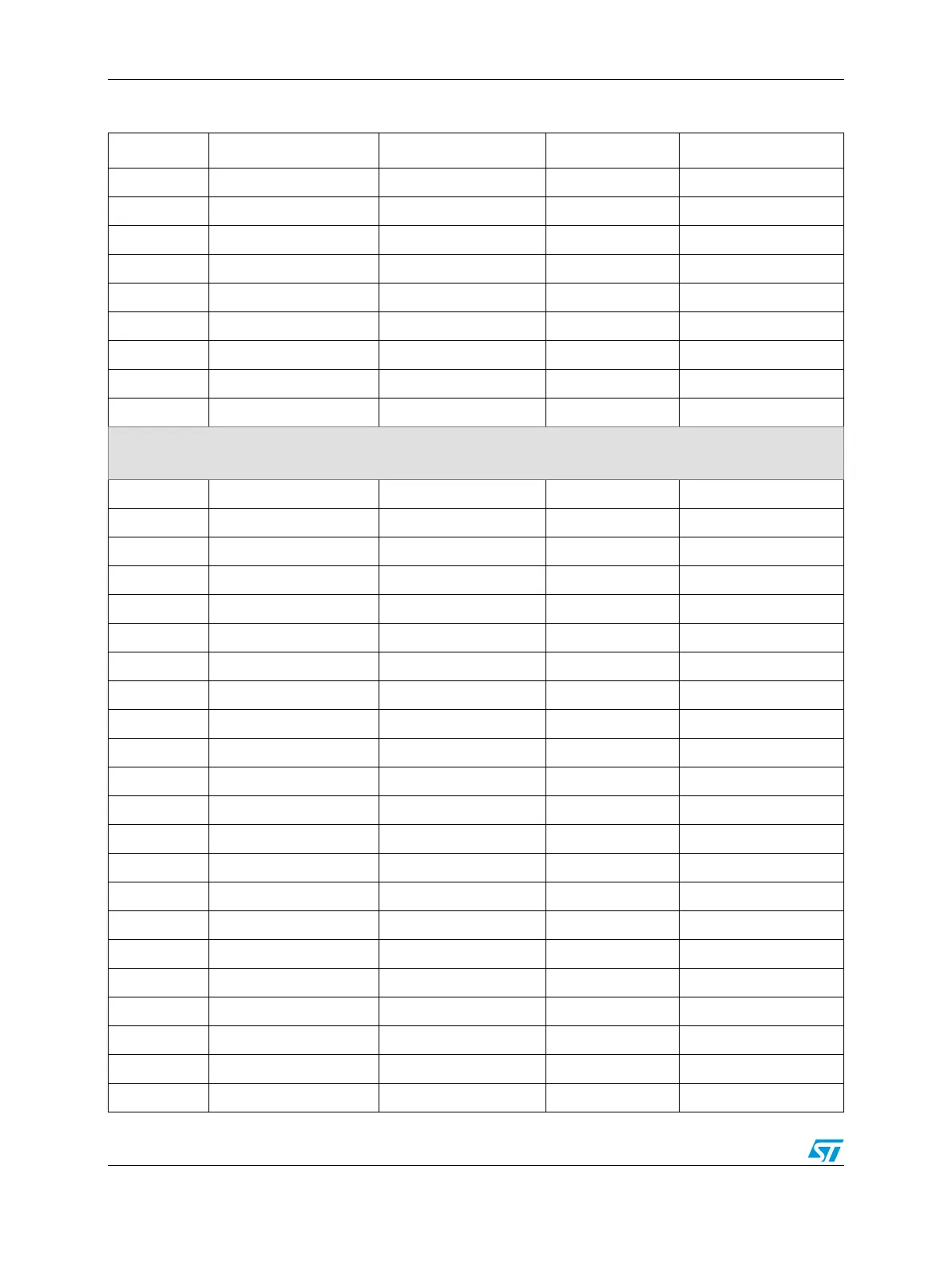

eTimer 0—Base address: 0xFFE1_8000

24 registers to protect

eTimer 0 CH0_CTRL 16 0x000E 16-bit

eTimer 0 CH0_CTRL2 16 0x0010 16-bit

eTimer 0 CH0_CTRL3 16 0x0012 16-bit

eTimer 0 CH0_CCCTRL 16 0x001C 16-bit

eTimer 0 CH1_CTRL 16 0x002E 16-bit

eTimer 0 CH1_CTRL2 16 0x0030 16-bit

eTimer 0 CH1_CTRL3 16 0x0032 16-bit

eTimer 0 CH1_CCCTRL 16 0x003C 16-bit

eTimer 0 CH2_CTRL 16 0x004E 16-bit

eTimer 0 CH2_CTRL2 16 0x0050 16-bit

eTimer 0 CH2_CTRL3 16 0x0052 16-bit

eTimer 0 CH2_CCCTRL 16 0x005C 16-bit

eTimer 0 CH3_CTRL 16 0x006E 16-bit

eTimer 0 CH3_CTRL2 16 0x0070 16-bit

eTimer 0 CH3_CTRL3 16 0x0072 16-bit

eTimer 0 CH3_CCCTRL 16 0x007C 16-bit

eTimer 0 CH4_CTRL 16 0x008E 16-bit

eTimer 0 CH4_CTRL2 16 0x0090 16-bit

eTimer 0 CH4_CTRL3 16 0x0092 16-bit

eTimer 0 CH4_CCCTRL 16 0x009C 16-bit

eTimer 0 CH5_CTRL 16 0x00AE 16-bit

eTimer 0 CH5_CTRL2 16 0x00B0 16-bit

Table 475. Registers under protection (continued)

Module Register Register size (bits) Register offset Protected bitfields

Loading...

Loading...