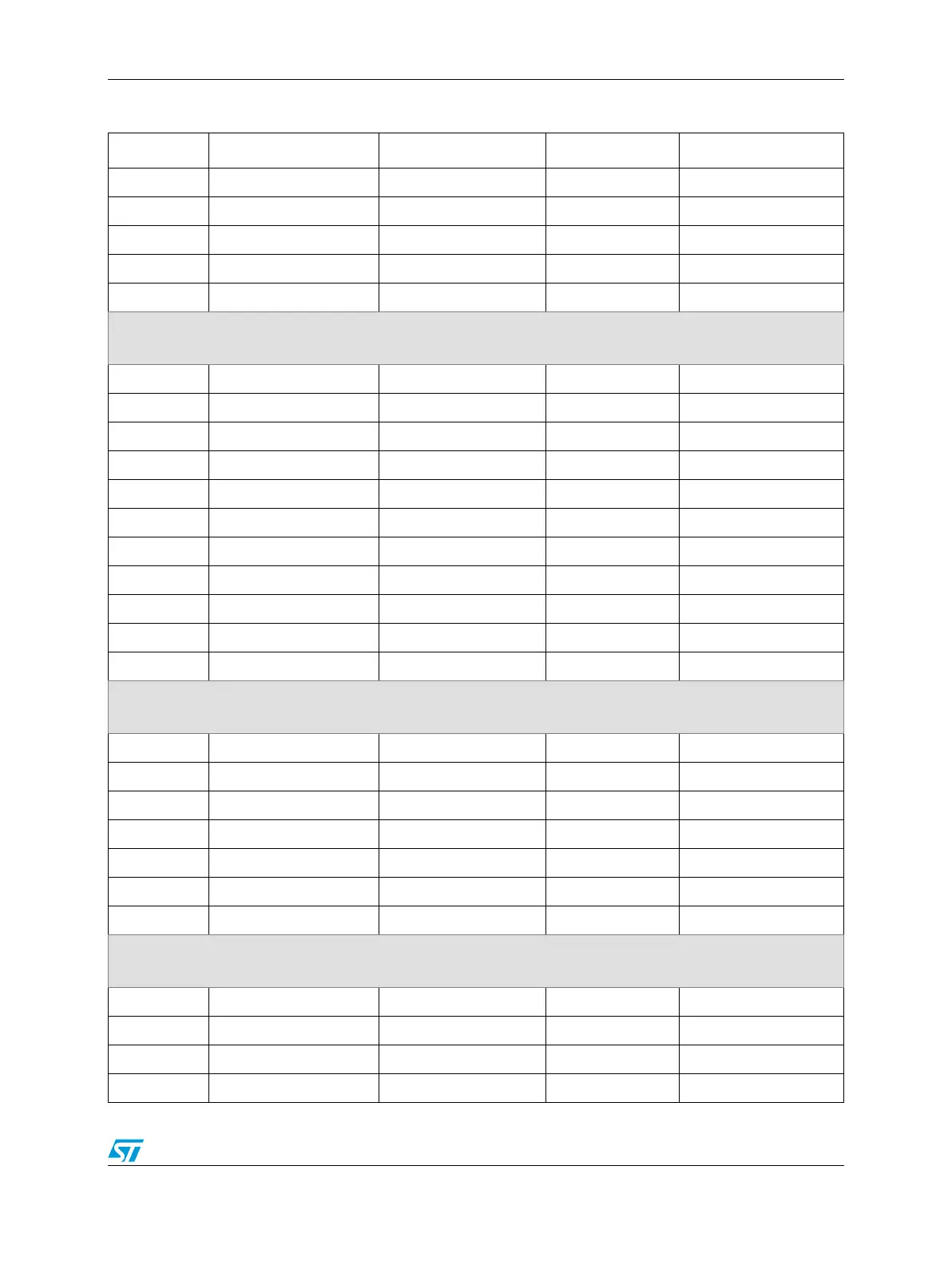

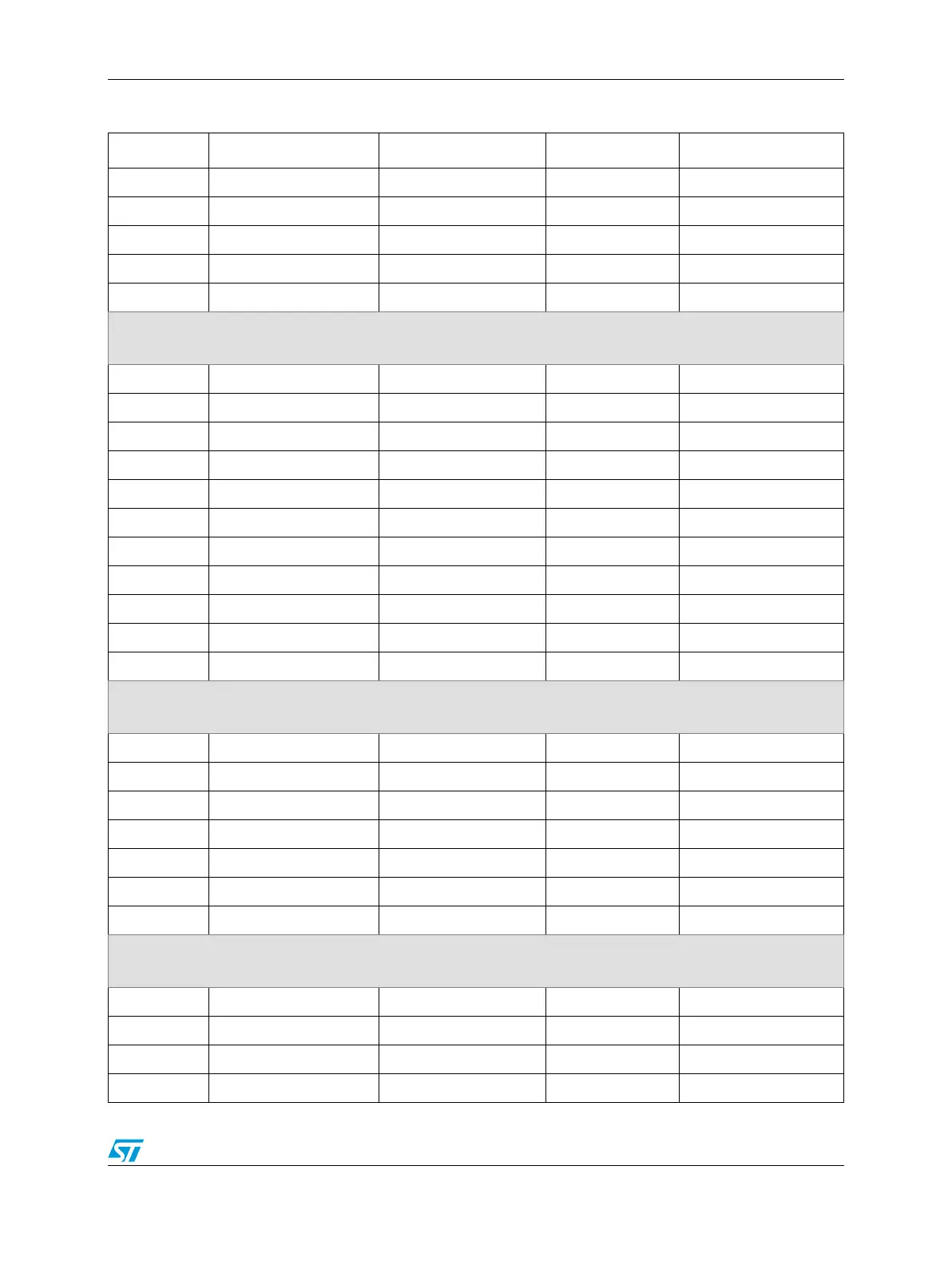

RM0046 Registers Under Protection

Doc ID 16912 Rev 5 923/936

DSPI 1 DSPI_CTAR4 32 0x001C 32-bit

DSPI 1 DSPI_CTAR5 32 0x0020 32-bit

DSPI 1 DSPI_CTAR6 32 0x0024 32-bit

DSPI 1 DSPI_CTAR7 32 0x0028 32-bit

DSPI 1 DSPI_RSER 32 0x0030 32-bit

DSPI 2—Base address: 0xFFF9_8000

11 registers to protect

DSPI 2 DSPI_MCR 32 0x0000 32-bit

DSPI 2 DSPI_TCR 32 0x0008 32-bit

DSPI 2 DSPI_CTAR0 32 0x000C 32-bit

DSPI 2 DSPI_CTAR1 32 0x0010 32-bit

DSPI 2 DSPI_CTAR2 32 0x0014 32-bit

DSPI 2 DSPI_CTAR3 32 0x0018 32-bit

DSPI 2 DSPI_CTAR4 32 0x001C 32-bit

DSPI 2 DSPI_CTAR5 32 0x0020 32-bit

DSPI 2 DSPI_CTAR6 32 0x0024 32-bit

DSPI 2 DSPI_CTAR7 32 0x0028 32-bit

DSPI 2 DSPI_RSER 32 0x0030 32-bit

FlexCAN—Base address: 0xFFFC_0000

7 registers to protect

FlexCAN CANx_MCR 32 0x0000 32-bit

FlexCAN CANx_CTRL 32 0x0004 32-bit

FlexCAN CANx_RXGMASK 32 0x0010 32-bit

FlexCAN CANx_RX14MASK 32 0x0014 32-bit

FlexCAN CANx_RX15MASK 32 0x0018 32-bit

FlexCAN CANx_IMASK2 32 0x0024 32-bit

FlexCAN CANx_IMASK 32 0x0028 32-bit

Safety Port—Base address: 0xFFFE_8000

7 registers to protect

Safety port CANx_MCR 32 0x0000 32-bit

Safety port CANx_CTRL 32 0x0004 32-bit

Safety port CANx_RXGMASK 32 0x0010 32-bit

Safety port CANx_RX14MASK 32 0x0014 32-bit

Table 475. Registers under protection (continued)

Module Register Register size (bits) Register offset Protected bitfields

Loading...

Loading...