Register 9: GPTM Interrupt Clear (GPTMICR), offset 0x024

This register is used to clear the status bits in the GPTMRIS and GPTMMIS registers. Writing a 1

to a bit clears the corresponding bit in the GPTMRIS and GPTMMIS registers.

GPTM Interrupt Clear (GPTMICR)

16/32-bit Timer 0 base: 0x4003.0000

16/32-bit Timer 1 base: 0x4003.1000

16/32-bit Timer 2 base: 0x4003.2000

16/32-bit Timer 3 base: 0x4003.3000

16/32-bit Timer 4 base: 0x4003.4000

16/32-bit Timer 5 base: 0x4003.5000

16/32-bit Timer 6 base: 0x400E.0000

16/32-bit Timer 7 base: 0x400E.1000

Offset 0x024

Type W1C, reset 0x0000.0000

16171819202122232425262728293031

reserved

ROROROROROROROROROROROROROROROROType

0000000000000000Reset

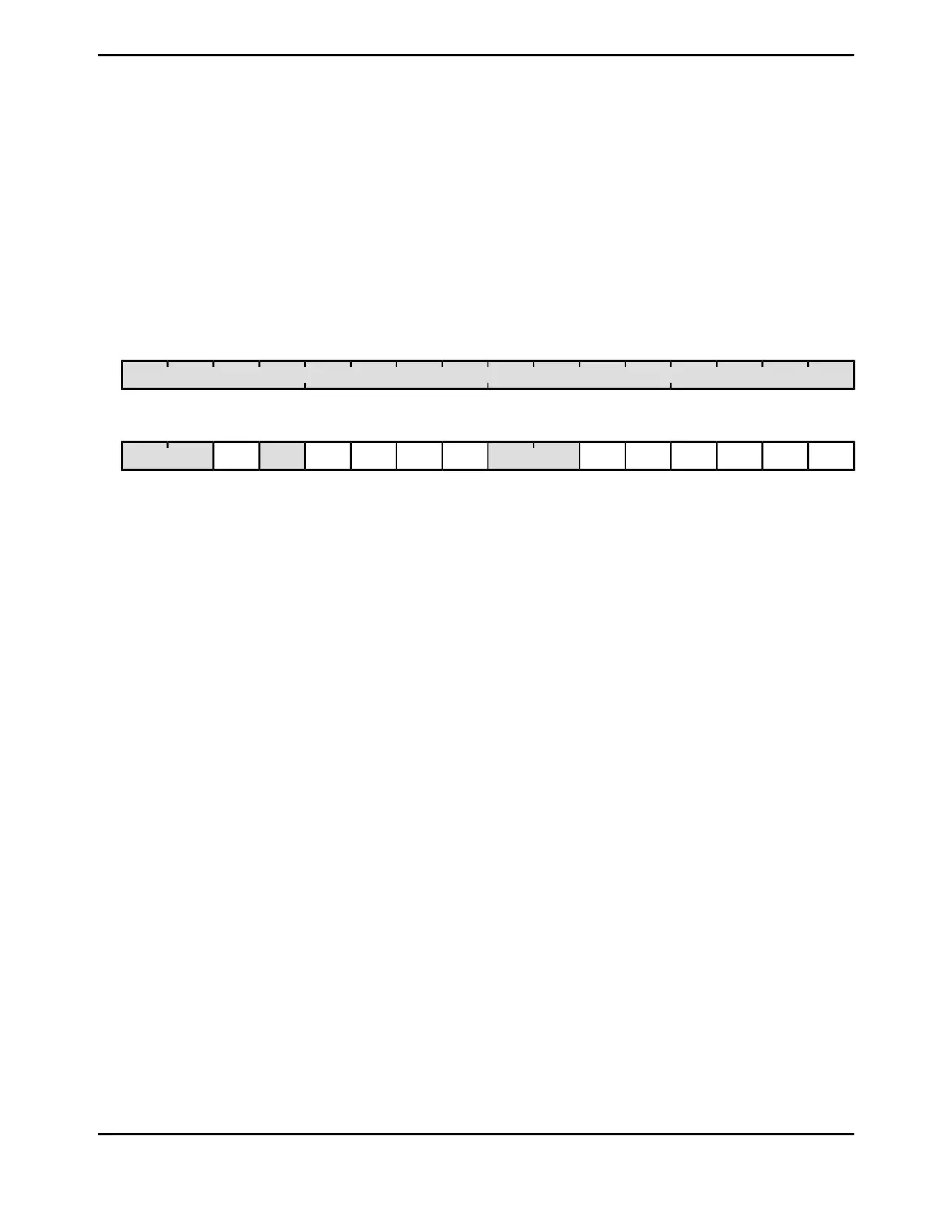

0123456789101112131415

TATOCINT

CAMCINTCAECINTRTCCINTTAMCINTDMAAINTreserved

TBTOCINT

CBMCINTCBECINTTBMCINTreservedDMABINTreserved

W1CW1CW1CW1CW1CW1CROROW1CW1CW1CW1CROW1CROROType

0000000000000000Reset

DescriptionResetTypeNameBit/Field

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x0000ROreserved31:14

GPTM Timer B DMA Done Interrupt Clear

Writing a 1 to this bit clears the DMABRIS bit in the GPTMRIS register

and the DMABMIS bit in the GPTMMIS register.

0W1CDMABINT13

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x0ROreserved12

GPTM Timer B Match Interrupt Clear

Writing a 1 to this bit clears the TBMRIS bit in the GPTMRIS register

and the TBMMIS bit in the GPTMMIS register.

0W1CTBMCINT11

GPTM Timer B Capture Mode Event Interrupt Clear

Writing a 1 to this bit clears the CBERIS bit in the GPTMRIS register

and the CBEMIS bit in the GPTMMIS register.

0W1CCBECINT10

GPTM Timer B Capture Mode Match Interrupt Clear

Writing a 1 to this bit clears the CBMRIS bit in the GPTMRIS register

and the CBMMIS bit in the GPTMMIS register.

0W1CCBMCINT9

GPTM Timer B Time-Out Interrupt Clear

Writing a 1 to this bit clears the TBTORIS bit in the GPTMRIS register

and the TBTOMIS bit in the GPTMMIS register.

0W1CTBTOCINT8

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0ROreserved7:6

June 18, 20141002

Texas Instruments-Production Data

General-Purpose Timers

Loading...

Loading...