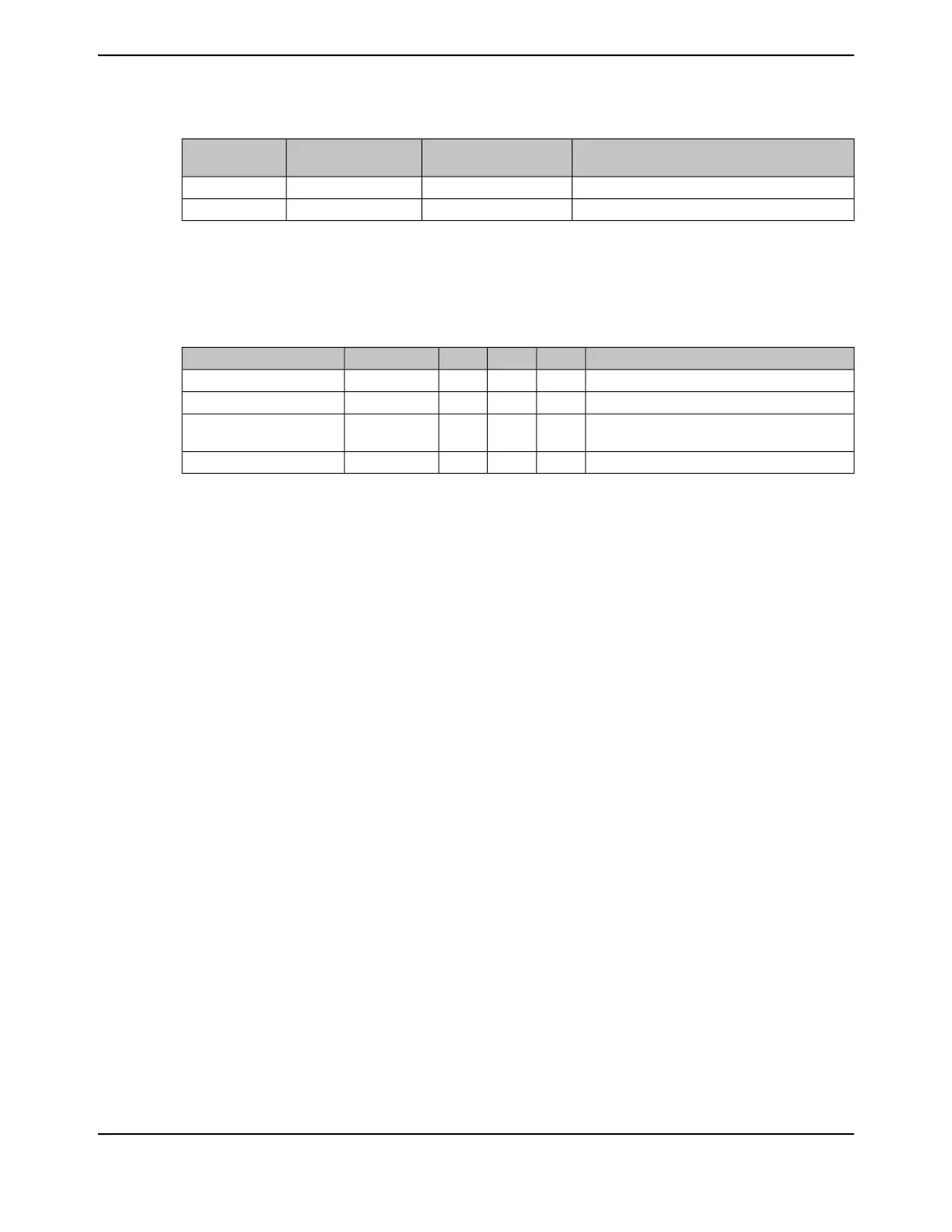

Table 3-5. AP Bit Field Encoding (continued)

DescriptionUnprivileged

Permissions

Privileged

Permissions

AP Bit Field

Read-only, by privileged or unprivileged software.RORO110

Read-only, by privileged or unprivileged software.RORO111

MPU Configuration for a Tiva™ C Series Microcontroller

Tiva™ C Series microcontrollers have only a single processor and no caches. As a result, the MPU

should be programmed as shown in Table 3-6 on page 142.

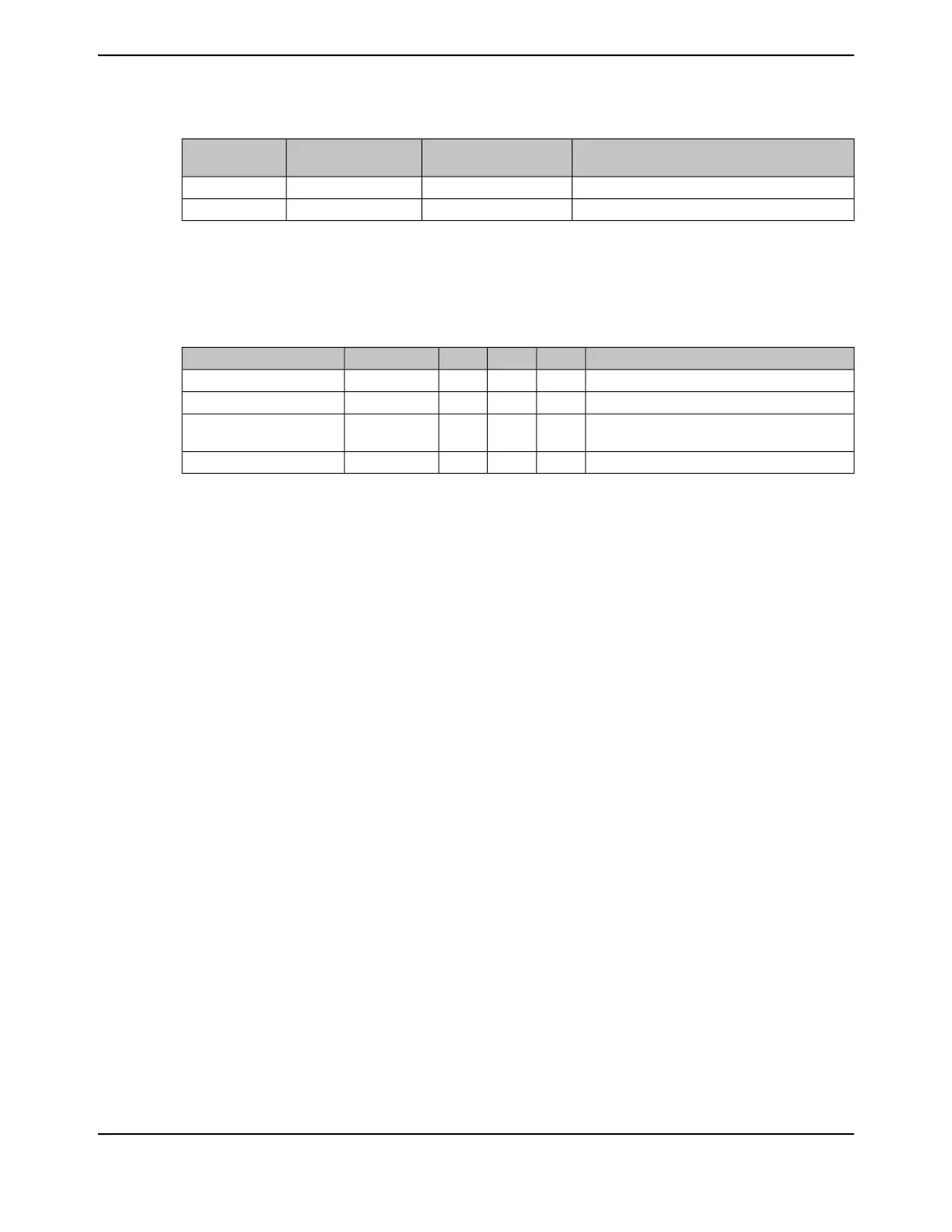

Table 3-6. Memory Region Attributes for Tiva™ C Series Microcontrollers

Memory Type and AttributesBCSTEXMemory Region

Normal memory, non-shareable, write-through010000bFlash memory

Normal memory, shareable, write-through011000bInternal SRAM

Normal memory, shareable, write-back,

write-allocate

111000bExternal SRAM

Device memory, shareable101000bPeripherals

In current Tiva™ C Series microcontroller implementations, the shareability and cache policy

attributes do not affect the system behavior. However, using these settings for the MPU regions

can make the application code more portable. The values given are for typical situations.

3.1.4.3 MPU Mismatch

When an access violates the MPU permissions, the processor generates a memory management

fault (see “Exceptions and Interrupts” on page 103 for more information). The MFAULTSTAT register

indicates the cause of the fault. See page 184 for more information.

3.1.5 Floating-Point Unit (FPU)

This section describes the Floating-Point Unit (FPU) and the registers it uses. The FPU provides:

■ 32-bit instructions for single-precision (C float) data-processing operations

■ Combined multiply and accumulate instructions for increased precision (Fused MAC)

■ Hardware support for conversion, addition, subtraction, multiplication with optional accumulate,

division, and square-root

■ Hardware support for denormals and all IEEE rounding modes

■ 32 dedicated 32-bit single-precision registers, also addressable as 16 double-word registers

■ Decoupled three stage pipeline

The Cortex-M4F FPU fully supports single-precision add, subtract, multiply, divide, multiply and

accumulate, and square root operations. It also provides conversions between fixed-point and

floating-point data formats, and floating-point constant instructions. The FPU provides floating-point

computation functionality that is compliant with the ANSI/IEEE Std 754-2008, IEEE Standard for

Binary Floating-Point Arithmetic, referred to as the IEEE 754 standard. The FPU's single-precision

extension registers can also be accessed as 16 doubleword registers for load, store, and move

operations.

June 18, 2014142

Texas Instruments-Production Data

Cortex-M4 Peripherals

Loading...

Loading...