Register 58: Application Interrupt and Reset Control (APINT), offset 0xD0C

Note: This register can only be accessed from privileged mode.

The APINT register provides priority grouping control for the exception model, endian status for

data accesses, and reset control of the system. To write to this register, 0x05FA must be written to

the VECTKEY field, otherwise the write is ignored.

The PRIGROUP field indicates the position of the binary point that splits the INTx fields in the

Interrupt Priority (PRIx) registers into separate group priority and subpriority fields. Table

3-9 on page 171 shows how the PRIGROUP value controls this split. The bit numbers in the Group

Priority Field and Subpriority Field columns in the table refer to the bits in the INTA field. For the

INTB field, the corresponding bits are 15:13; for INTC, 23:21; and for INTD, 31:29.

Note: Determining preemption of an exception uses only the group priority field.

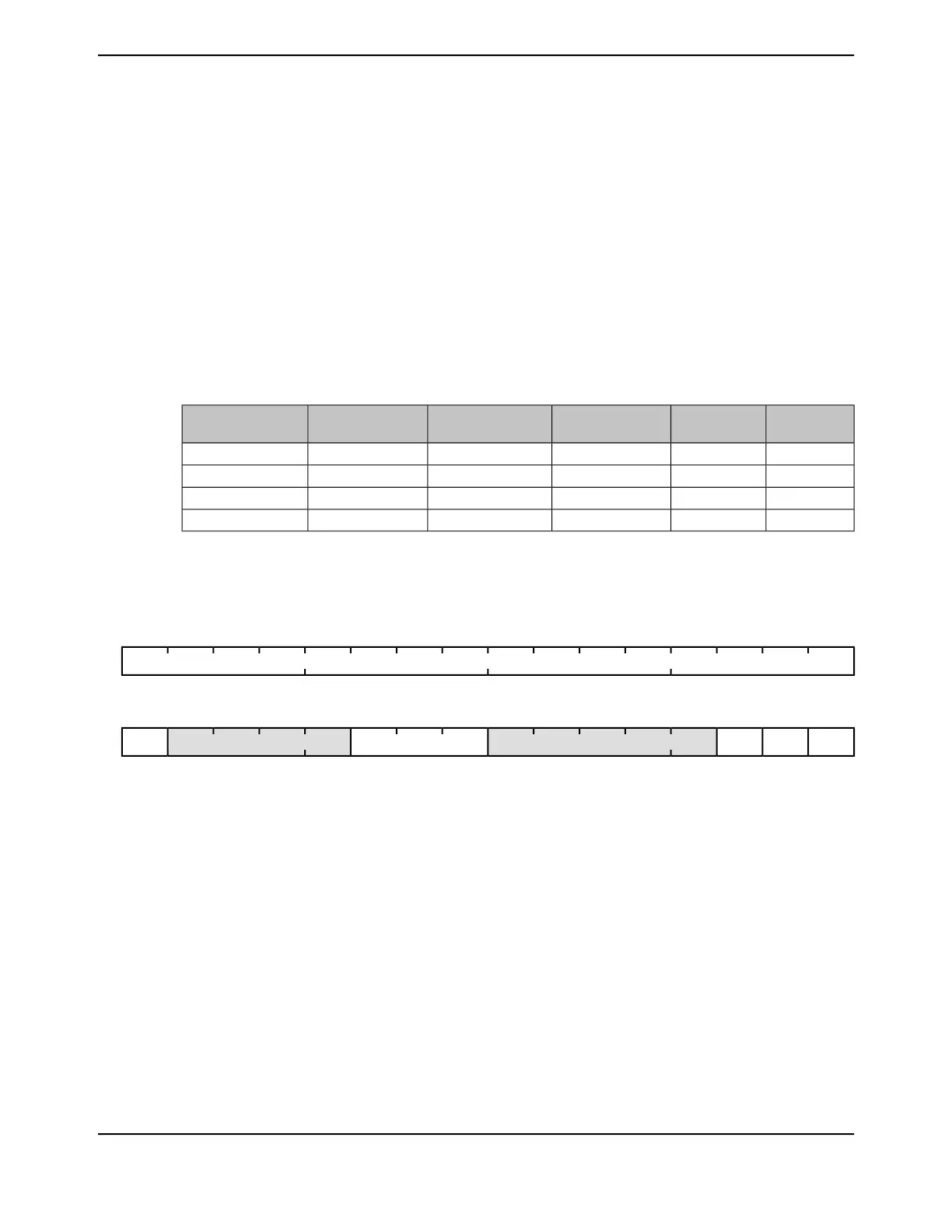

Table 3-9. Interrupt Priority Levels

SubprioritiesGroup

Priorities

Subpriority FieldGroup Priority FieldBinary Point

a

PRIGROUP Bit Field

18None[7:5]bxxx.0x0 - 0x4

24[5][7:6]bxx.y0x5

42[6:5][7]bx.yy0x6

81[7:5]Noneb.yyy0x7

a. INTx field showing the binary point. An x denotes a group priority field bit, and a y denotes a subpriority field bit.

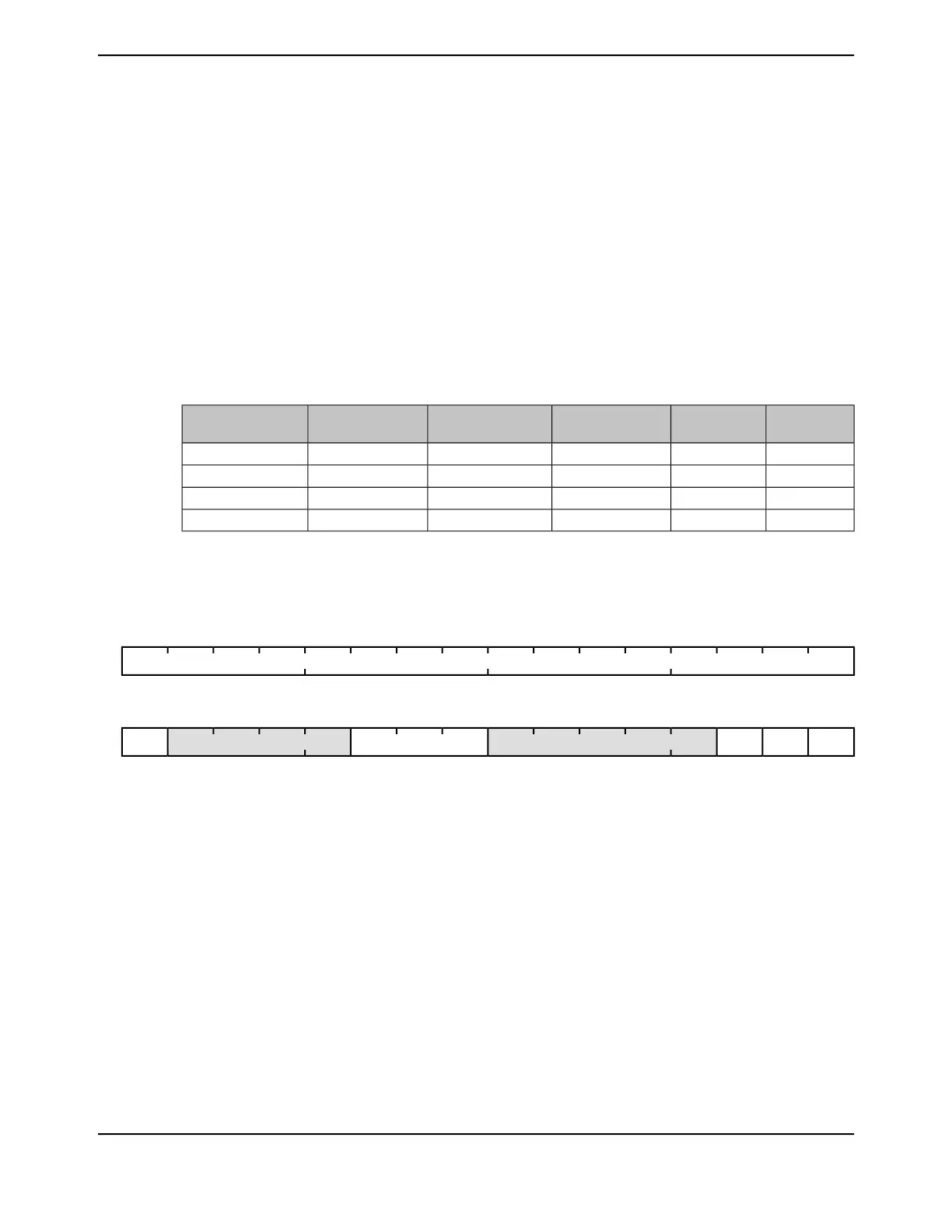

Application Interrupt and Reset Control (APINT)

Base 0xE000.E000

Offset 0xD0C

Type RW, reset 0xFA05.0000

16171819202122232425262728293031

VECTKEY

RWRWRWRWRWRWRWRWRWRWRWRWRWRWRWRWType

1010000001011111Reset

0123456789101112131415

VECTRESETVECTCLRACTSYSRESREQ

reservedPRIGROUPreserved

ENDIANESS

WOWOWORORORORORORWRWRWROROROROROType

0000000000000000Reset

DescriptionResetTypeNameBit/Field

Register Key

This field is used to guard against accidental writes to this register.

0x05FA must be written to this field in order to change the bits in this

register. On a read, 0xFA05 is returned.

0xFA05RWVECTKEY31:16

Data Endianess

The Tiva™ C Series implementation uses only little-endian mode so

this is cleared to 0.

0ROENDIANESS15

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x0ROreserved14:11

171June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...