Register 35: EPI Host-Bus 16 Configuration 3 (EPIHB16CFG3), offset 0x308

Important: The MODE field in the EPICFG register determines which configuration is enabled.

For EPIHB16CFG3 to be valid, the MODE field must be 0x3.

EPI Host-Bus 16 Configuration 3 (EPIHB16CFG3)

Base 0x400D.0000

Offset 0x308

Type RW, reset 0x0008.0000

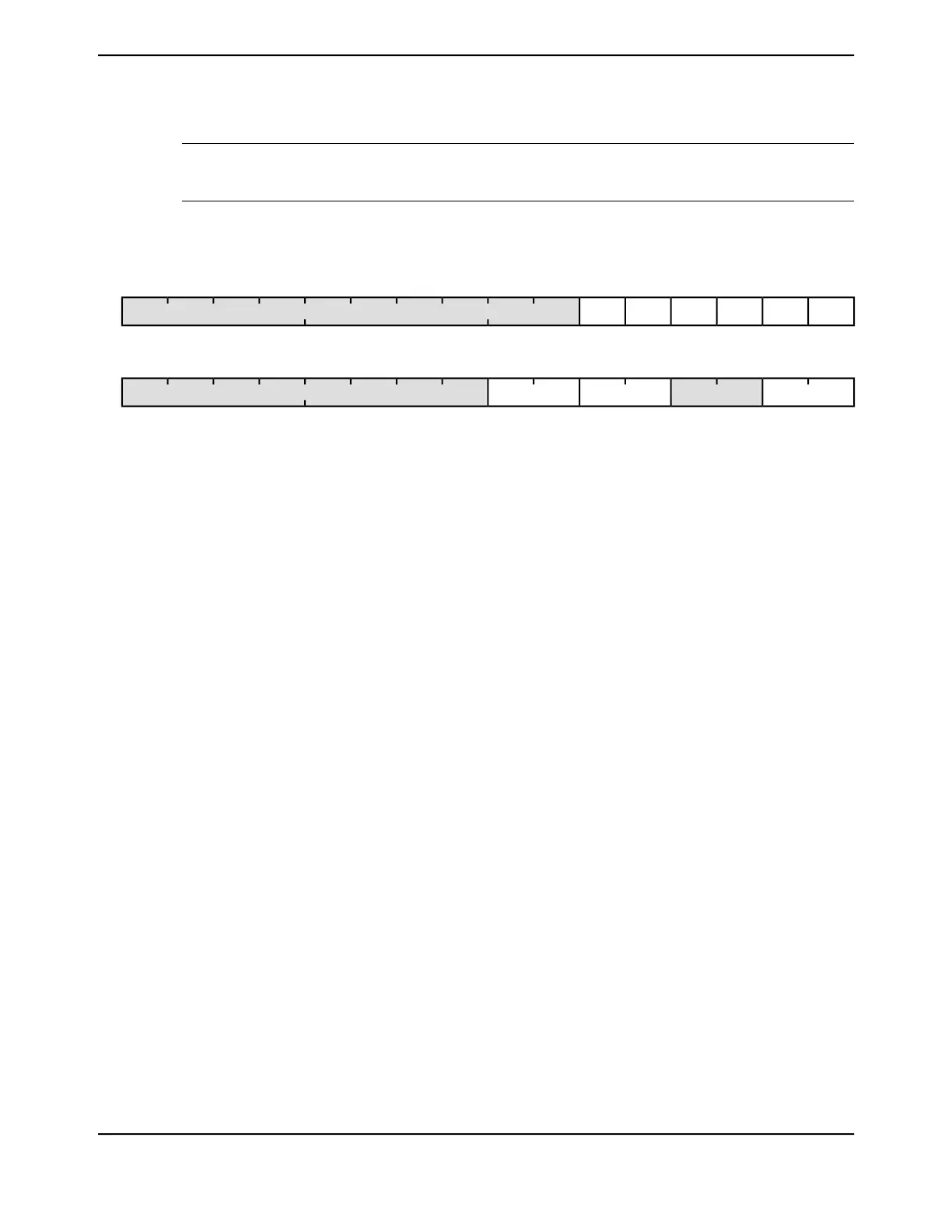

16171819202122232425262728293031

BURSTRDCREWRCREALEHIGHRDHIGHWRHIGHreserved

RWRWRWRWRWRWROROROROROROROROROROType

0001000000000000Reset

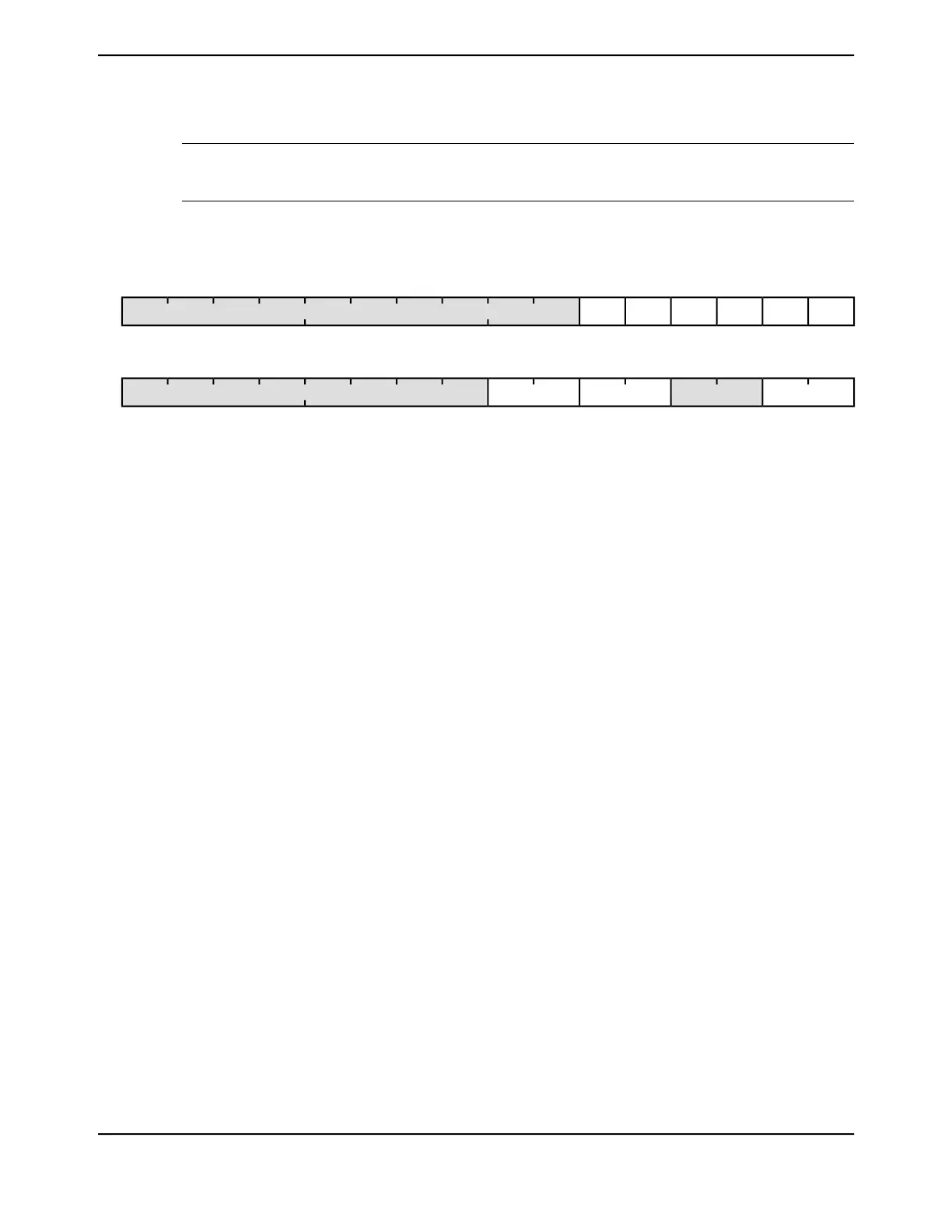

0123456789101112131415

MODEreservedRDWSWRWSreserved

RWRWRORORWRWRWRWROROROROROROROROType

0000000000000000Reset

DescriptionResetTypeNameBit/Field

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x000ROreserved31:22

CS2n WRITE Strobe Polarity

This field is used if the CSBAUD bit is enabled in EPIHB16CFG2.

DescriptionValue

The WRITE strobe for CS2n accesses is WRn (active Low).0

The WRITE strobe for CS2n accesses is WR (active High).1

0RWWRHIGH21

CS2n READ Strobe Polarity

This field is used if the CSBAUD bit is enabled in EPIHB16CFG2.

DescriptionValue

The READ strobe for CS2n accesses is RDn (active Low).0

The READ strobe for CS2n accesses is RD (active High).1

0RWRDHIGH20

CS2n ALE Strobe Polarity

This field is used if the CSBAUD bit is enabled in EPIHB16CFG2.

DescriptionValue

The address latch strobe for CS2n accesses is ADVn (active

Low).

0

The address latch strobe for CS2n accesses is ALE (active

High).

1

1RWALEHIGH19

June 18, 2014918

Texas Instruments-Production Data

External Peripheral Interface (EPI)

Loading...

Loading...