Register 6: UART Fractional Baud-Rate Divisor (UARTFBRD), offset 0x028

The UARTFBRD register is the fractional part of the baud-rate divisor value. All the bits are cleared

on reset. When changing the UARTFBRD register, the new value does not take effect until

transmission/reception of the current character is complete. Any changes to the baud-rate divisor

must be followed by a write to the UARTLCRH register. See “Baud-Rate Generation” on page 1165

for configuration details.

UART Fractional Baud-Rate Divisor (UARTFBRD)

UART0 base: 0x4000.C000

UART1 base: 0x4000.D000

UART2 base: 0x4000.E000

UART3 base: 0x4000.F000

UART4 base: 0x4001.0000

UART5 base: 0x4001.1000

UART6 base: 0x4001.2000

UART7 base: 0x4001.3000

Offset 0x028

Type RW, reset 0x0000.0000

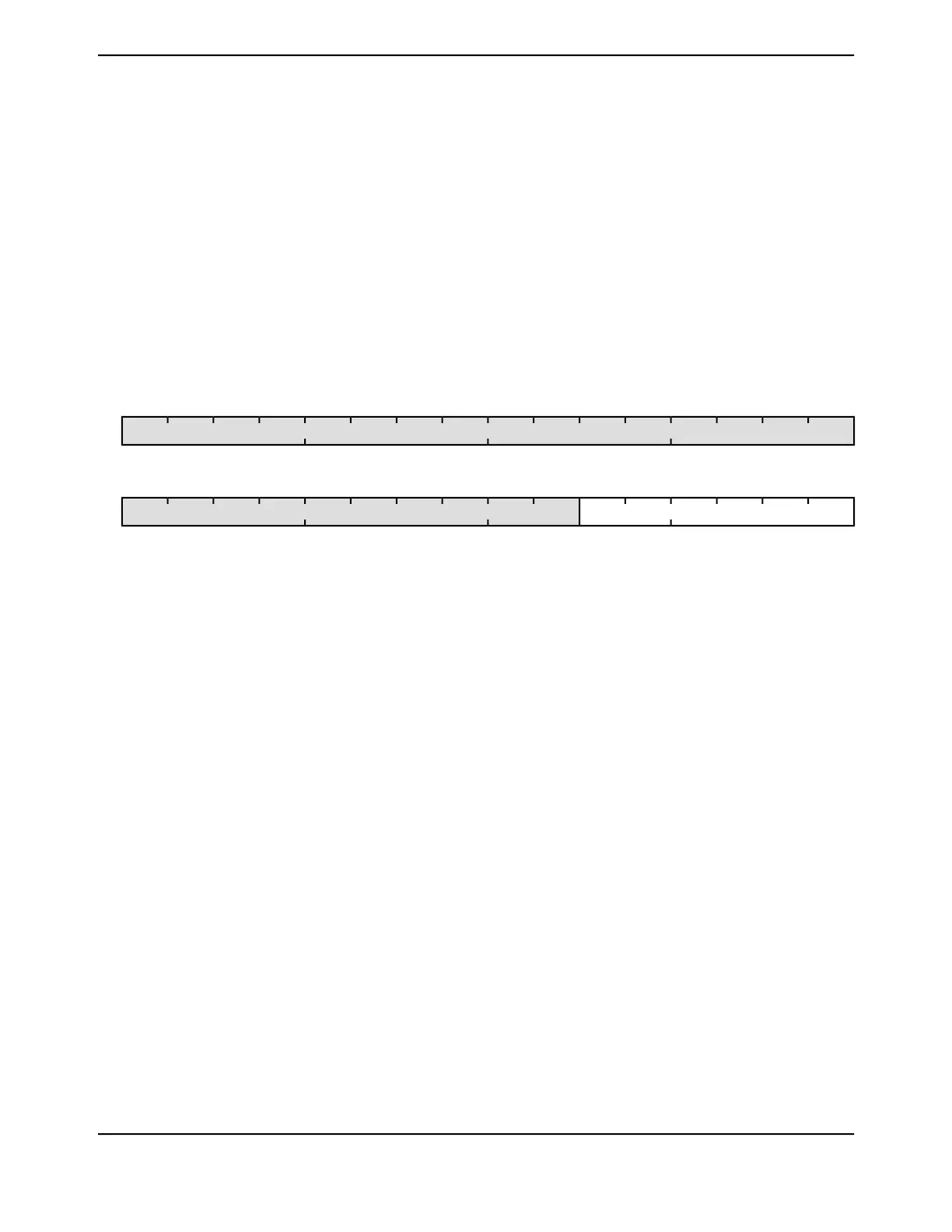

16171819202122232425262728293031

reserved

ROROROROROROROROROROROROROROROROType

0000000000000000Reset

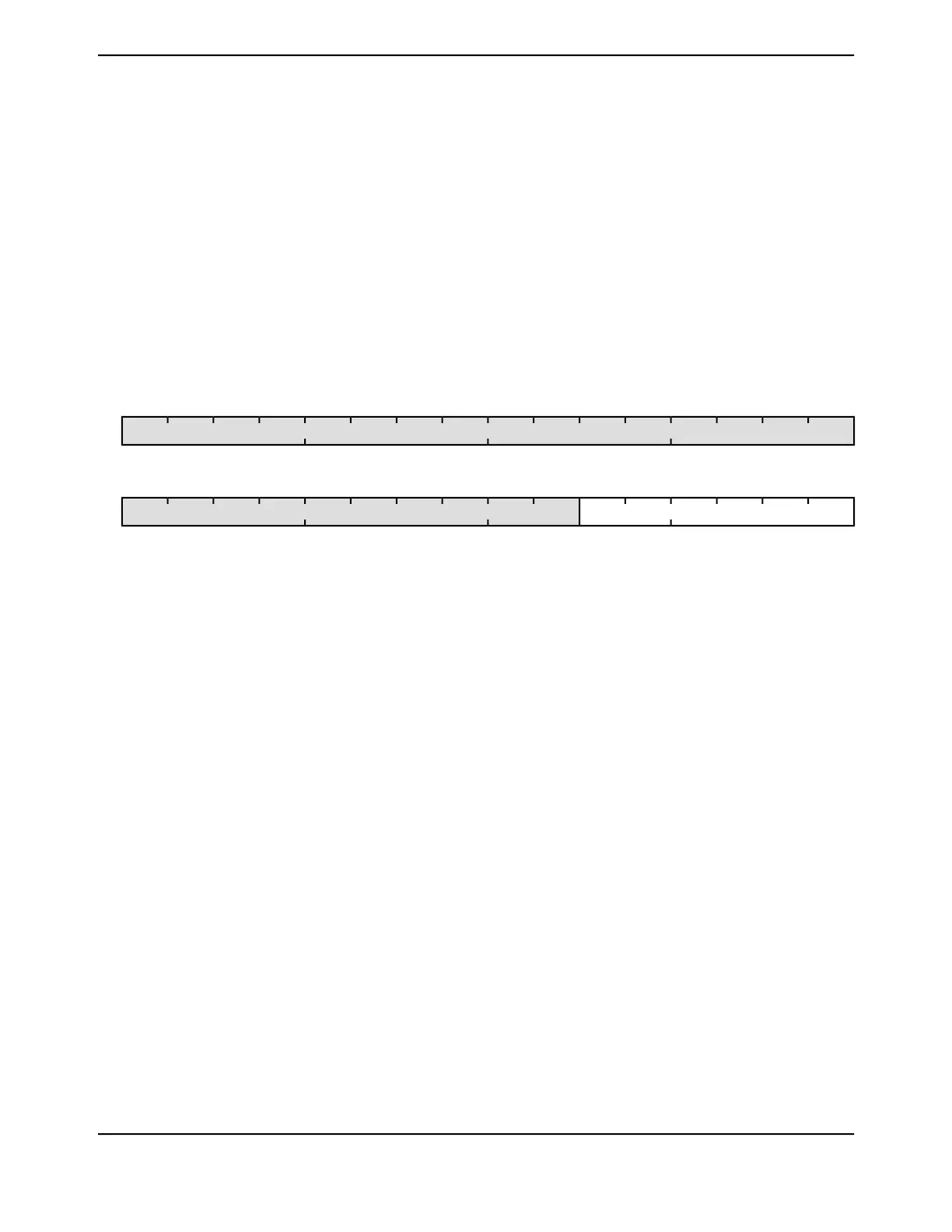

0123456789101112131415

DIVFRACreserved

RWRWRWRWRWRWROROROROROROROROROROType

0000000000000000Reset

DescriptionResetTypeNameBit/Field

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x0000.000ROreserved31:6

Fractional Baud-Rate Divisor0x0RWDIVFRAC5:0

1185June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...