■ The PHY receives the main oscillator (MOSC) which must be 25 MHz ± 50 ppm for proper

operation. The MOSC source can be a single-ended source or a crystal.

PWM Clock Control

The PWMCC register can be used to select the System Clock as the PWM clock source or a divided

System Clock. For more information, see page 1747.

Other Peripheral Clock Control

In the UART and QSSI Clock Control Registers, users can choose between the system clock

(SysClk), which is the default source for the baud clock, and an alternate clock. Note that there may

be special considerations when configuring the baud clock.

Optional Clock Output Signal (DIVSCLK)

An optional clock output, DIVSCLK, is provided which can be used as a clock source to an external

device but bears no timing relationship to other signals. Note that this signal is not synchronized to

the System Clock. By programming the SRC field in the Divisor and Source Clock Configuration

(DIVSCLK) register, the following clock outputs may be selected for DIVSCLK:

■ System Clock

■ PIOSC

■ MOSC

The DIV field in the DIVSCLK register controls the divided output clock frequency. The DIVSCLK

signal is selected as an alternate function of a GPIO signal and has the same inherit electrical

characteristics of a GPIO as listed in “Electrical Characteristics” on page 1818.

System Clock Frequency

The system clock (SysClk) is the clock that is distributed to the processor and the integrated

peripherals after clock gating. The SysClk frequency is based on the frequency of the clock source

and the divisor factor. For example, if the PLL is not being used and the device is not in deep sleep

mode, then the OSYSDIV bit field in the RSCLKCFG register is the divisor used to determine the

system clock. If the PLL is being used, then PSYSDIV bit field in the RSCLKCFG register must be

programmed as well as the values in the PLLFREQ0 and PLLFREQ1 registers. If the device is in

deep sleep mode, then the Deep Sleep Clock Configuration Register (DSCLKCFG) can be

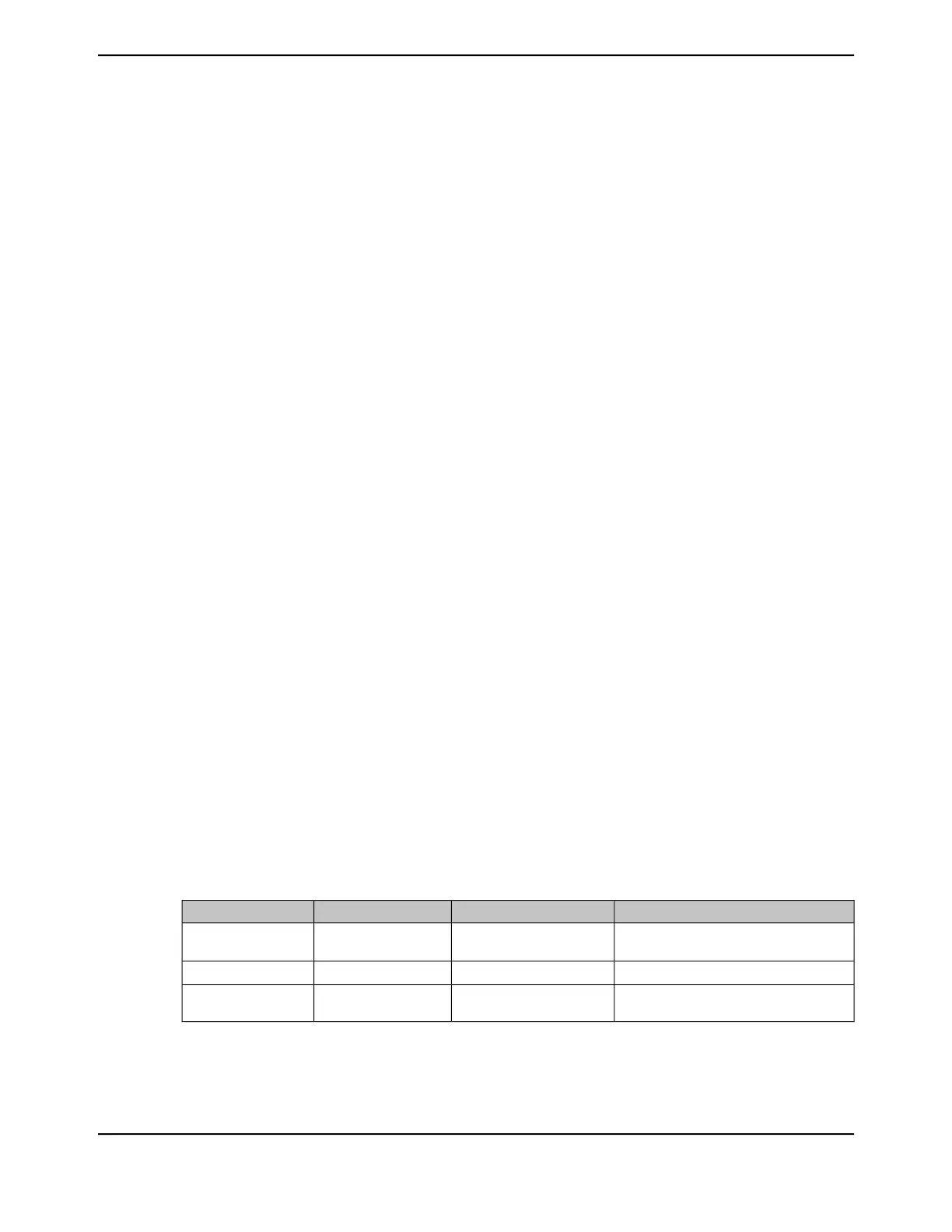

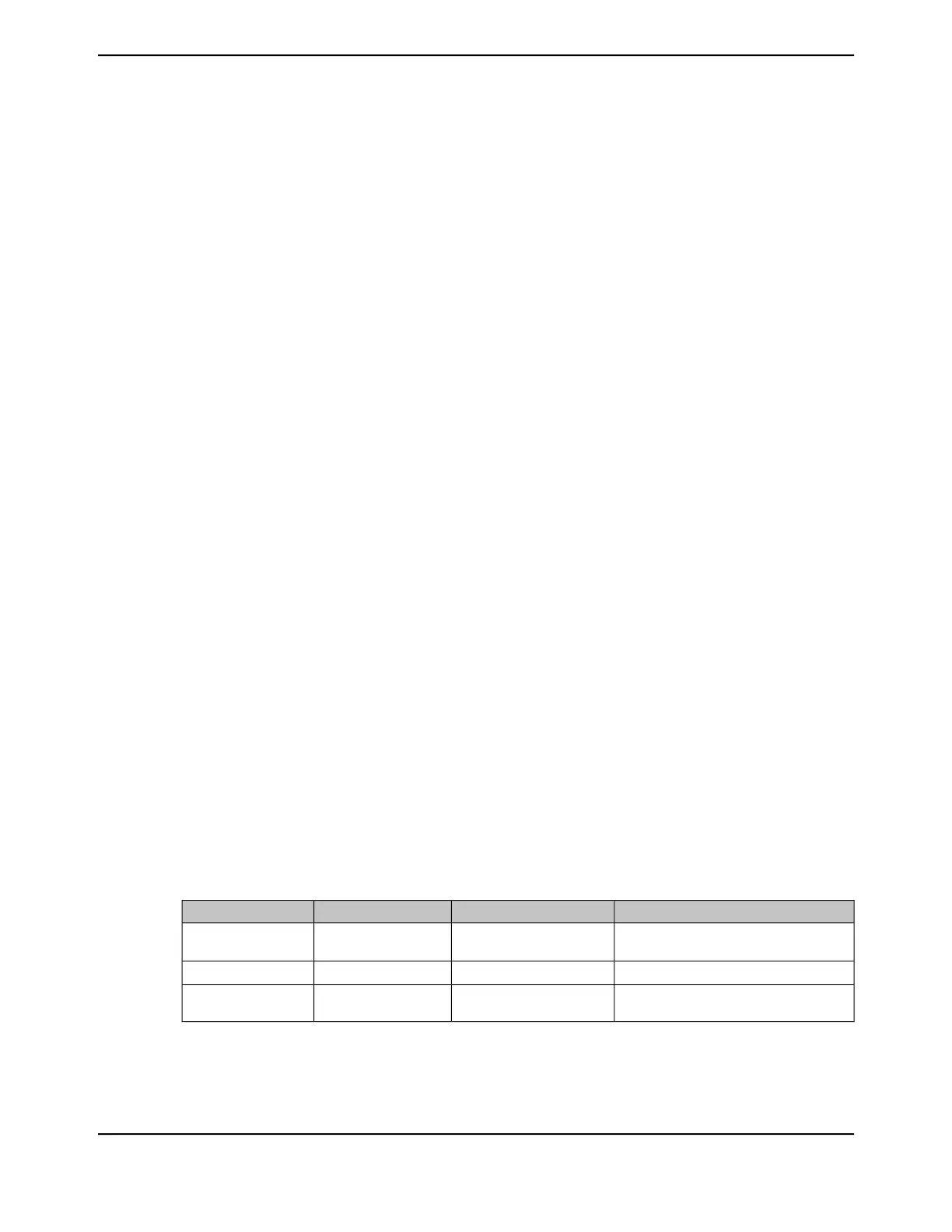

programmed with the divisor bit field DSSYSYDIV to modify the clock source frequency. Table

5-5 on page 235 shows the different system clock frequency calculations based on the operation

mode, clock source and PLL encoding.

Table 5-5. System Clock Frequency

Divisor Factors UsedSYSCLK ValueUSEPLL (RSCLKCFG)Clock Mode

PSYSDIV bit field in RSCLKCFG; MINT,

MDIV in PLLFREQ0; Q, N bits in PLLFREQ1

f

VCO

/(PSYSDIV + 1)1Run or Sleep

OSYSDIV bit field in RSCLKCFGf

OSCCLK

/(OSYSDIV + 1)0Run or Sleep

DSSYSDIV bit field in DSCLKCFGf

OSCCLK

/(DSSYSDIV + 1)PLL not enabled in Deep

Sleep

Deep Sleep

235June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...