Register 7: GPTM Raw Interrupt Status (GPTMRIS), offset 0x01C

This register shows the state of the GPTM's internal interrupt signal. These bits are set whether or

not the interrupt is masked in the GPTMIMR register. Each bit can be cleared by writing a 1 to its

corresponding bit in GPTMICR.

Note: The state of the GPTMRIS register is not affected by disabling and then re-enabling the

timer using the TnEN bits in the GPTM Control (GPTMCTL) register. If an application

requires that all or certain status bits should not carry over after re-enabling the timer, then

the appropriate bits in the GPTMRIS register should be cleared using the GPTMICR register

prior to re-enabling the timer. If this is not done, any status bits set in the GPTMRIS register

and unmasked in the GPTMIMR register generate an interrupt once the timer is re-enabled.

GPTM Raw Interrupt Status (GPTMRIS)

16/32-bit Timer 0 base: 0x4003.0000

16/32-bit Timer 1 base: 0x4003.1000

16/32-bit Timer 2 base: 0x4003.2000

16/32-bit Timer 3 base: 0x4003.3000

16/32-bit Timer 4 base: 0x4003.4000

16/32-bit Timer 5 base: 0x4003.5000

16/32-bit Timer 6 base: 0x400E.0000

16/32-bit Timer 7 base: 0x400E.1000

Offset 0x01C

Type RO, reset 0x0000.0000

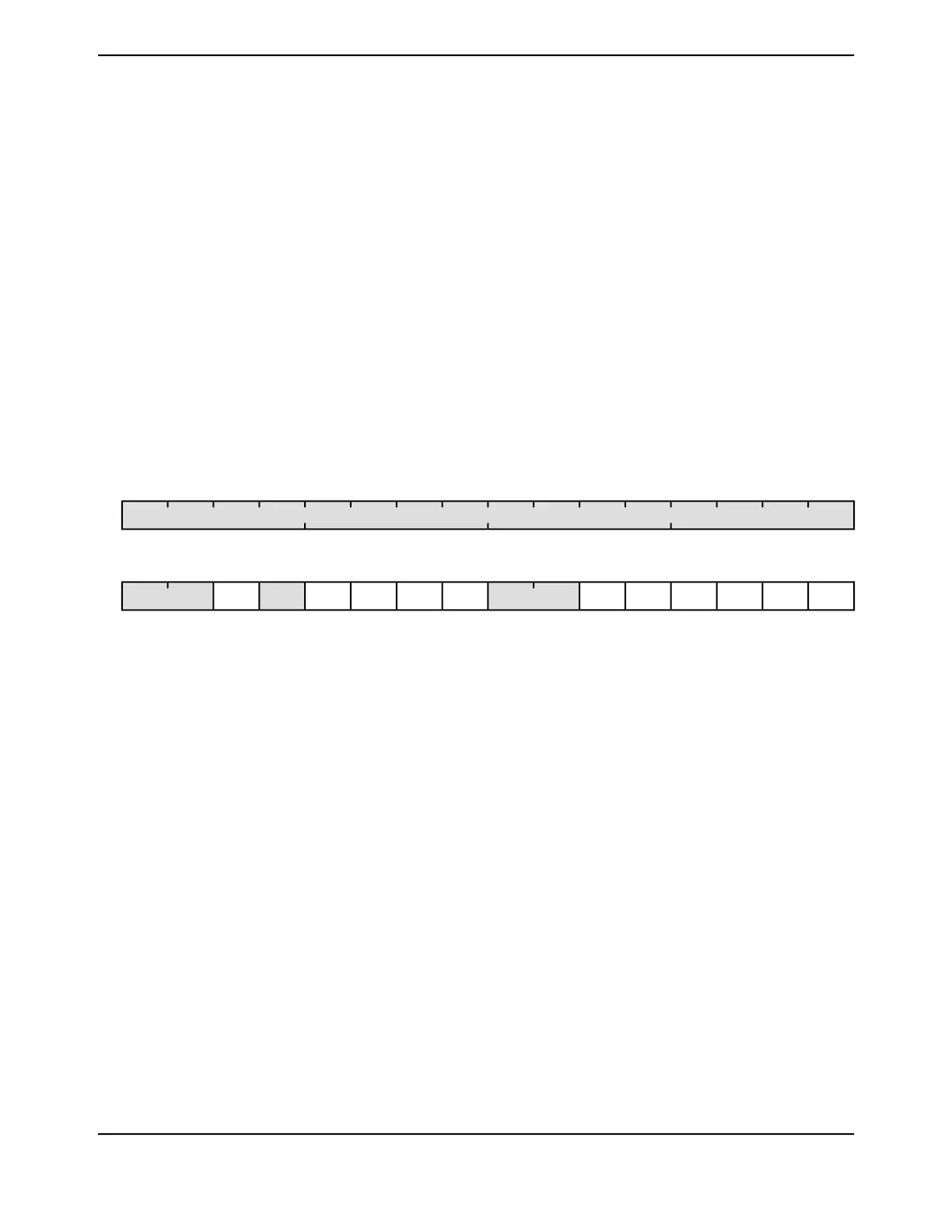

16171819202122232425262728293031

reserved

ROROROROROROROROROROROROROROROROType

0000000000000000Reset

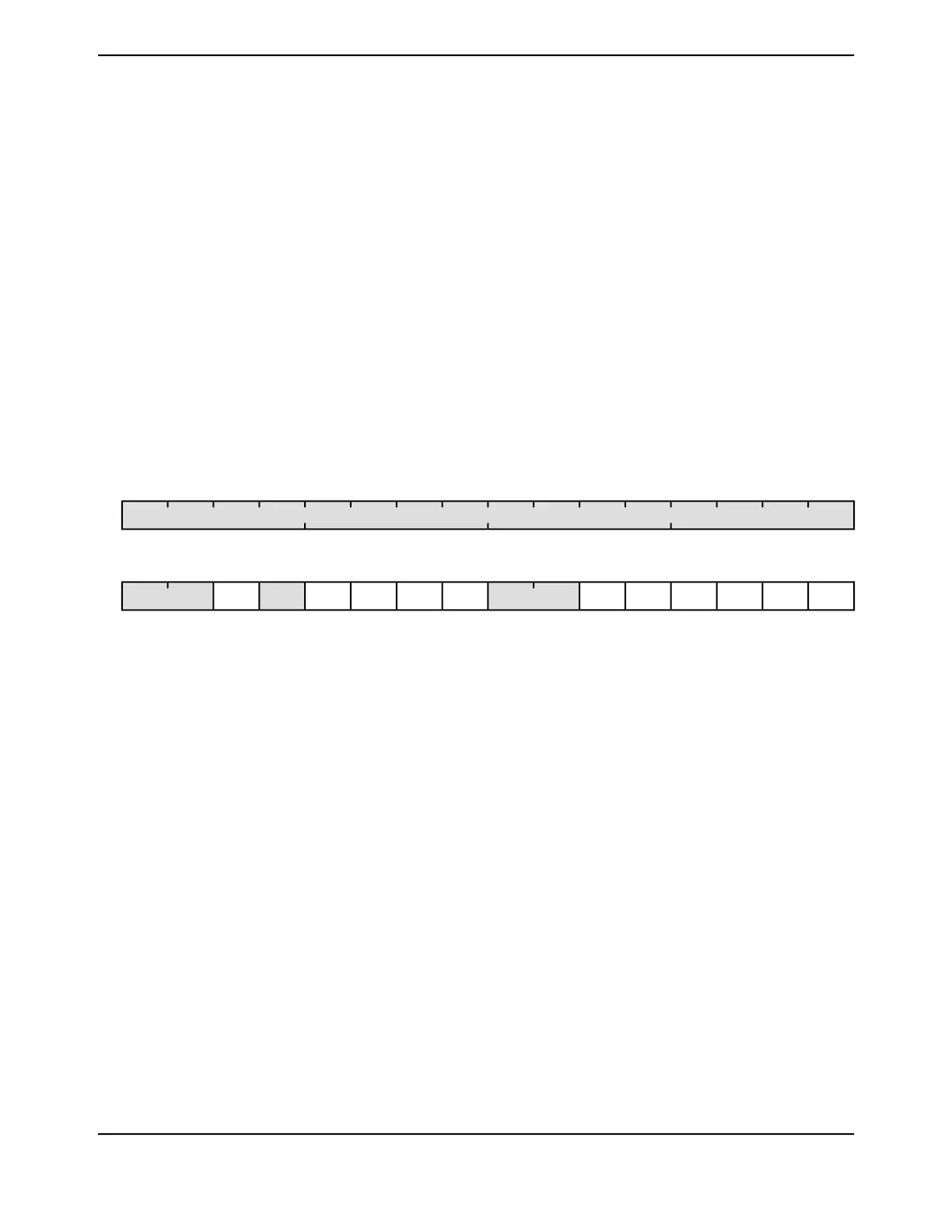

0123456789101112131415

TATORISCAMRISCAERISRTCRISTAMRISDMAARISreservedTBTORISCBMRISCBERISTBMRISreservedDMABRISreserved

ROROROROROROROROROROROROROROROROType

0000000000000000Reset

DescriptionResetTypeNameBit/Field

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x0000ROreserved31:14

GPTM Timer B DMA Done Raw Interrupt Status

DescriptionValue

The Timer B DMA transfer has not completed.0

The Timer B DMA transfer has completed.1

0RODMABRIS13

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x0ROreserved12

June 18, 2014996

Texas Instruments-Production Data

General-Purpose Timers

Loading...

Loading...