Register 58: Ethernet MAC DMA Operation Mode (EMACDMAOPMODE), offset

0xC18

The MAC DMA Operation Mode (EMACDMAOPMODE) register establishes the Transmit and

Receive operating modes and commands. This register should be the last register to be written as

part of the DMA initialization.

Ethernet MAC DMA Operation Mode (EMACDMAOPMODE)

Base 0x400E.C000

Offset 0xC18

Type RW, reset 0x0000.0000

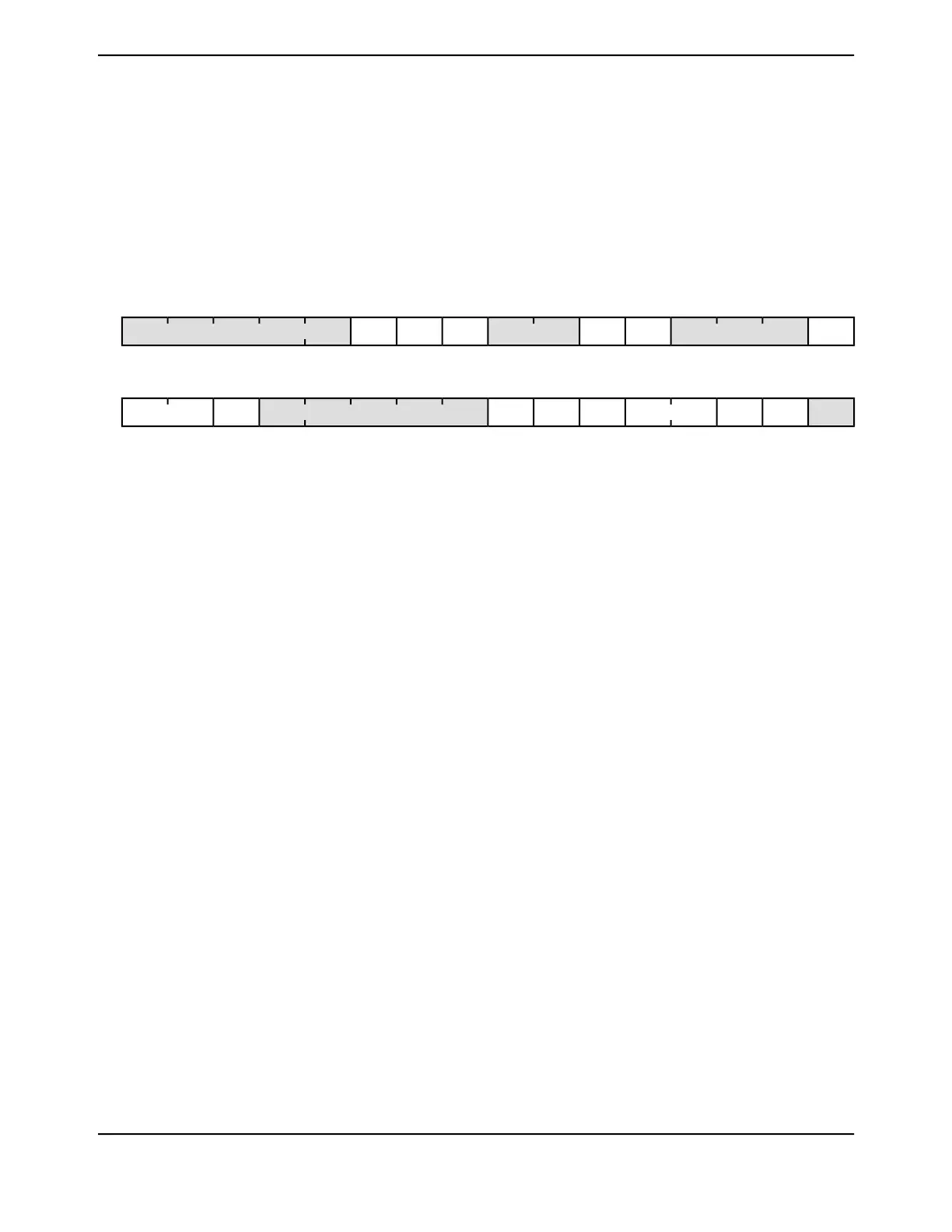

16171819202122232425262728293031

TTCreservedFTFTSFreservedDFFRSFDTreserved

RWRORORORWRWRORORWRWRWROROROROROType

0000000000000000Reset

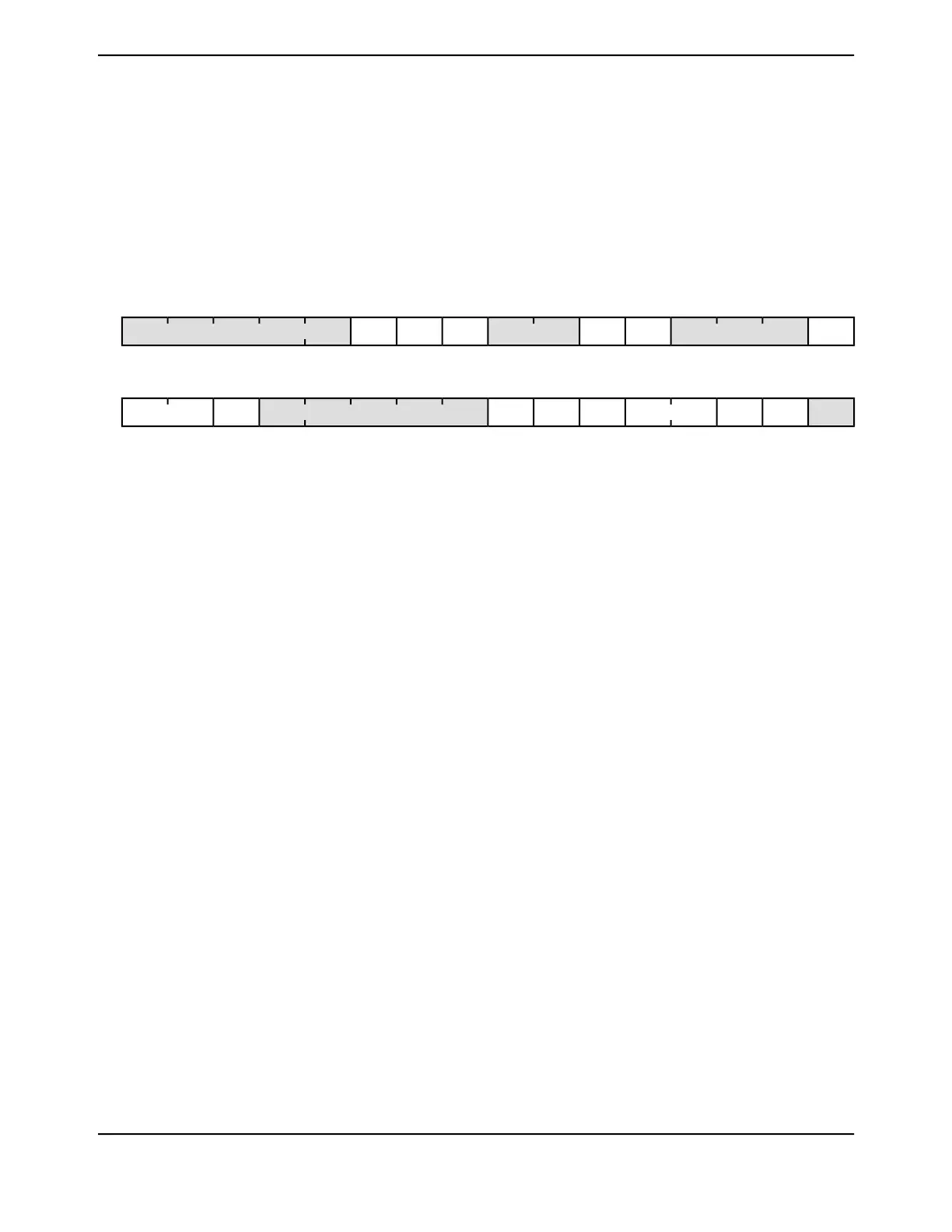

0123456789101112131415

reservedSROSFRTCDGFFUFFEFreservedSTTTC

RORWRWRWRWRWRWRWRORORORORORWRWRWType

0000000000000000Reset

DescriptionResetTypeNameBit/Field

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x0ROreserved31:27

Disable Dropping of TCP/IP Checksum Error Frames

DescriptionValue

All error frames are dropped if the FEF bit is reset.0

The MAC does not drop the frames which only have errors

detected by the Receive Checksum Offload engine. Such frames

do not have any errors (including FCS error) in the Ethernet

frame received by the MAC but have errors only in the

encapsulated payload.

1

0x0RWDT26

Receive Store and Forward

DescriptionValue

The RX FIFO operates in the cut-through mode, subject to the

threshold specified by the RTC bits.

0

The TX/RX Controller reads a frame from the RX FIFO only

after the complete frame has been written to it, ignoring the RTC

bits.

1

0x0RWRSF25

Disable Flushing of Received Frames

DescriptionValue

RX DMA flushes frames based on receive descriptors or buffers.0

The RX DMA does not flush any frames because of the

unavailability of receive descriptors or buffers.

1

0x0RWDFF24

1567June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...