Register 22: Sleep Power Configuration (SLPPWRCFG), offset 0x188

This register provides configuration information for the power control of the SRAM and Flash memory

while in Sleep mode.

Sleep Power Configuration (SLPPWRCFG)

Base 0x400F.E000

Offset 0x188

Type RW, reset 0x0000.0000

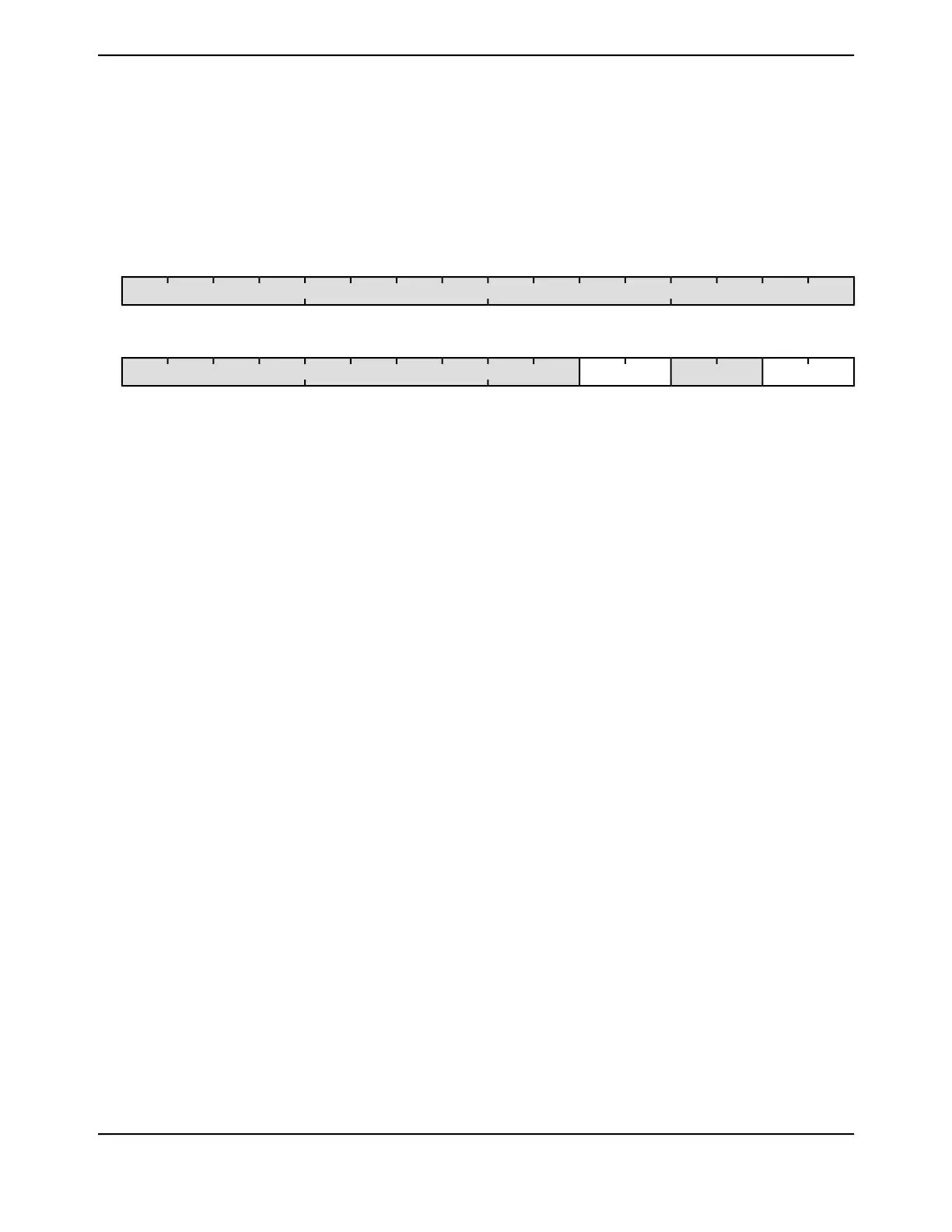

16171819202122232425262728293031

reserved

ROROROROROROROROROROROROROROROROType

0000000000000000Reset

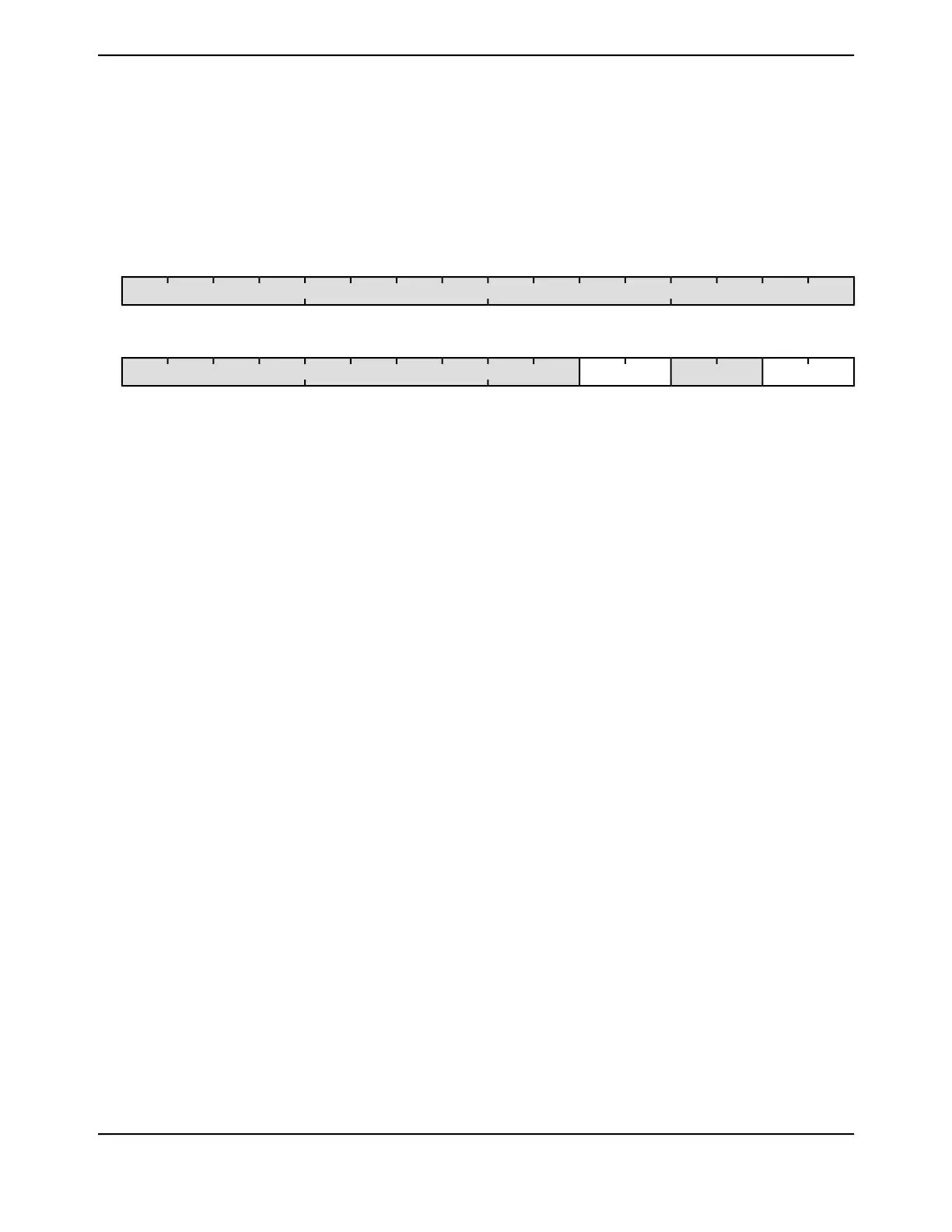

0123456789101112131415

SRAMPMreservedFLASHPMreserved

RWRWRORORWRWROROROROROROROROROROType

0000000000000000Reset

DescriptionResetTypeNameBit/Field

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x0000.00ROreserved31:6

Flash Power Modes

DescriptionValue

Active Mode

Flash memory is not placed in a lower power mode. This mode

provides the fastest time to sleep and wakeup but the highest

power consumption while the microcontroller is in Sleep mode.

0x0

Reserved0x1

Low Power Mode

Flash memory is placed in low power mode. This mode provides

the lowers power consumption but requires more time to come

out of Sleep mode.

0x2

Reserved0x3

0x0RWFLASHPM5:4

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x0ROreserved3:2

295June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...