Register 53: Software Trigger Interrupt (SWTRIG), offset 0xF00

Note: Only privileged software can enable unprivileged access to the SWTRIG register.

Writing an interrupt number to the SWTRIG register generates a Software Generated Interrupt (SGI).

See Table 2-9 on page 116 for interrupt assignments.

When the MAINPEND bit in the Configuration and Control (CFGCTRL) register (see page 175) is

set, unprivileged software can access the SWTRIG register.

Software Trigger Interrupt (SWTRIG)

Base 0xE000.E000

Offset 0xF00

Type WO, reset 0x0000.0000

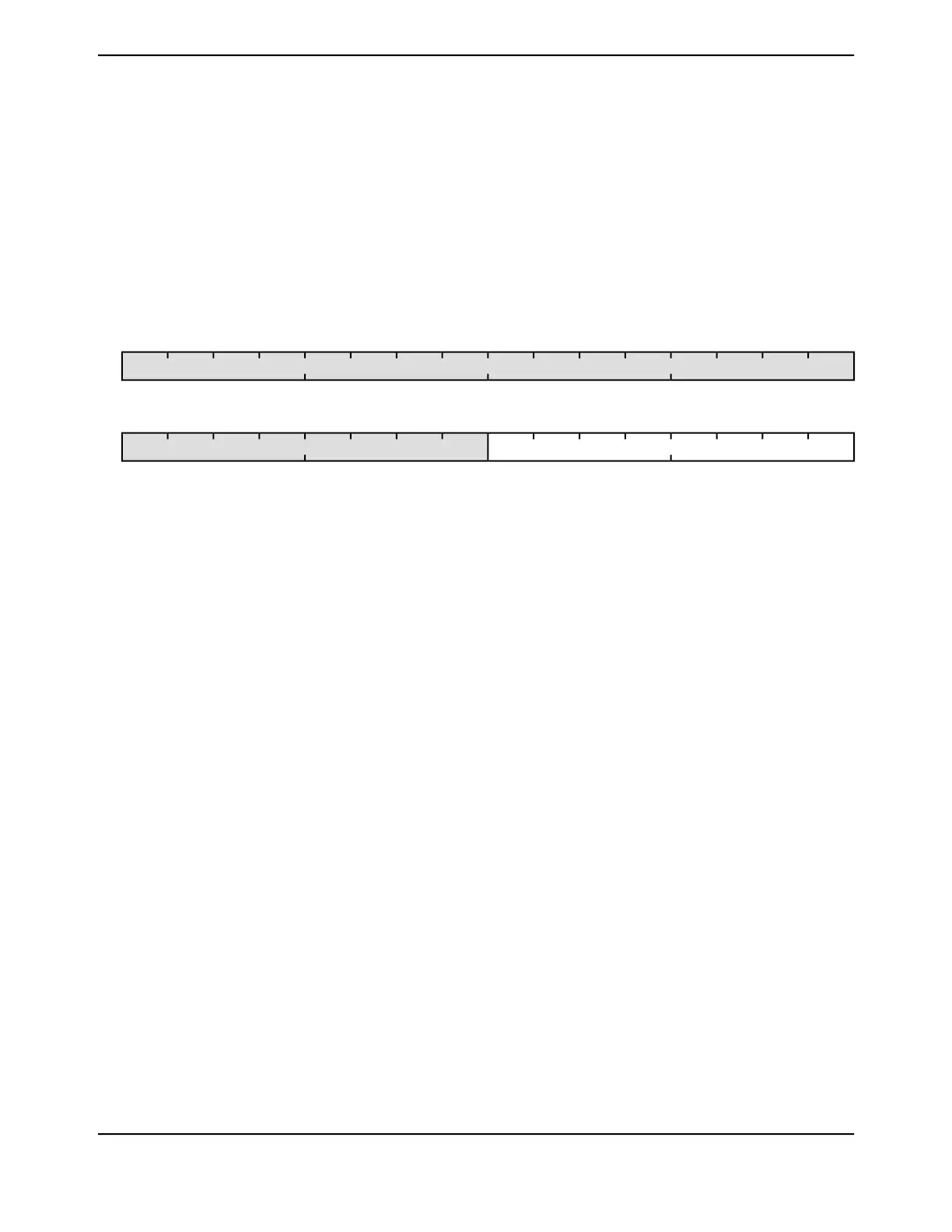

16171819202122232425262728293031

reserved

ROROROROROROROROROROROROROROROROType

0000000000000000Reset

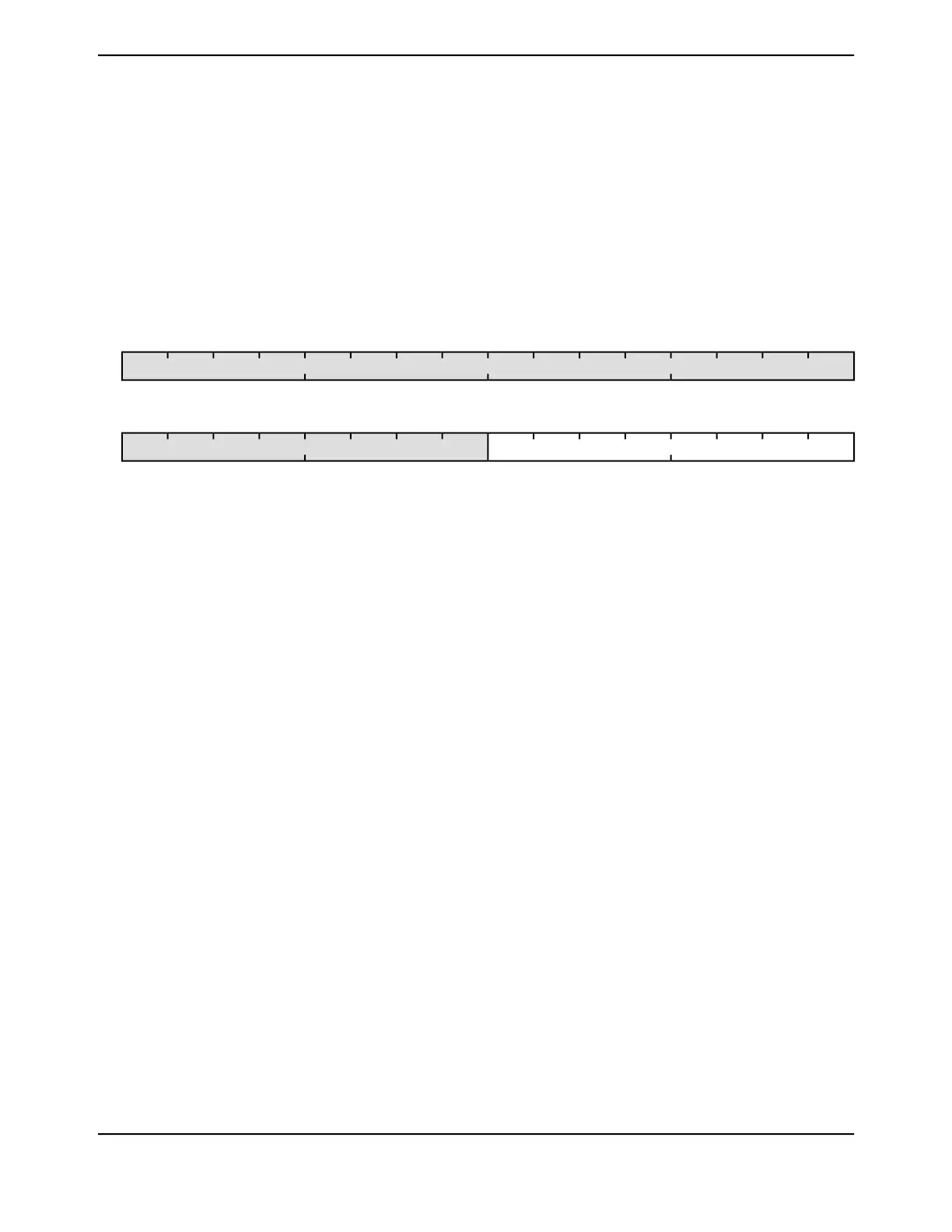

0123456789101112131415

INTIDreserved

WOWOWOWOWOWOWOWOROROROROROROROROType

0000000000000000Reset

DescriptionResetTypeNameBit/Field

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x0000.00ROreserved31:8

Interrupt ID

This field holds the interrupt ID of the required SGI. For example, a value

of 0x3 generates an interrupt on IRQ3.

0x00WOINTID7:0

3.5 System Control Block (SCB) Register Descriptions

This section lists and describes the System Control Block (SCB) registers, in numerical order by

address offset. The SCB registers can only be accessed from privileged mode.

All registers must be accessed with aligned word accesses except for the FAULTSTAT and

SYSPRI1-SYSPRI3 registers, which can be accessed with byte or aligned halfword or word accesses.

The processor does not support unaligned accesses to system control block registers.

163June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...