■ Usage Fault. A usage fault is an exception that occurs because of a fault related to instruction

execution, such as:

– An undefined instruction

– An illegal unaligned access

– Invalid state on instruction execution

– An error on exception return

An unaligned address on a word or halfword memory access or division by zero can cause a

usage fault when the core is properly configured.

■ SVCall. A supervisor call (SVC) is an exception that is triggered by the SVC instruction. In an

OS environment, applications can use SVC instructions to access OS kernel functions and device

drivers.

■ Debug Monitor. This exception is caused by the debug monitor (when not halting). This exception

is only active when enabled. This exception does not activate if it is a lower priority than the

current activation.

■ PendSV. PendSV is a pendable, interrupt-driven request for system-level service. In an OS

environment, use PendSV for context switching when no other exception is active. PendSV is

triggered using the Interrupt Control and State (INTCTRL) register.

■ SysTick. A SysTick exception is an exception that the system timer generates when it reaches

zero when it is enabled to generate an interrupt. Software can also generate a SysTick exception

using the Interrupt Control and State (INTCTRL) register. In an OS environment, the processor

can use this exception as system tick.

■ Interrupt (IRQ). An interrupt, or IRQ, is an exception signaled by a peripheral or generated by

a software request and fed through the NVIC (prioritized). All interrupts are asynchronous to

instruction execution. In the system, peripherals use interrupts to communicate with the processor.

Table 2-9 on page 116 lists the interrupts on the TM4C1294NCPDT controller.

For an asynchronous exception, other than reset, the processor can execute another instruction

between when the exception is triggered and when the processor enters the exception handler.

Privileged software can disable the exceptions that Table 2-8 on page 115 shows as having

configurable priority (see the SYSHNDCTRL register on page 180 and the DIS0 register on page 155).

For more information about hard faults, memory management faults, bus faults, and usage faults,

see “Fault Handling” on page 123.

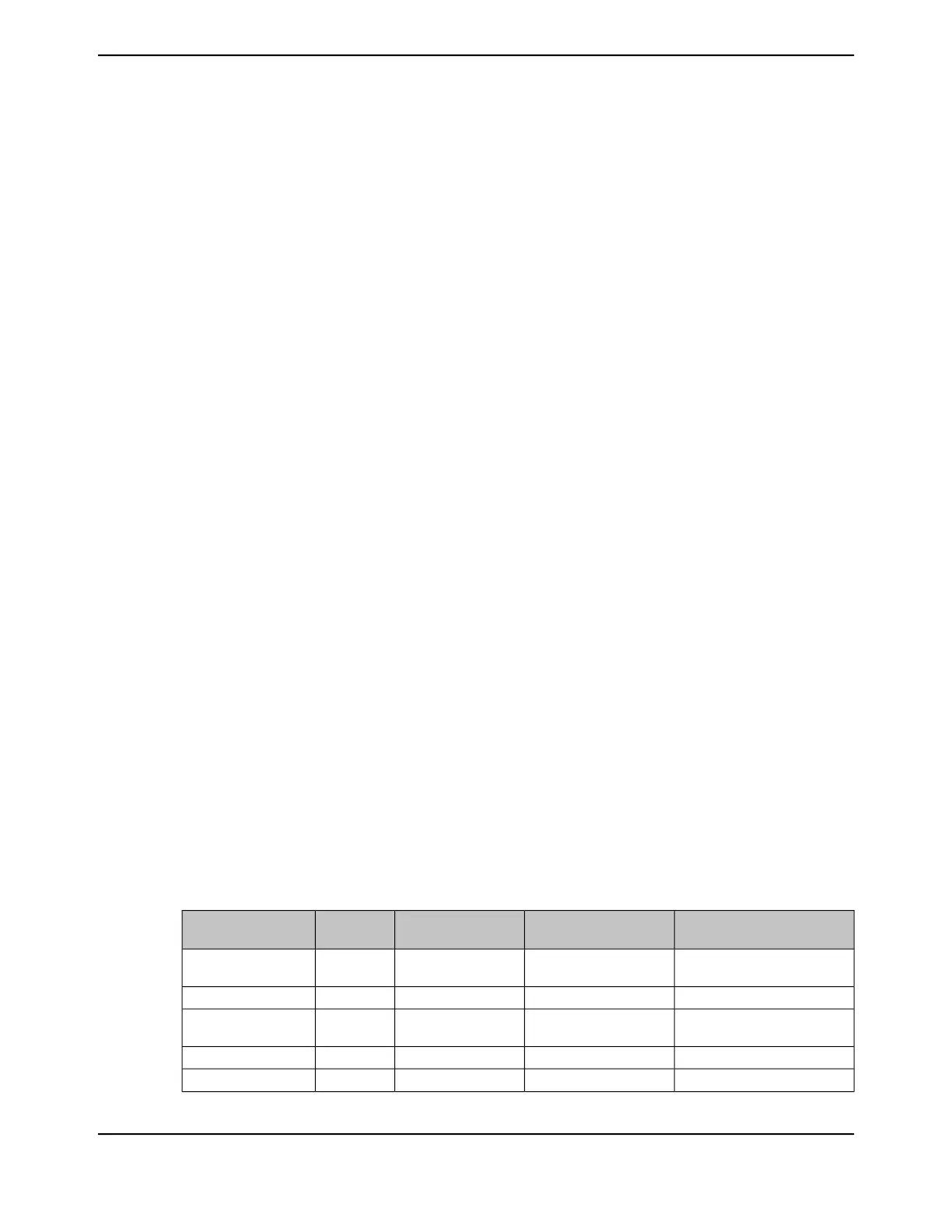

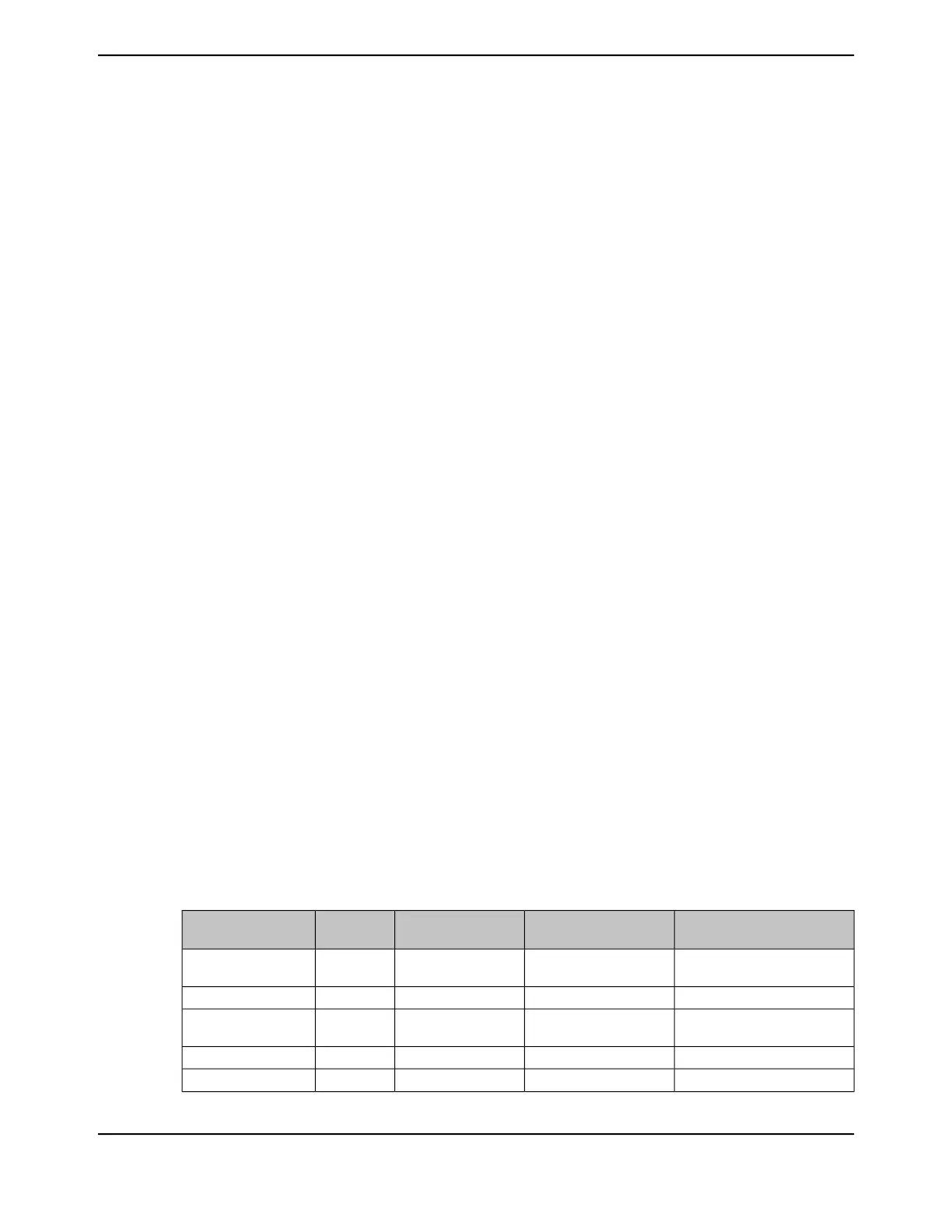

Table 2-8. Exception Types

ActivationVector Address or

Offset

b

Priority

a

Vector

Number

Exception Type

Stack top is loaded from the first

entry of the vector table on reset.

0x0000.0000-0-

Asynchronous0x0000.0004-3 (highest)1Reset

Asynchronous0x0000.0008-22Non-Maskable Interrupt

(NMI)

-0x0000.000C-13Hard Fault

Synchronous0x0000.0010programmable

c

4Memory Management

115June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...