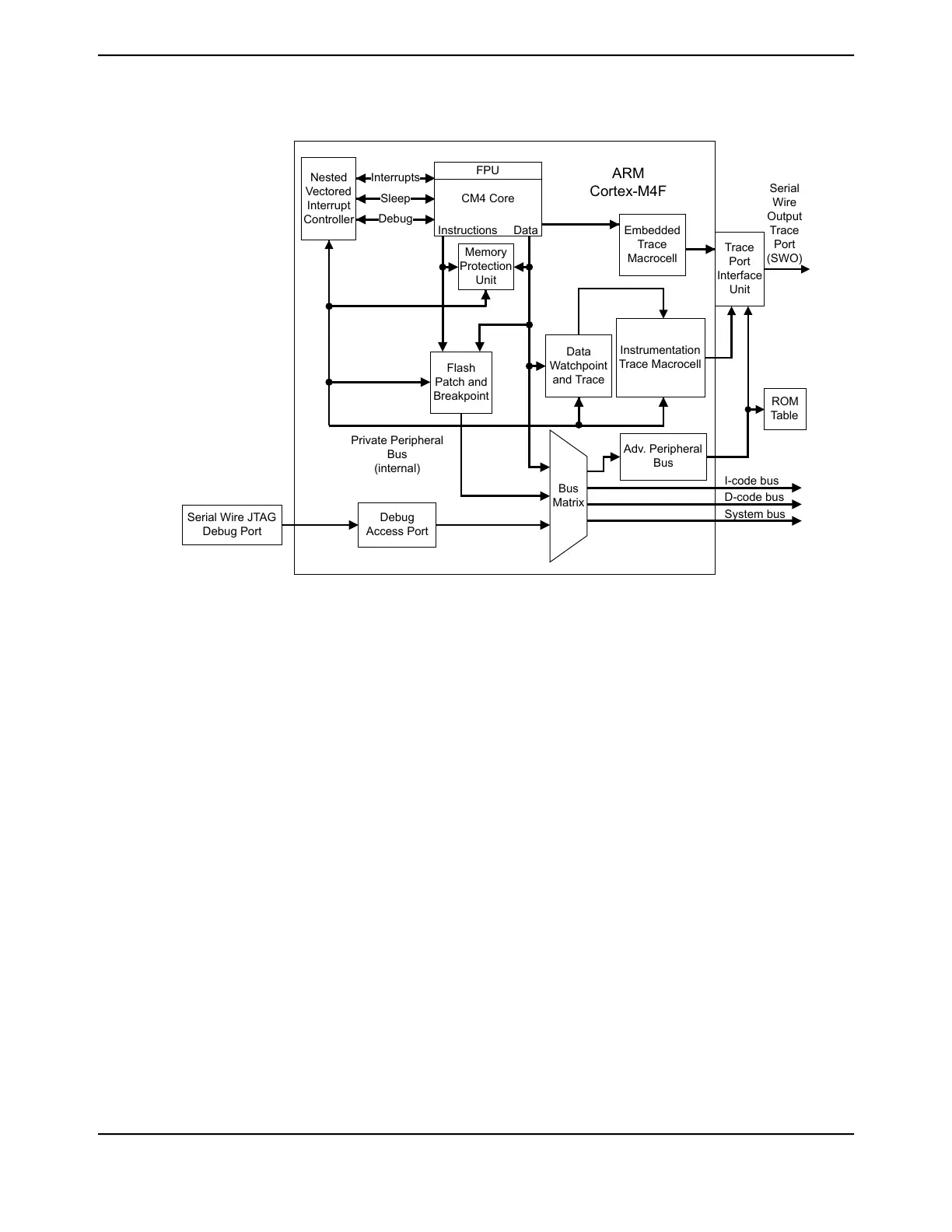

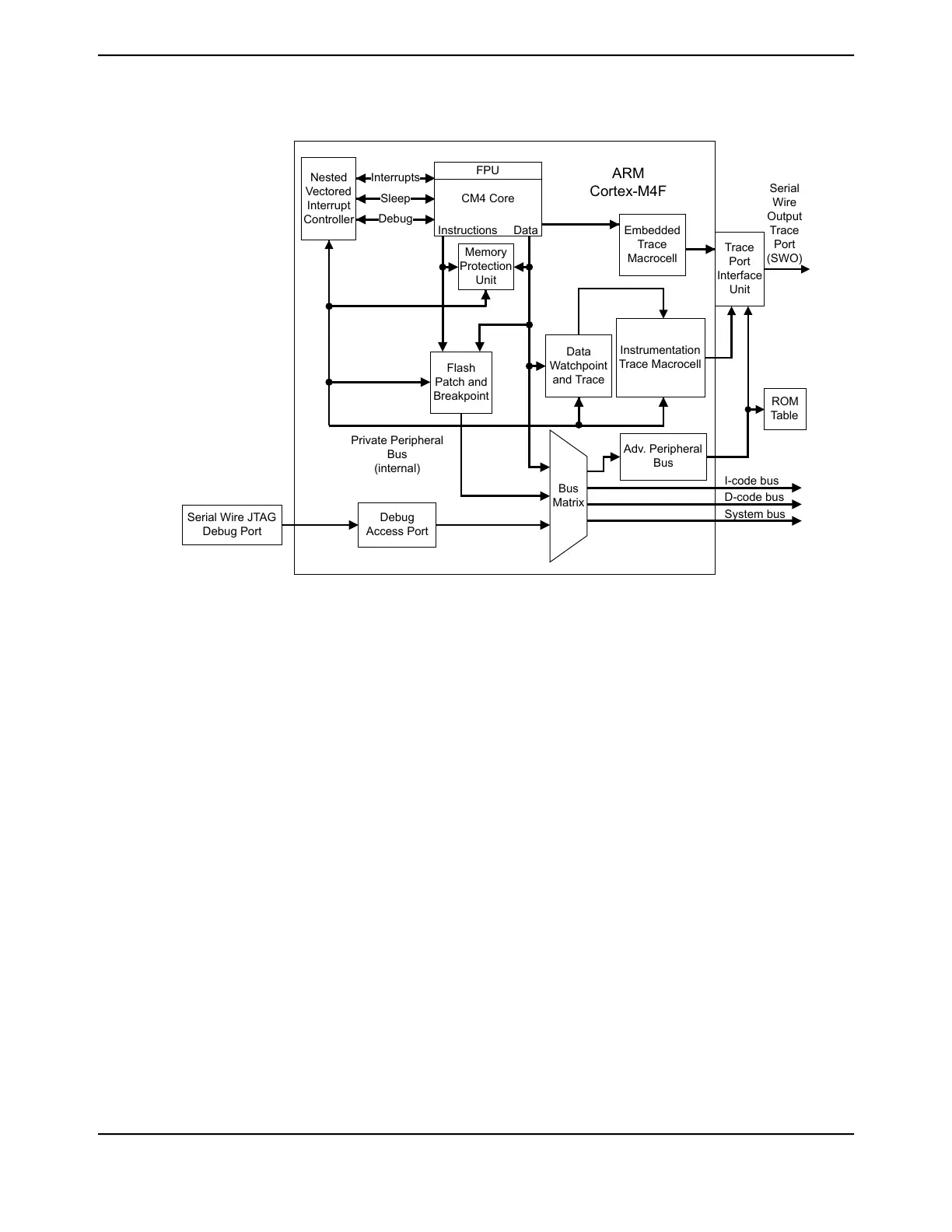

Figure 2-1. CPU Block Diagram

Private Peripheral

Bus

(internal)

Data

Watchpoint

and Trace

Interrupts

Debug

Sleep

Instrumentation

Trace Macrocell

Trace

Port

Interface

Unit

CM4 Core

Instructions Data

Flash

Patch and

Breakpoint

Memory

Protection

Unit

Debug

Access Port

Nested

Vectored

Interrupt

Controller

Serial Wire JTAG

Debug Port

Bus

Matrix

Adv. Peripheral

Bus

I-code bus

D-code bus

System bus

ROM

Table

Serial

Wire

Output

Trace

Port

(SWO)

ARM

Cortex-M4F

FPU

Embedded

Trace

Macrocell

2.2 Overview

2.2.1 System-Level Interface

The Cortex-M4F processor provides multiple interfaces using AMBA® technology to provide

high-speed, low-latency memory accesses. The core supports unaligned data accesses and

implements atomic bit manipulation that enables faster peripheral controls, system spinlocks, and

thread-safe Boolean data handling.

The Cortex-M4F processor has a memory protection unit (MPU) that provides fine-grain memory

control, enabling applications to implement security privilege levels and separate code, data and

stack on a task-by-task basis.

2.2.2 Integrated Configurable Debug

The Cortex-M4F processor implements a complete hardware debug solution, providing high system

visibility of the processor and memory through either a traditional JTAG port or a 2-pin Serial Wire

Debug (SWD) port that is ideal for microcontrollers and other small package devices. The Tiva™

C Series implementation replaces the ARM SW-DP and JTAG-DP with the ARM

CoreSight™-compliant Serial Wire JTAG Debug Port (SWJ-DP) interface. The SWJ-DP interface

combines the SWD and JTAG debug ports into one module. See the ARM® Debug Interface V5

Architecture Specification for details on SWJ-DP.

For system trace, the processor integrates an Instrumentation Trace Macrocell (ITM) alongside data

watchpoints and a profiling unit. To enable simple and cost-effective profiling of the system trace

events, a Serial Wire Viewer (SWV) can export a stream of software-generated messages, data

trace, and profiling information through a single pin.

June 18, 201482

Texas Instruments-Production Data

The Cortex-M4F Processor

Loading...

Loading...