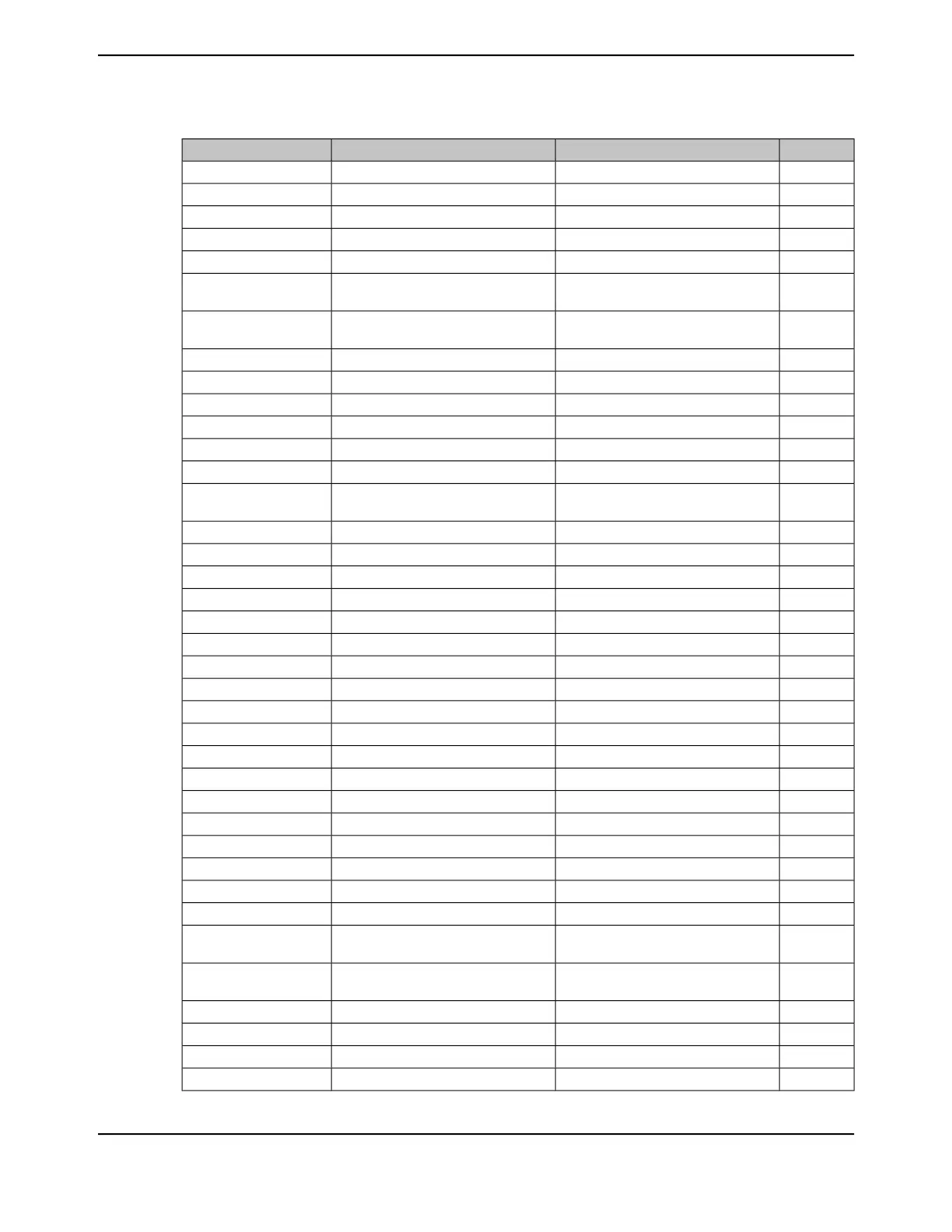

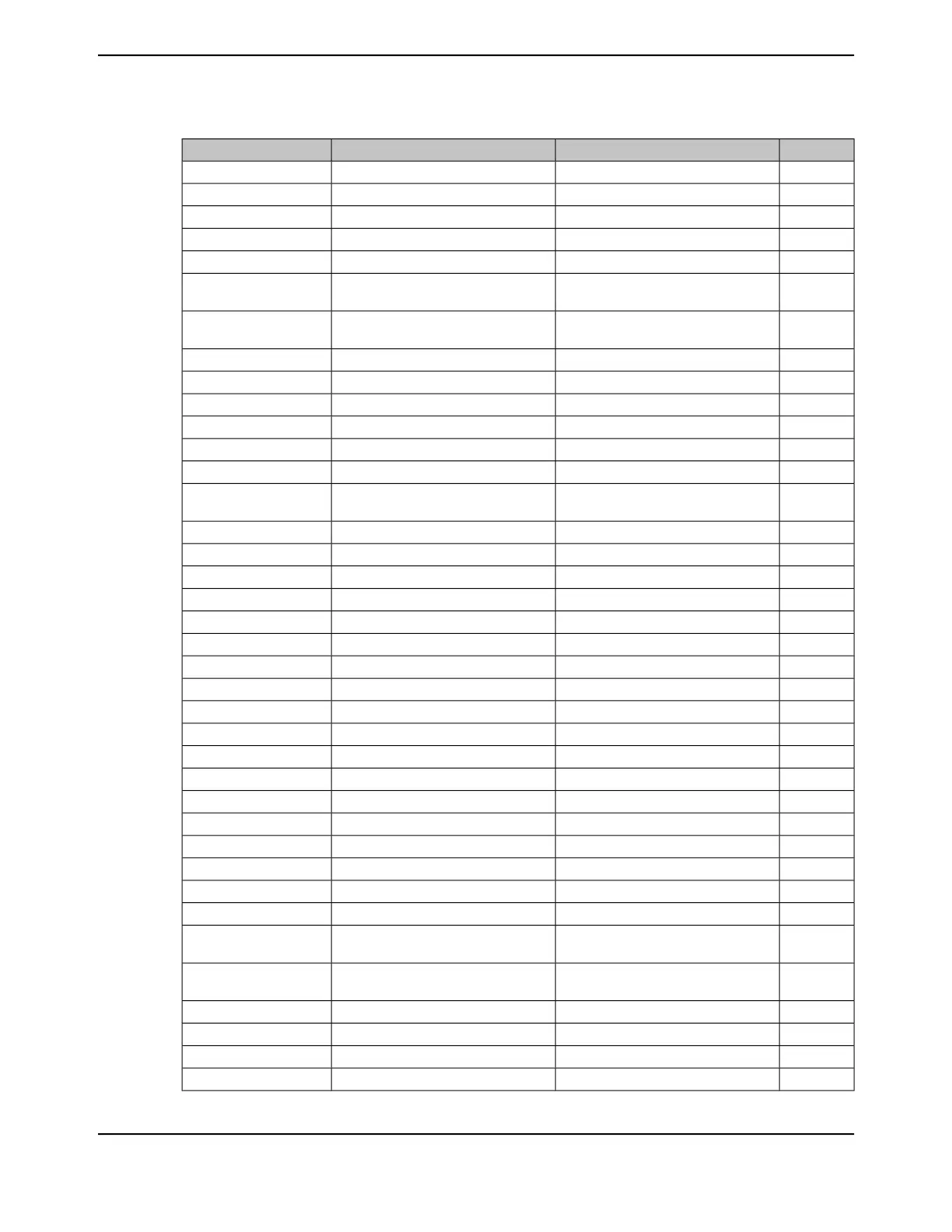

Table 2-13. Cortex-M4F Instruction Summary (continued)

FlagsBrief DescriptionOperandsMnemonic

-Compare and branch if zeroRn, labelCBZ

-Clear exclusive-CLREX

-Count leading zerosRd, RmCLZ

N,Z,C,VCompare negativeRn, Op2CMN

N,Z,C,VCompareRn, Op2CMP

-Change processor state, disable

interrupts

iCPSID

-Change processor state, enable

interrupts

iCPSIE

-Data memory barrier-DMB

-Data synchronization barrier-DSB

N,Z,CExclusive OR{Rd,} Rn, Op2EOR, EORS

-Instruction synchronization barrier-ISB

-If-Then condition block-IT

-Load multiple registers, increment afterRn{!}, reglistLDM

-Load multiple registers, decrement

before

Rn{!}, reglistLDMDB, LDMEA

-Load multiple registers, increment afterRn{!}, reglistLDMFD, LDMIA

-Load register with wordRt, [Rn, #offset]LDR

-Load register with byteRt, [Rn, #offset]LDRB, LDRBT

-Load register with two bytesRt, Rt2, [Rn, #offset]LDRD

-Load register exclusiveRt, [Rn, #offset]LDREX

-Load register exclusive with byteRt, [Rn]LDREXB

-Load register exclusive with halfwordRt, [Rn]LDREXH

-Load register with halfwordRt, [Rn, #offset]LDRH, LDRHT

-Load register with signed byteRt, [Rn, #offset]LDRSB, LDRSBT

-Load register with signed halfwordRt, [Rn, #offset]LDRSH, LDRSHT

-Load register with wordRt, [Rn, #offset]LDRT

N,Z,CLogical shift leftRd, Rm, <Rs|#n>LSL, LSLS

N,Z,CLogical shift rightRd, Rm, <Rs|#n>LSR, LSRS

-Multiply with accumulate, 32-bit resultRd, Rn, Rm, RaMLA

-Multiply and subtract, 32-bit resultRd, Rn, Rm, RaMLS

N,Z,CMoveRd, Op2MOV, MOVS

N,Z,CMove 16-bit constantRd, #imm16MOV, MOVW

-Move topRd, #imm16MOVT

-Move from special register to general

register

Rd, spec_regMRS

N,Z,C,VMove from general register to special

register

spec_reg, RmMSR

N,ZMultiply, 32-bit result{Rd,} Rn, RmMUL, MULS

N,Z,CMove NOTRd, Op2MVN, MVNS

-No operation-NOP

N,Z,CLogical OR NOT{Rd,} Rn, Op2ORN, ORNS

June 18, 2014128

Texas Instruments-Production Data

The Cortex-M4F Processor

Loading...

Loading...