If it is necessary to keep the MOSC powered on during automatic (deep-sleep) or accidental power

down, then the MOSCDPD bit should be set to 0x1. Otherwise, if the MOSCDPD bit is set to 0x0, the

MOSC is powered off when deep-sleep is entered or automatic power down occurs. The following

table describes the relationship between the PWRDN bit in the MOSCCTL register and the MOSCDPD

bit in the DSCLKCFG register:

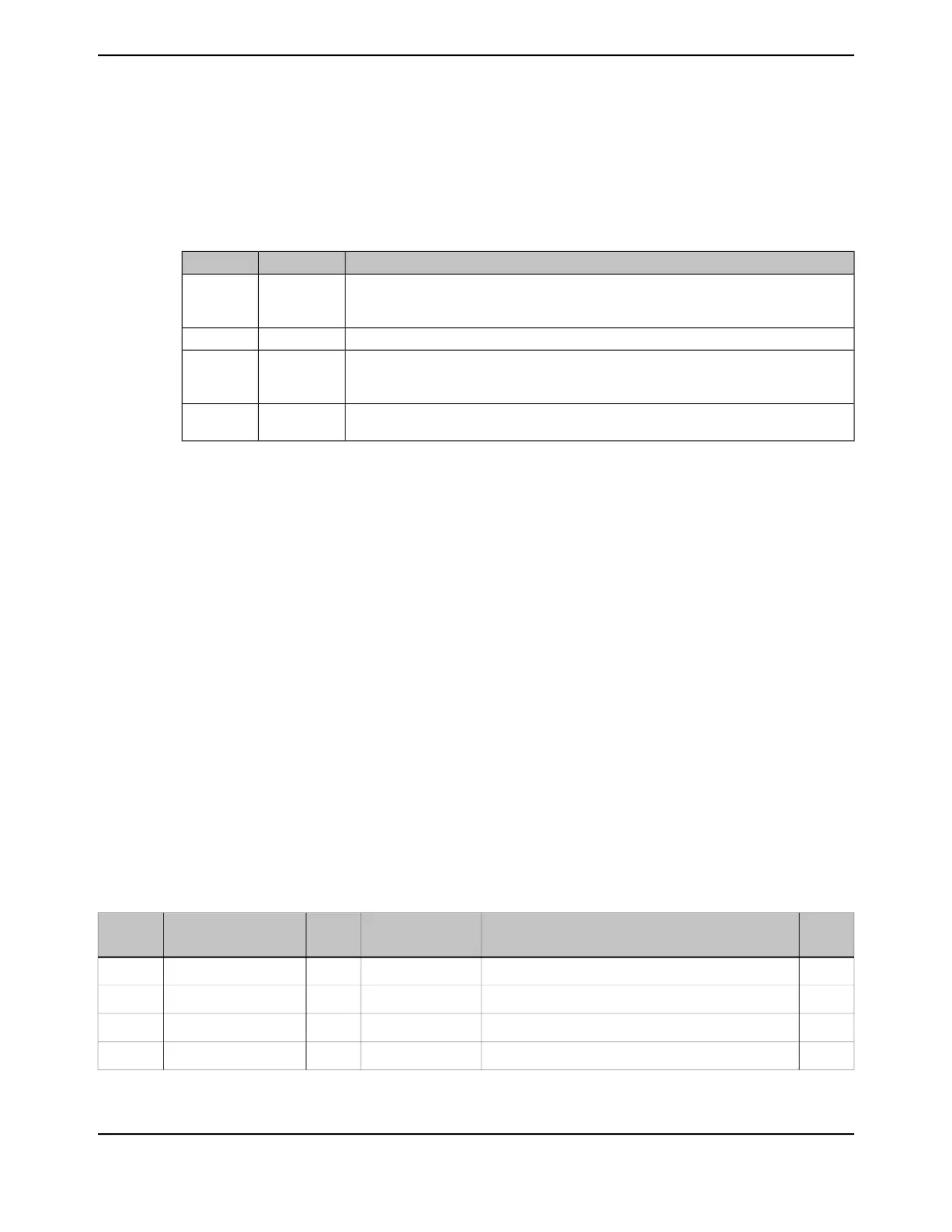

Table 5-10. MOSC Configurations

ResultMOSCDPD fieldPWRDN bit

MOSC is powered ON in run and sleep modes, but is disabled in accidental power down,

when the PWRDN bit is set in the MOSCCTL register, or in deep-sleep mode only if it is not

the deep-sleep clock source (DSOSCSRC !==0x3).

00

MOSC is powered and running in run, sleep and deep-sleep modes.10

MOSC is powered off, and does not run in any mode. Please note, that in this configuration,

when the MOSC is disabled, the MOSC must not be chosen as a clock source or indeterminate

results occur.

01

MOSC runs and does not disable itself in run, sleep, and deep-sleep modes regardless of

the fact that the PWRDN bit is set.

11

Note: The MOSCDPD bit has an effect in all modes of operation

To change the system clock frequency by changing its corresponding PSYSDIV or OSYSDIV value,

a user must ensure timing parameters to memory are within range through the following steps:

1. If the change in system clock frequency changes the operational range of the timing parameters,

the MEMTIM0 register must be updated. If so, write the timing configuration register, MEMTIM0,

setting the value to correspond to the final SYSCLK frequency (f

VCO

/new SYSDIV or f

OSC

).

Otherwise the MEMTIM0 register should not be changed.

2. Write the RSCLKCFG register's PSYSDIV value and MEMTIMU bit if the MEMTIM0 register is

updated in the first step. The new SYSDIV is now in effect.

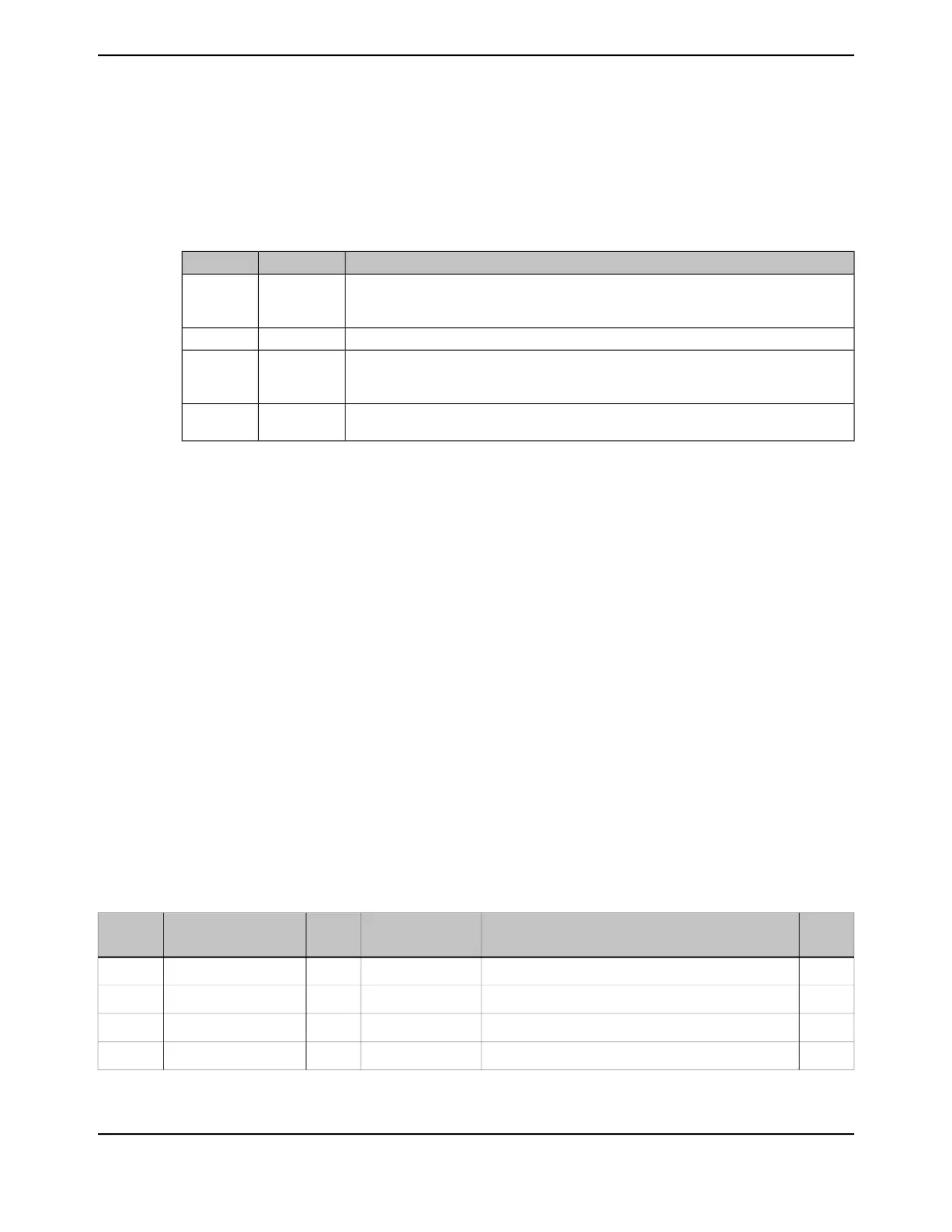

5.4 Register Map

Table 5-11 on page 247 lists the System Control registers, grouped by function. The offset listed is

a hexadecimal increment to the register's address, relative to the System Control base address of

0x400F.E000.

Note: Spaces in the System Control register space that are not used are reserved for future or

internal use. Software should not modify any reserved memory address.

Additional Flash and ROM registers defined in the System Control register space are

described in the “Internal Memory” on page 600.

Table 5-11. System Control Register Map

See

page

DescriptionResetTypeNameOffset

255Device Identification 0-RODID00x000

257Device Identification 10x101F.C06ERODID10x004

259Power-Temp Brown Out Control0x0000.0003RWPTBOCTL0x038

261Raw Interrupt Status0x0000.0000RORIS0x050

247June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...