Register 57: Vector Table Offset (VTABLE), offset 0xD08

Note: This register can only be accessed from privileged mode.

The VTABLE register indicates the offset of the vector table base address from memory address

0x0000.0000.

Vector Table Offset (VTABLE)

Base 0xE000.E000

Offset 0xD08

Type RW, reset 0x0000.0000

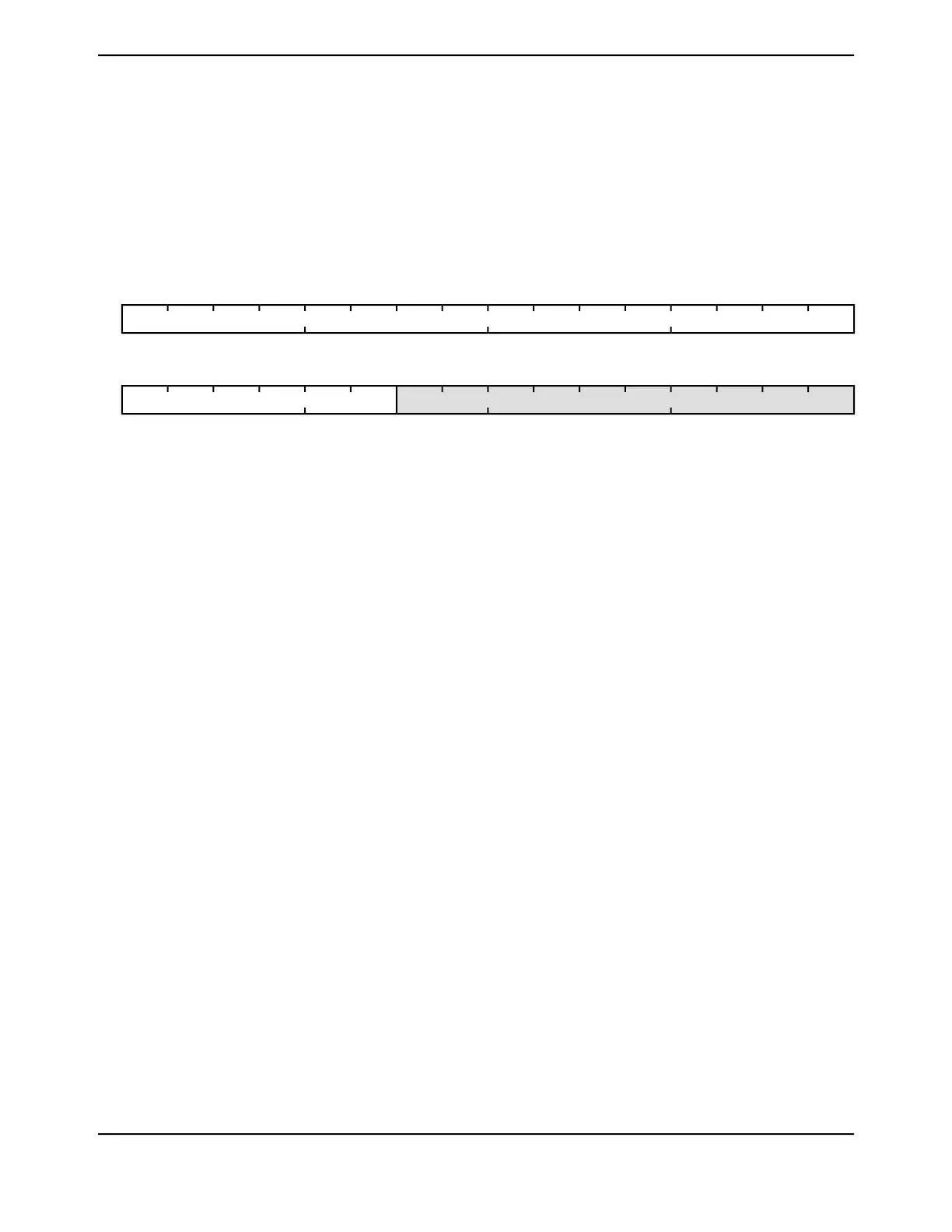

16171819202122232425262728293031

OFFSET

RWRWRWRWRWRWRWRWRWRWRWRWRWRWRWRWType

0000000000000000Reset

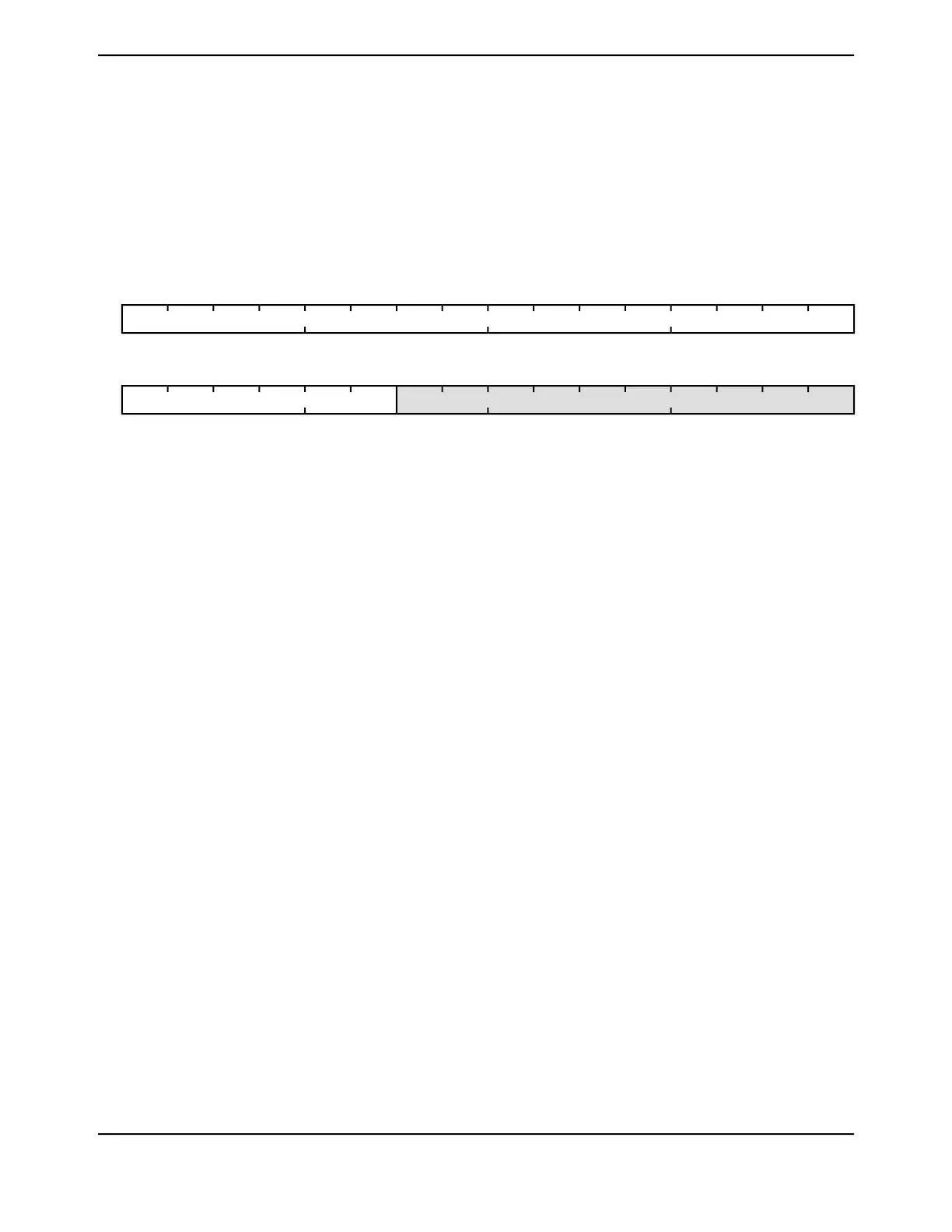

0123456789101112131415

reservedOFFSET

RORORORORORORORORORORWRWRWRWRWRWType

0000000000000000Reset

DescriptionResetTypeNameBit/Field

Vector Table Offset

When configuring the OFFSET field, the offset must be aligned to the

number of exception entries in the vector table. Because there are 112

interrupts, the offset must be aligned on a 1024-byte boundary.

0x000.00RWOFFSET31:10

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x00ROreserved9:0

June 18, 2014170

Texas Instruments-Production Data

Cortex-M4 Peripherals

Loading...

Loading...