Register 160: EEPROM Power Control (PCEEPROM), offset 0x958

Important: The EEPROM module does not currently provide the ability to respond to the power

down request. Setting a bit in this register has no effect on power consumption. This

register is defined for future software compatibility.

The PCEEPROM register controls the power applied to the EEPROM module. The function of this

bit depends on the current state of the device (Run, Sleep or Deep-Sleep mode) and value of the

corresponding bits in the RCGCEEPROM, SCGCEEPROM and DCGCEEPROM registers. If the

Rn, Sn, or Dn bit of the respective RCGCEEPROM, SCGCEEPROM and DCGCEEPROM registers

is 1 and the device is in that mode, the module is powered and receives a clock irrespective of what

the corresponding Pn bit in the PCEEPROM register is.

However, if the Rn, Sn, or Dn bit of the respective RCGCEEPROM, SCGCEEPROM and

DCGCEEPROM registers is 0 and the device is in that mode, then the module behaves differently

depending on the value of the corresponding Pn bit in the PCEEPROM register. In this case, when

the Pn bit is clear the module is not powered and does not receive a clock. If the Pn bit is set, the

module is powered but does not receive a clock. The table below details the differences.

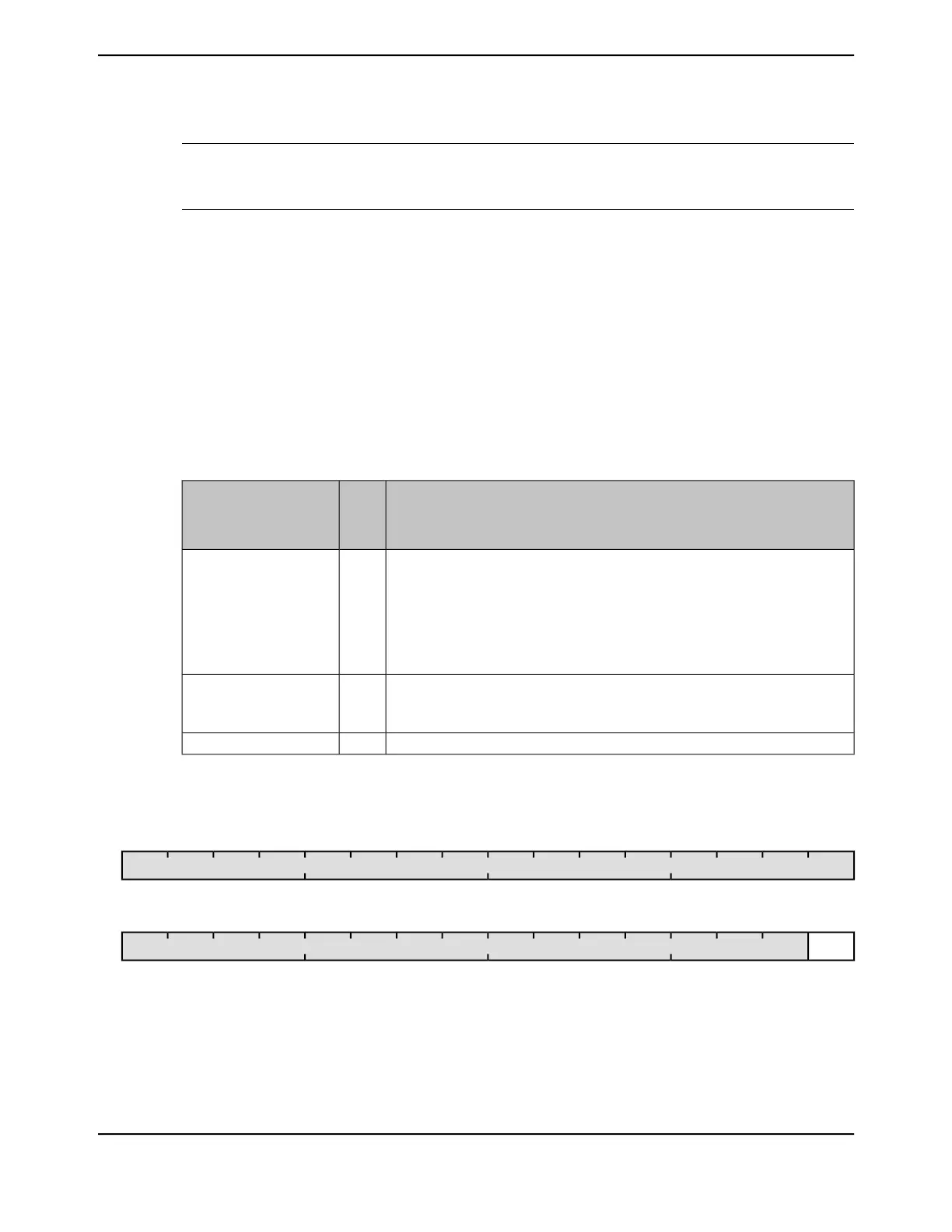

Table 5-32. Module Power Control

DescriptionPnRn, Sn or Dn Value in

Respective RCGCx,

SCGCx, or DCGCx

Register

Module is not powered and does not receive a clock. In this case, the peripheral's

state is not retained.

This is the lowest power consumption state of any peripheral since it consumes no

dynamic nor leakage current. Hardware should perform a peripheral reset if the active

mode changes and the RCGCx, SCGCx, or DCGCx register is a 1 or the P0 bit is

changed to a 1.

Software must re-initialize the peripheral when re-enabled due to the loss of state.

00

Module is powered, but does not receive a clock.

In this case, the peripheral is inactive. This is the second-lowest power consumption

of any peripheral since it consumes only leakage current.

10

Module is powered and receives a clock.X1

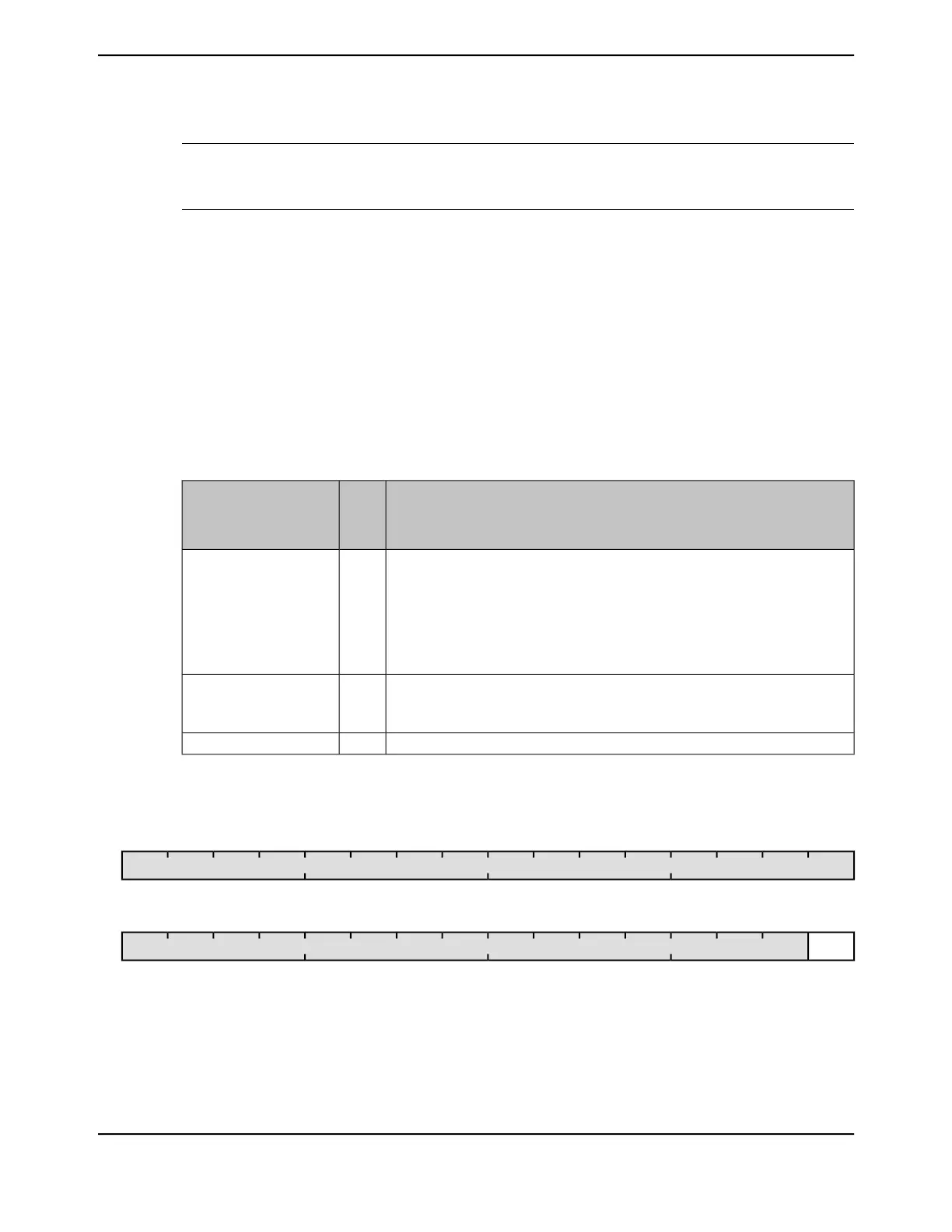

EEPROM Power Control (PCEEPROM)

Base 0x400F.E000

Offset 0x958

Type RW, reset 0x0000.0001

16171819202122232425262728293031

reserved

ROROROROROROROROROROROROROROROROType

0000000000000000Reset

0123456789101112131415

P0reserved

RWROROROROROROROROROROROROROROROType

1000000000000000Reset

DescriptionResetTypeNameBit/Field

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0ROreserved31:1

June 18, 2014490

Texas Instruments-Production Data

System Control

Loading...

Loading...