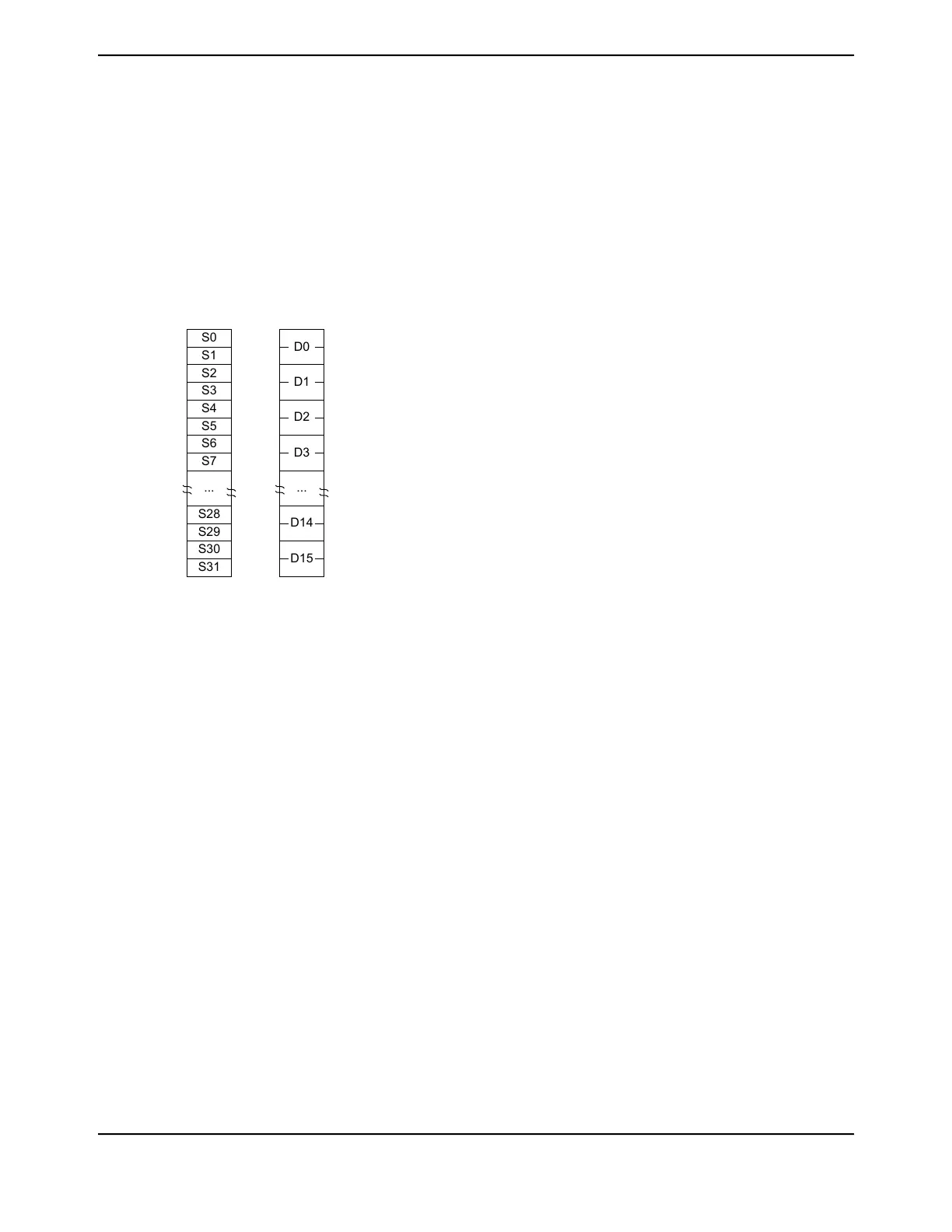

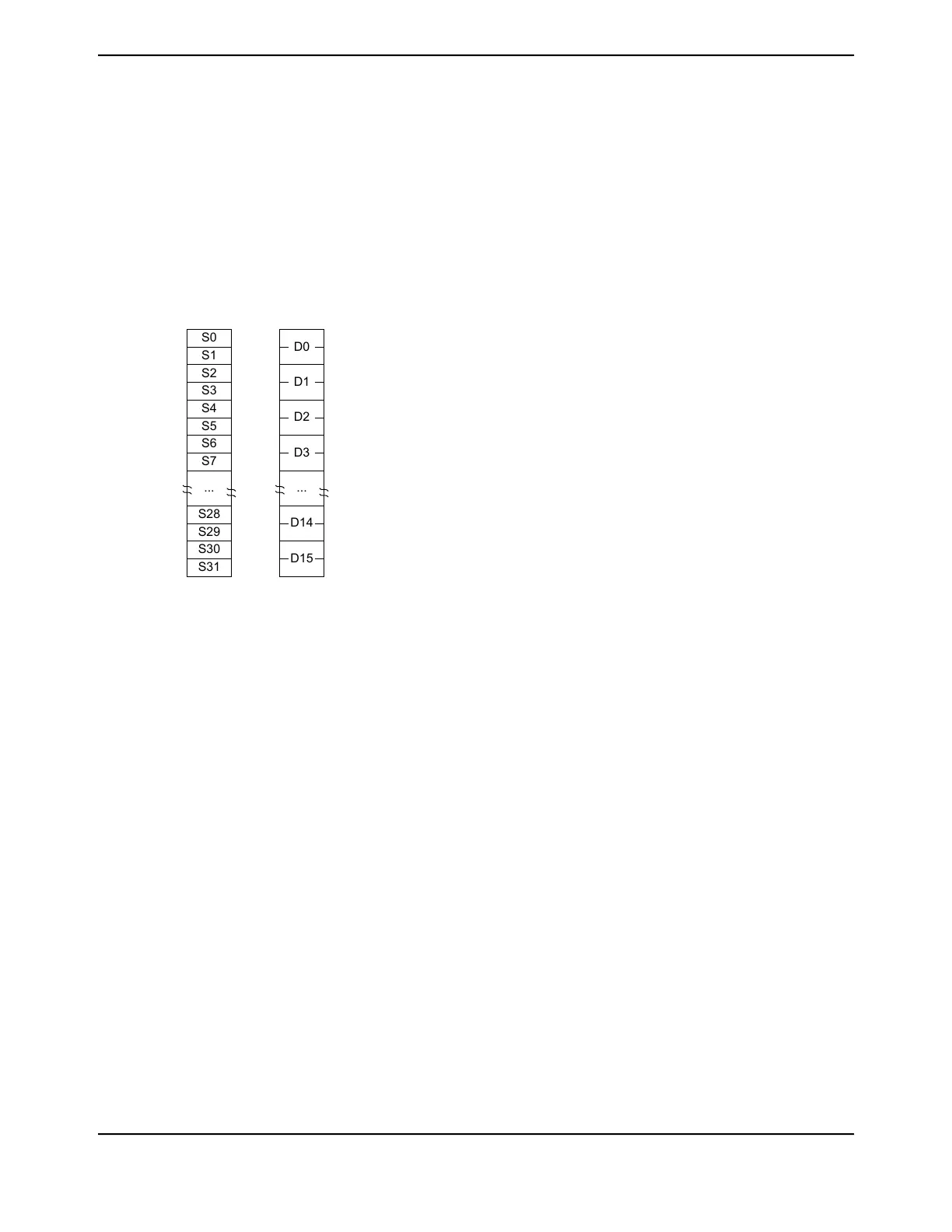

3.1.5.1 FPU Views of the Register Bank

The FPU provides an extension register file containing 32 single-precision registers. These can be

viewed as:

■ Sixteen 64-bit doubleword registers, D0-D15

■ Thirty-two 32-bit single-word registers, S0-S31

■ A combination of registers from the above views

Figure 3-2. FPU Register Bank

...

D0

D1

D2

D3

D14

D15

S0

S1

S2

S3

S4

S5

S6

S7

S28

S29

S30

S31

...

The mapping between the registers is as follows:

■ S<2n> maps to the least significant half of D<n>

■ S<2n+1> maps to the most significant half of D<n>

For example, you can access the least significant half of the value in D6 by accessing S12, and the

most significant half of the elements by accessing S13.

3.1.5.2 Modes of Operation

The FPU provides three modes of operation to accommodate a variety of applications.

Full-Compliance mode. In Full-Compliance mode, the FPU processes all operations according to

the IEEE 754 standard in hardware.

Flush-to-Zero mode. Setting the FZ bit of the Floating-Point Status and Control (FPSC) register

enables Flush-to-Zero mode. In this mode, the FPU treats all subnormal input operands of arithmetic

CDP operations as zeros in the operation. Exceptions that result from a zero operand are signalled

appropriately. VABS, VNEG, and VMOV are not considered arithmetic CDP operations and are not

affected by Flush-to-Zero mode. A result that is tiny, as described in the IEEE 754 standard, where

the destination precision is smaller in magnitude than the minimum normal value before rounding,

is replaced with a zero. The IDC bit in FPSC indicates when an input flush occurs. The UFC bit in

FPSC indicates when a result flush occurs.

Default NaN mode. Setting the DN bit in the FPSC register enables default NaN mode. In this mode,

the result of any arithmetic data processing operation that involves an input NaN, or that generates

a NaN result, returns the default NaN. Propagation of the fraction bits is maintained only by VABS,

143June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...