Register 7: ADC Underflow Status (ADCUSTAT), offset 0x018

This register indicates underflow conditions in the sample sequencer FIFOs. The corresponding

underflow condition is cleared by writing a 1 to the relevant bit position.

ADC Underflow Status (ADCUSTAT)

ADC0 base: 0x4003.8000

ADC1 base: 0x4003.9000

Offset 0x018

Type RW1C, reset 0x0000.0000

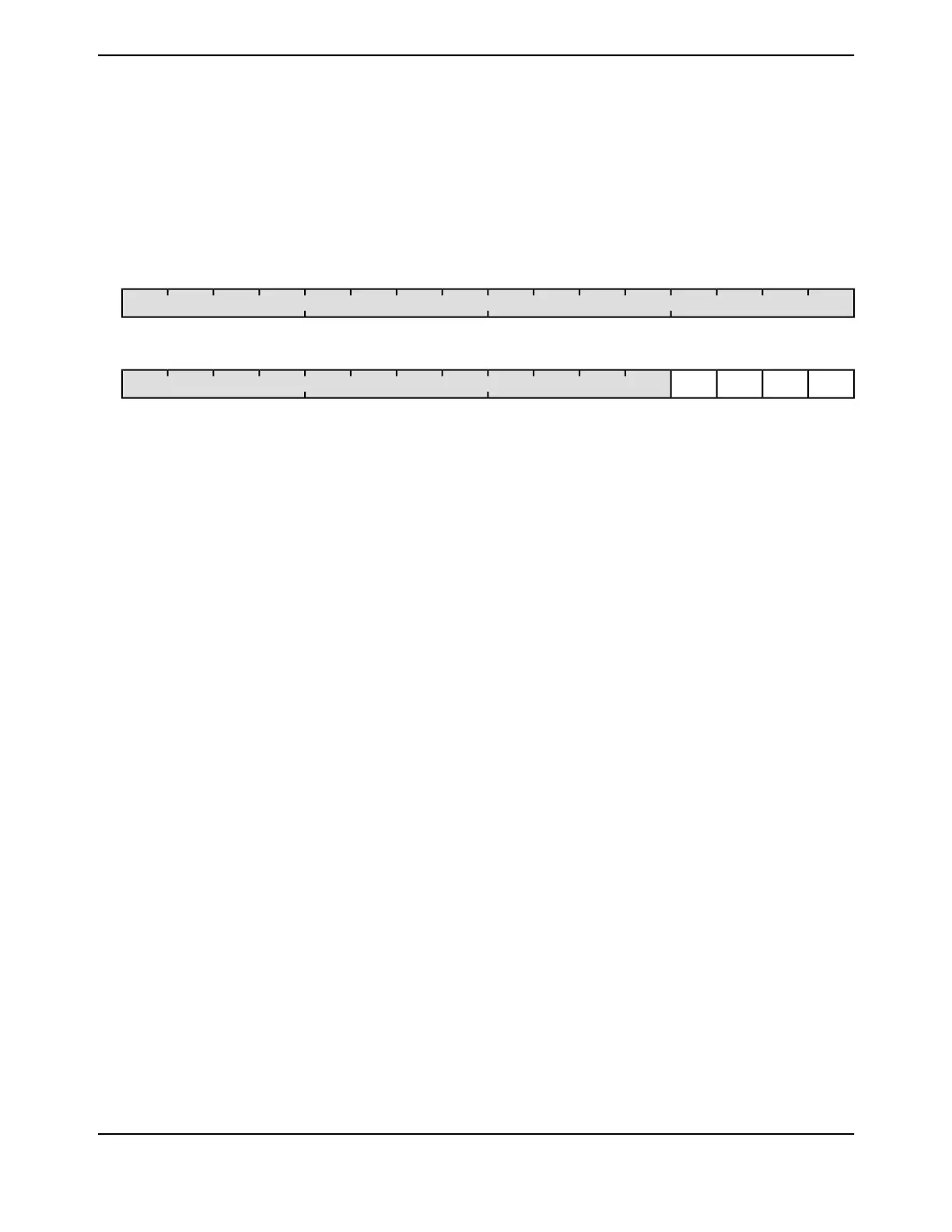

16171819202122232425262728293031

reserved

ROROROROROROROROROROROROROROROROType

0000000000000000Reset

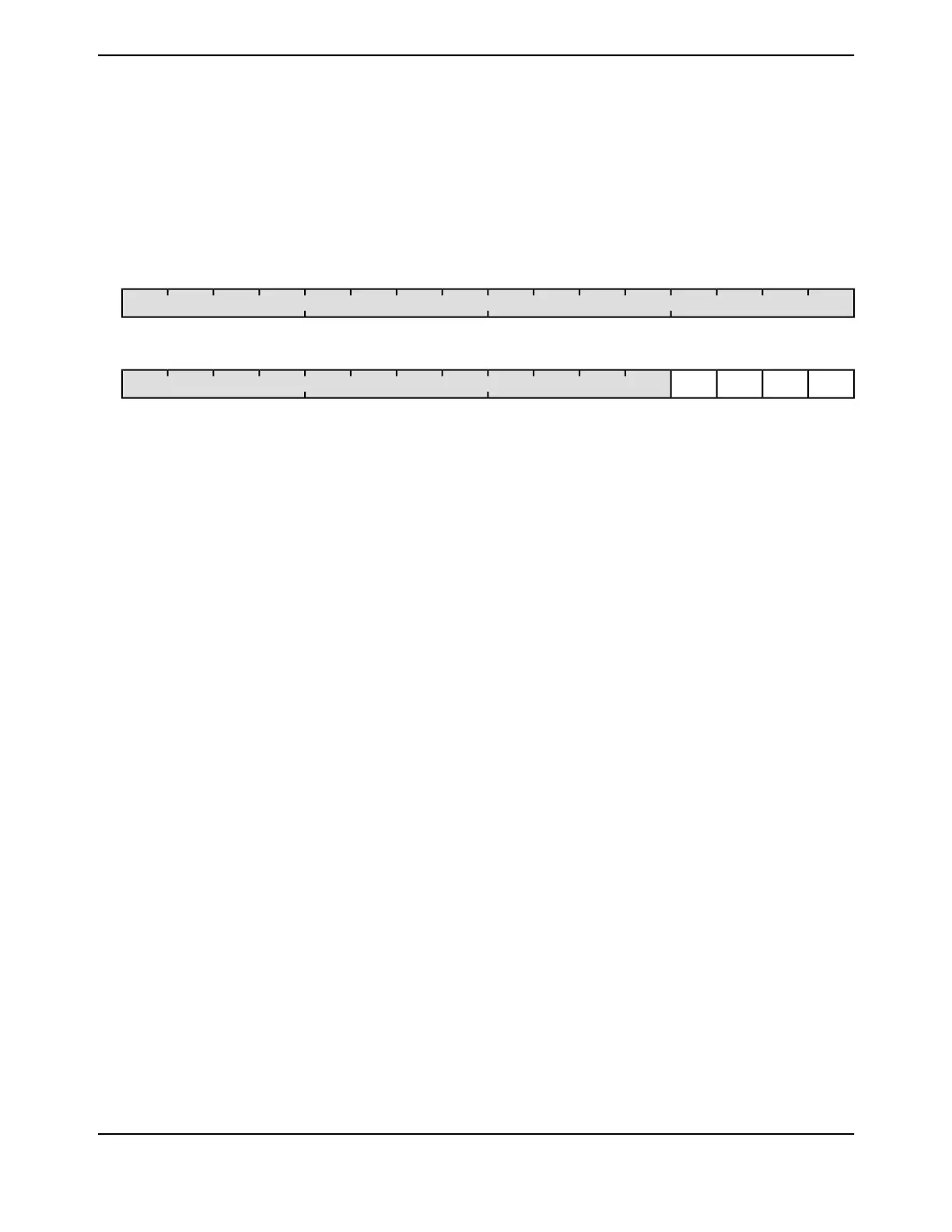

0123456789101112131415

UV0UV1UV2UV3reserved

RW1CRW1CRW1CRW1CROROROROROROROROROROROROType

0000000000000000Reset

DescriptionResetTypeNameBit/Field

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x0000.000ROreserved31:4

SS3 FIFO Underflow

The valid configurations for this field are shown below. This bit is cleared

by writing a 1.

DescriptionValue

The FIFO has not underflowed.0

The FIFO for the Sample Sequencer has hit an underflow

condition, meaning that the FIFO is empty and a read was

requested. The problematic read does not move the FIFO

pointers, and 0s are returned.

1

0RW1CUV33

SS2 FIFO Underflow

The valid configurations are the same as those for the UV3 field. This

bit is cleared by writing a 1.

0RW1CUV22

SS1 FIFO Underflow

The valid configurations are the same as those for the UV3 field. This

bit is cleared by writing a 1.

0RW1CUV11

SS0 FIFO Underflow

The valid configurations are the same as those for the UV3 field. This

bit is cleared by writing a 1.

0RW1CUV00

June 18, 20141096

Texas Instruments-Production Data

Analog-to-Digital Converter (ADC)

Loading...

Loading...