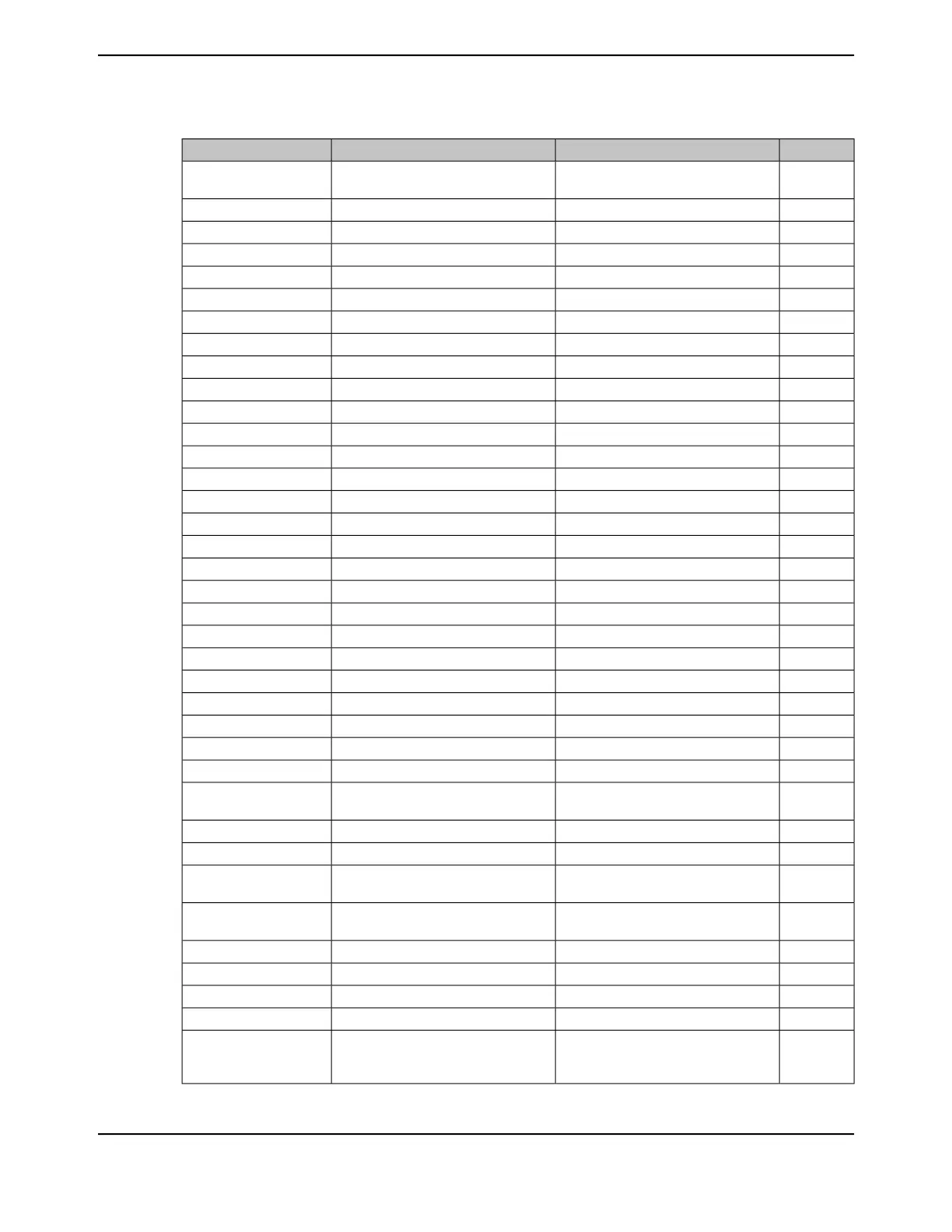

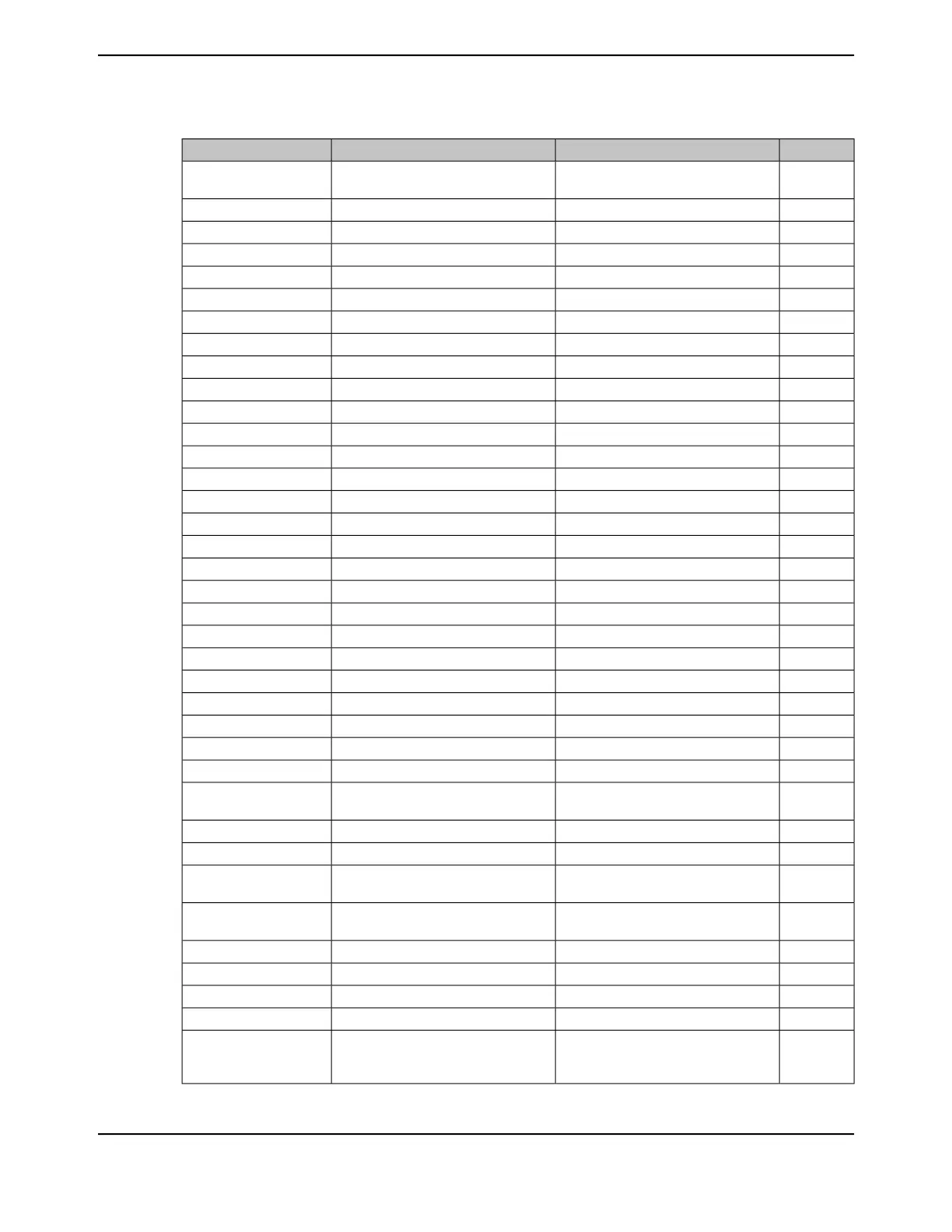

Table 2-13. Cortex-M4F Instruction Summary (continued)

FlagsBrief DescriptionOperandsMnemonic

-Store multiple registers, decrement

before

Rn{!}, reglistSTMDB, STMEA

-Store multiple registers, increment afterRn{!}, reglistSTMFD, STMIA

-Store register wordRt, [Rn {, #offset}]STR

-Store register byteRt, [Rn {, #offset}]STRB, STRBT

-Store register two wordsRt, Rt2, [Rn {, #offset}]STRD

-Store register exclusiveRt, Rt, [Rn {, #offset}]STREX

-Store register exclusive byteRd, Rt, [Rn]STREXB

-Store register exclusive halfwordRd, Rt, [Rn]STREXH

-Store register halfwordRt, [Rn {, #offset}]STRH, STRHT

-Store register signed byteRt, [Rn {, #offset}]STRSB, STRSBT

-Store register signed halfwordRt, [Rn {, #offset}]STRSH, STRSHT

-Store register wordRt, [Rn {, #offset}]STRT

N,Z,C,VSubtract{Rd,} Rn, Op2SUB, SUBS

N,Z,C,VSubtract 12-bit constant{Rd,} Rn, #imm12SUB, SUBW

-Supervisor call#immSVC

-Extend 8 bits to 32 and add{Rd,} Rn, Rm, {,ROR #}SXTAB

-Dual extend 8 bits to 16 and add{Rd,} Rn, Rm,{,ROR #}SXTAB16

-Extend 16 bits to 32 and add{Rd,} Rn, Rm,{,ROR #}SXTAH

-Signed extend byte 16{Rd,} Rm {,ROR #n}SXTB16

-Sign extend a byte{Rd,} Rm {,ROR #n}SXTB

-Sign extend a halfword{Rd,} Rm {,ROR #n}SXTH

-Table branch byte[Rn, Rm]TBB

-Table branch halfword[Rn, Rm, LSL #1]TBH

N,Z,CTest equivalenceRn, Op2TEQ

N,Z,CTestRn, Op2TST

GEUnsigned add 16{Rd,} Rn, RmUADD16

GEUnsigned add 8{Rd,} Rn, RmUADD8

GEUnsigned add and subtract with

exchange

{Rd,} Rn, RmUASX

-Unsigned halving add 16{Rd,} Rn, RmUHADD16

-Unsigned halving add 8{Rd,} Rn, RmUHADD8

-Unsigned halving add and subtract with

exchange

{Rd,} Rn, RmUHASX

-Unsigned halving subtract and add with

exchange

{Rd,} Rn, RmUHSAX

-Unsigned halving subtract 16{Rd,} Rn, RmUHSUB16

-Unsigned halving subtract 8{Rd,} Rn, RmUHSUB8

-Unsigned bit field extractRd, Rn, #lsb, #widthUBFX

-Unsigned divide{Rd,} Rn, RmUDIV

-Unsigned multiply accumulate

accumulate long (32x32+64), 64-bit

result

RdLo, RdHi, Rn, RmUMAAL

131June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...