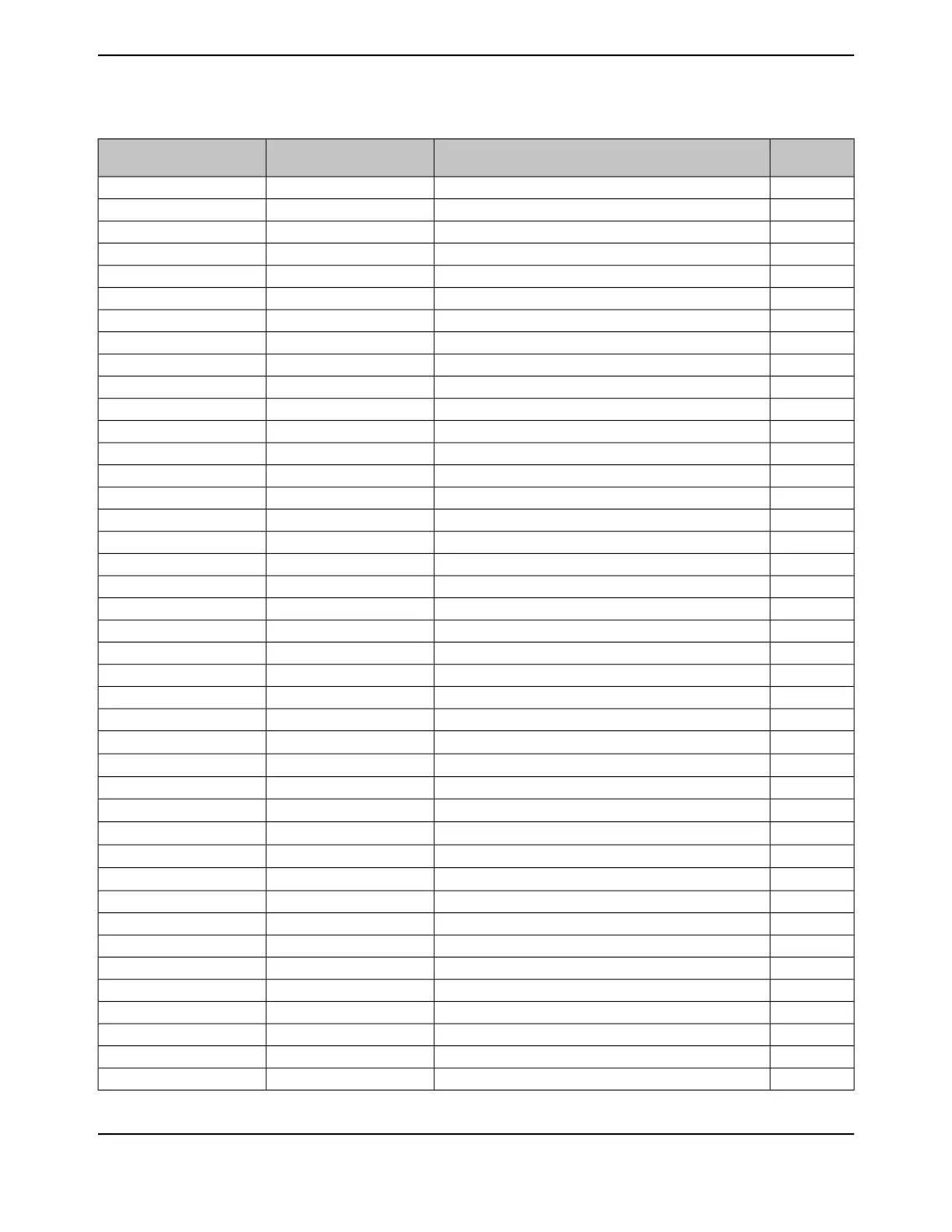

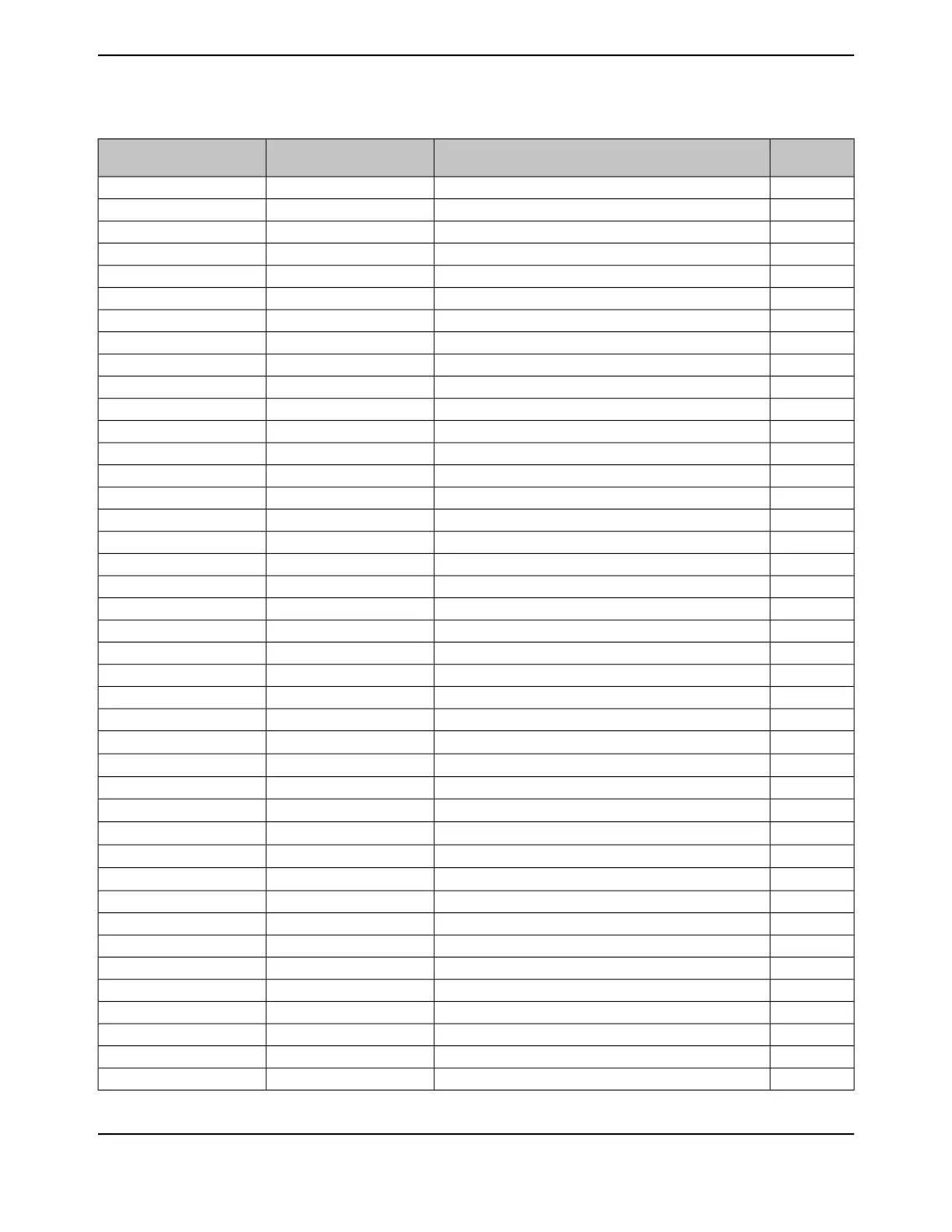

Table 2-4. Memory Map (continued)

For details,

see page ...

DescriptionEndStart

755GPIO Port J0x4003.DFFF0x4003.D000

-Reserved0x4003.FFFF0x4003.E000

1375CAN0 Controller0x4004.0FFF0x4004.0000

1375CAN1 Controller0x4004.1FFF0x4004.1000

-Reserved0x4004.FFFF0x4004.2000

1646USB0x4005.0FFF0x4005.0000

-Reserved0x4005.7FFF0x4005.1000

755GPIO Port A (AHB aperture)0x4005.8FFF0x4005.8000

755GPIO Port B (AHB aperture)0x4005.9FFF0x4005.9000

755GPIO Port C (AHB aperture)0x4005.AFFF0x4005.A000

755GPIO Port D (AHB aperture)0x4005.BFFF0x4005.B000

755GPIO Port E (AHB aperture)0x4005.CFFF0x4005.C000

755GPIO Port F (AHB aperture)0x4005.DFFF0x4005.D000

755GPIO Port G (AHB aperture)0x4005.EFFF0x4005.E000

755GPIO Port H (AHB aperture)0x4005.FFFF0x4005.F000

755GPIO Port J (AHB aperture)0x4006.0FFF0x4006.0000

755GPIO Port K (AHB aperture)0x4006.1FFF0x4006.1000

755GPIO Port L (AHB aperture)0x4006.2FFF0x4006.2000

755GPIO Port M (AHB aperture)0x4006.3FFF0x4006.3000

755GPIO Port N (AHB aperture)0x4006.4FFF0x4006.4000

755GPIO Port P (AHB aperture)0x4006.5FFF0x4006.5000

755GPIO Port Q (AHB aperture)0x4006.6FFF0x4006.6000

-Reserved0x400A.EFFF0x4006.7000

621EEPROM and Key Locker0x400A.FFFF0x400A.F000

-Reserved0x400B.7FFF0x400B.0000

1299I

2

C 80x400B.8FFF0x400B.8000

1299I

2

C 90x400B.9FFF0x400B.9000

-Reserved0x400B.FFFF0x400B.A000

1299I

2

C 40x400C.0FFF0x400C.0000

1299I

2

C 50x400C.1FFF0x400C.1000

1299I

2

C 60x400C.2FFF0x400C.2000

1299I

2

C 70x400C.3FFF0x400C.3000

-Reserved0x400C.FFFF0x400C.4000

856EPI 00x400D.0FFF0x400D.0000

-Reserved0x400D.FFFF0x400D.1000

97416/32-bit Timer 60x400E.0FFF0x400E.0000

97416/32-bit Timer 70x400E.1FFF0x400E.1000

-Reserved0x400E.BFFF0x400E.2000

1467Ethernet Controller0x400E.CFFF0x400E.C000

-Reserved0x400F.8FFF0x400E.D000

523System Exception Module0x400F.9FFF0x400F.9000

105June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...