23.2 Signal Description

The following table lists the external signals of the PWM module and describes the function of each.

The PWM controller signals are alternate functions for some GPIO signals and default to be GPIO

signals at reset. The column in the table below titled "Pin Mux/Pin Assignment" lists the possible

GPIO pin placements for these PWM signals. The AFSEL bit in the GPIO Alternate Function Select

(GPIOAFSEL) register (page 770) should be set to choose the PWM function. The number in

parentheses is the encoding that must be programmed into the PMCn field in the GPIO Port Control

(GPIOPCTL) register (page 787) to assign the PWM signal to the specified GPIO port pin. For more

information on configuring GPIOs, see “General-Purpose Input/Outputs (GPIOs)” on page 742.

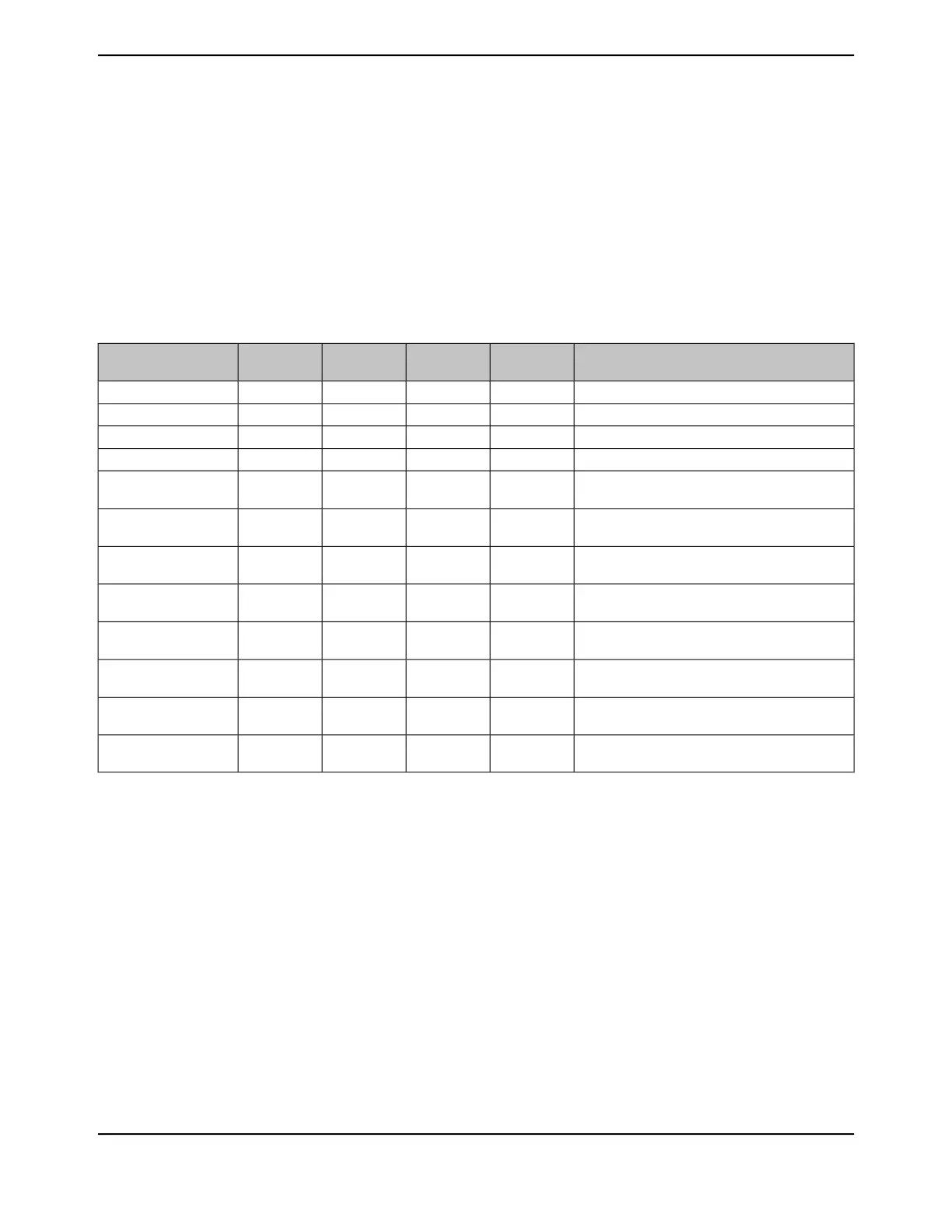

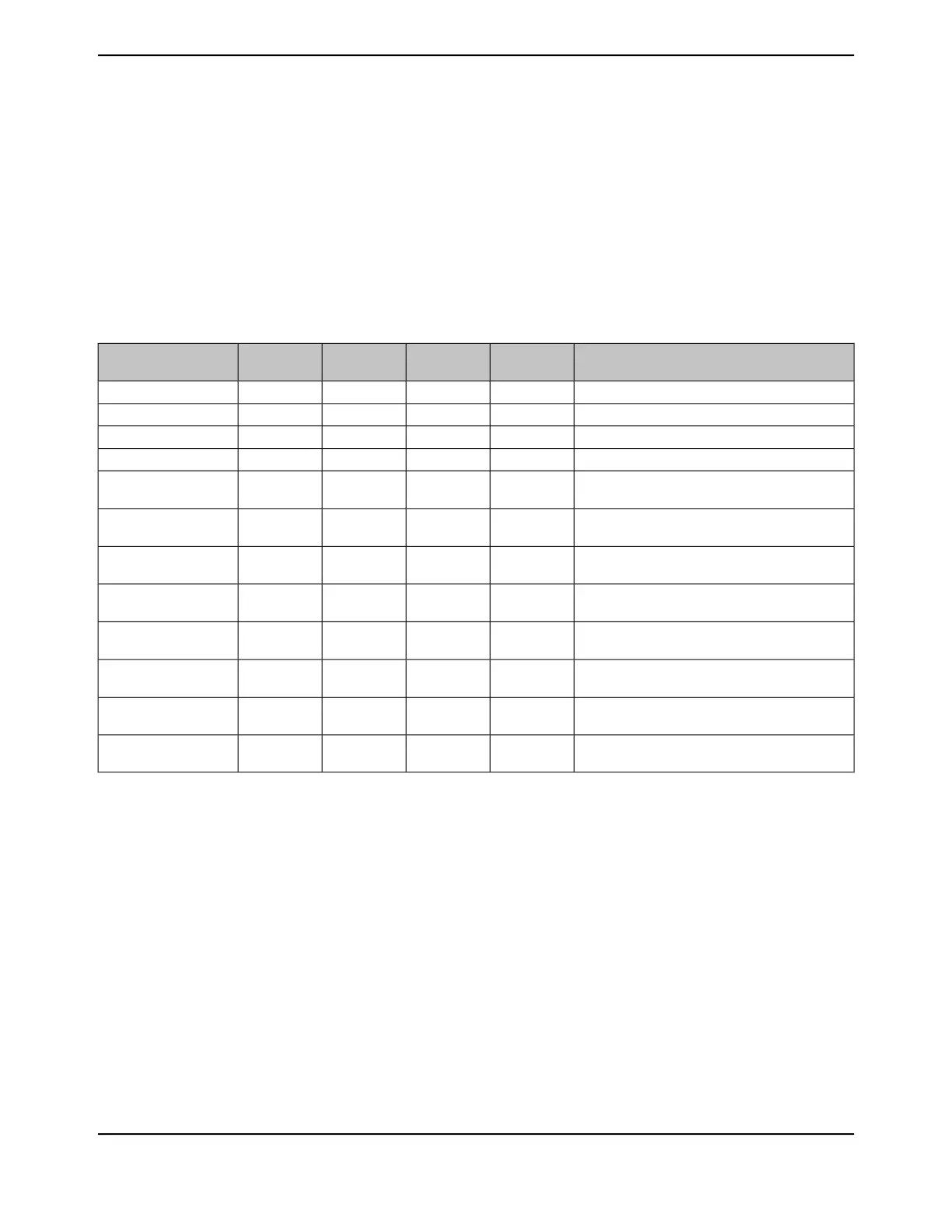

Table 23-1. PWM Signals (128TQFP)

DescriptionBuffer TypePin TypePin Mux / Pin

Assignment

Pin NumberPin Name

Motion Control Module 0 PWM Fault 0.TTLIPF4 (6)46M0FAULT0

Motion Control Module 0 PWM Fault 1.TTLIPK6 (6)61M0FAULT1

Motion Control Module 0 PWM Fault 2.TTLIPK7 (6)60M0FAULT2

Motion Control Module 0 PWM Fault 3.TTLIPL0 (6)81M0FAULT3

Motion Control Module 0 PWM 0. This signal is

controlled by Module 0 PWM Generator 0.

TTLOPF0 (6)42M0PWM0

Motion Control Module 0 PWM 1. This signal is

controlled by Module 0 PWM Generator 0.

TTLOPF1 (6)43M0PWM1

Motion Control Module 0 PWM 2. This signal is

controlled by Module 0 PWM Generator 1.

TTLOPF2 (6)44M0PWM2

Motion Control Module 0 PWM 3. This signal is

controlled by Module 0 PWM Generator 1.

TTLOPF3 (6)45M0PWM3

Motion Control Module 0 PWM 4. This signal is

controlled by Module 0 PWM Generator 2.

TTLOPG0 (6)49M0PWM4

Motion Control Module 0 PWM 5. This signal is

controlled by Module 0 PWM Generator 2.

TTLOPG1 (6)50M0PWM5

Motion Control Module 0 PWM 6. This signal is

controlled by Module 0 PWM Generator 3.

TTLOPK4 (6)63M0PWM6

Motion Control Module 0 PWM 7. This signal is

controlled by Module 0 PWM Generator 3.

TTLOPK5 (6)62M0PWM7

23.3 Functional Description

23.3.1 Clock Configuration

The PWM has two clock source options:

■ The System Clock

■ A predivided System Clock

The clock source is selected by programming the USEPWM bit in the PWM Clock Configuration

(PWMCC) register. The PWMDIV bitfield specifies the divisor of the System Clock that is used to

create the PWM Clock.

23.3.2 PWM Timer

The timer in each PWM generator runs in one of two modes: Count-Down mode or Count-Up/Down

mode. In Count-Down mode, the timer counts from the load value to zero, goes back to the load

June 18, 20141672

Texas Instruments-Production Data

Pulse Width Modulator (PWM)

Loading...

Loading...