2.7.2.1 Wake Up from WFI or Sleep-on-Exit

Normally, the processor wakes up only when the NVIC detects an exception with sufficient priority

to cause exception entry. Some embedded systems might have to execute system restore tasks

after the processor wakes up and before executing an interrupt handler. Entry to the interrupt handler

can be delayed by setting the PRIMASK bit and clearing the FAULTMASK bit. If an interrupt arrives

that is enabled and has a higher priority than current exception priority, the processor wakes up but

does not execute the interrupt handler until the processor clears PRIMASK. For more information

about PRIMASK and FAULTMASK, see page 96 and page 97.

2.7.2.2 Wake Up from WFE

The processor wakes up if it detects an exception with sufficient priority to cause exception entry.

In addition, if the SEVONPEND bit in the SYSCTRL register is set, any new pending interrupt triggers

an event and wakes up the processor, even if the interrupt is disabled or has insufficient priority to

cause exception entry. For more information about SYSCTRL, see page 173.

2.8 Instruction Set Summary

The processor implements a version of the Thumb instruction set. Table 2-13 on page 127 lists the

supported instructions.

Note: In Table 2-13 on page 127:

■ Angle brackets, <>, enclose alternative forms of the operand

■ Braces, {}, enclose optional operands

■ The Operands column is not exhaustive

■ Op2 is a flexible second operand that can be either a register or a constant

■ Most instructions can use an optional condition code suffix

For more information on the instructions and operands, see the instruction descriptions in

the ARM® Cortex™-M4 Technical Reference Manual.

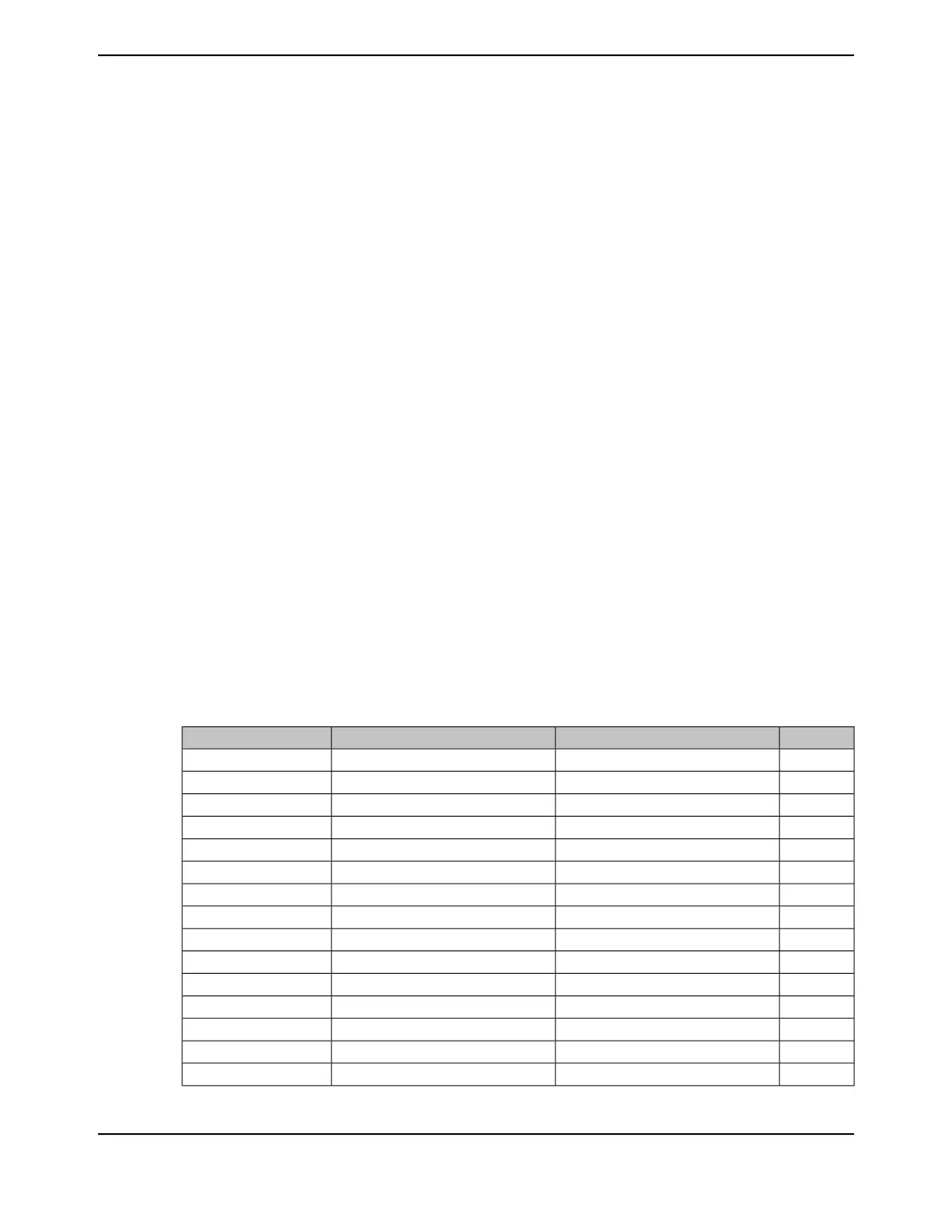

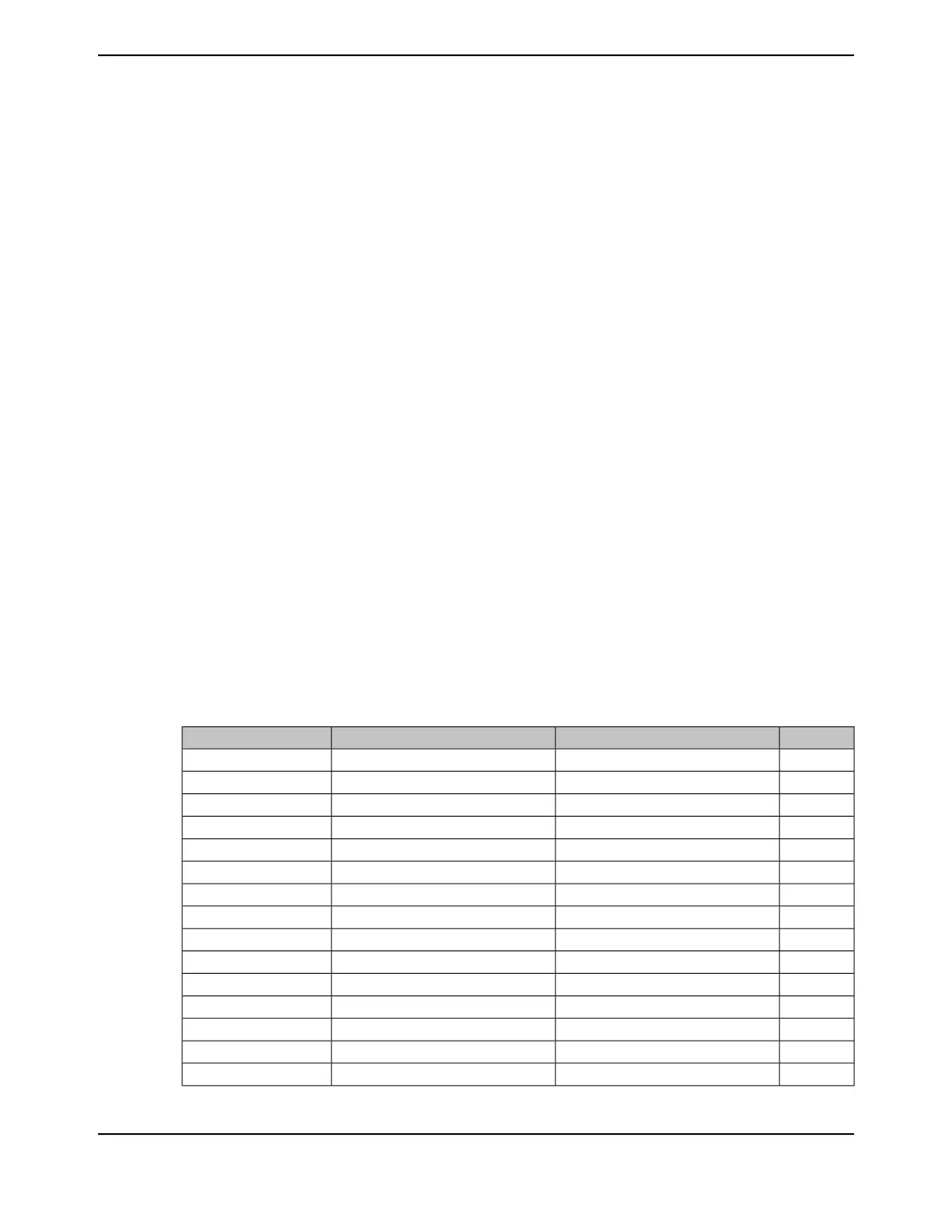

Table 2-13. Cortex-M4F Instruction Summary

FlagsBrief DescriptionOperandsMnemonic

N,Z,C,VAdd with carry{Rd,} Rn, Op2ADC, ADCS

N,Z,C,VAdd{Rd,} Rn, Op2ADD, ADDS

-Add{Rd,} Rn , #imm12ADD, ADDW

-Load PC-relative addressRd, labelADR

N,Z,CLogical AND{Rd,} Rn, Op2AND, ANDS

N,Z,CArithmetic shift rightRd, Rm, <Rs|#n>ASR, ASRS

-BranchlabelB

-Bit field clearRd, #lsb, #widthBFC

-Bit field insertRd, Rn, #lsb, #widthBFI

N,Z,CBit clear{Rd,} Rn, Op2BIC, BICS

-Breakpoint#immBKPT

-Branch with linklabelBL

-Branch indirect with linkRmBLX

-Branch indirectRmBX

-Compare and branch if non-zeroRn, labelCBNZ

127June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...