Register 7: GPIO Raw Interrupt Status (GPIORIS), offset 0x414

The GPIORIS register is the raw interrupt status register. A bit in this register is set when an interrupt

condition occurs on the corresponding GPIO pin or if a µDMA done interrupt occurs. If the

corresponding bit in the GPIO Interrupt Mask (GPIOIM) register (see page 764) is set, the interrupt

is sent to the interrupt controller. Bits read as zero indicate that corresponding input pins have not

initiated an interrupt. For a GPIO level-detect interrupt, the interrupt signal generating the interrupt

must be held until serviced. Once the input signal deasserts from the interrupt generating logical

sense, the corresponding RIS bit in the GPIORIS register clears. For a GPIO edge-detect interrupt,

the RIS bit in the GPIORIS register is cleared by writing a ‘1’ to the corresponding bit in the GPIO

Interrupt Clear (GPIOICR) register. The corresponding GPIOMIS bit reflects the masked value of

the RIS bit.

GPIO Raw Interrupt Status (GPIORIS)

GPIO Port A (AHB) base: 0x4005.8000

GPIO Port B (AHB) base: 0x4005.9000

GPIO Port C (AHB) base: 0x4005.A000

GPIO Port D (AHB) base: 0x4005.B000

GPIO Port E (AHB) base: 0x4005.C000

GPIO Port F (AHB) base: 0x4005.D000

GPIO Port G (AHB) base: 0x4005.E000

GPIO Port H (AHB) base: 0x4005.F000

GPIO Port J (AHB) base: 0x4006.0000

GPIO Port K (AHB) base: 0x4006.1000

GPIO Port L (AHB) base: 0x4006.2000

GPIO Port M (AHB) base: 0x4006.3000

GPIO Port N (AHB) base: 0x4006.4000

GPIO Port P (AHB) base: 0x4006.5000

GPIO Port Q (AHB) base: 0x4006.6000

Offset 0x414

Type RO, reset 0x0000.0000

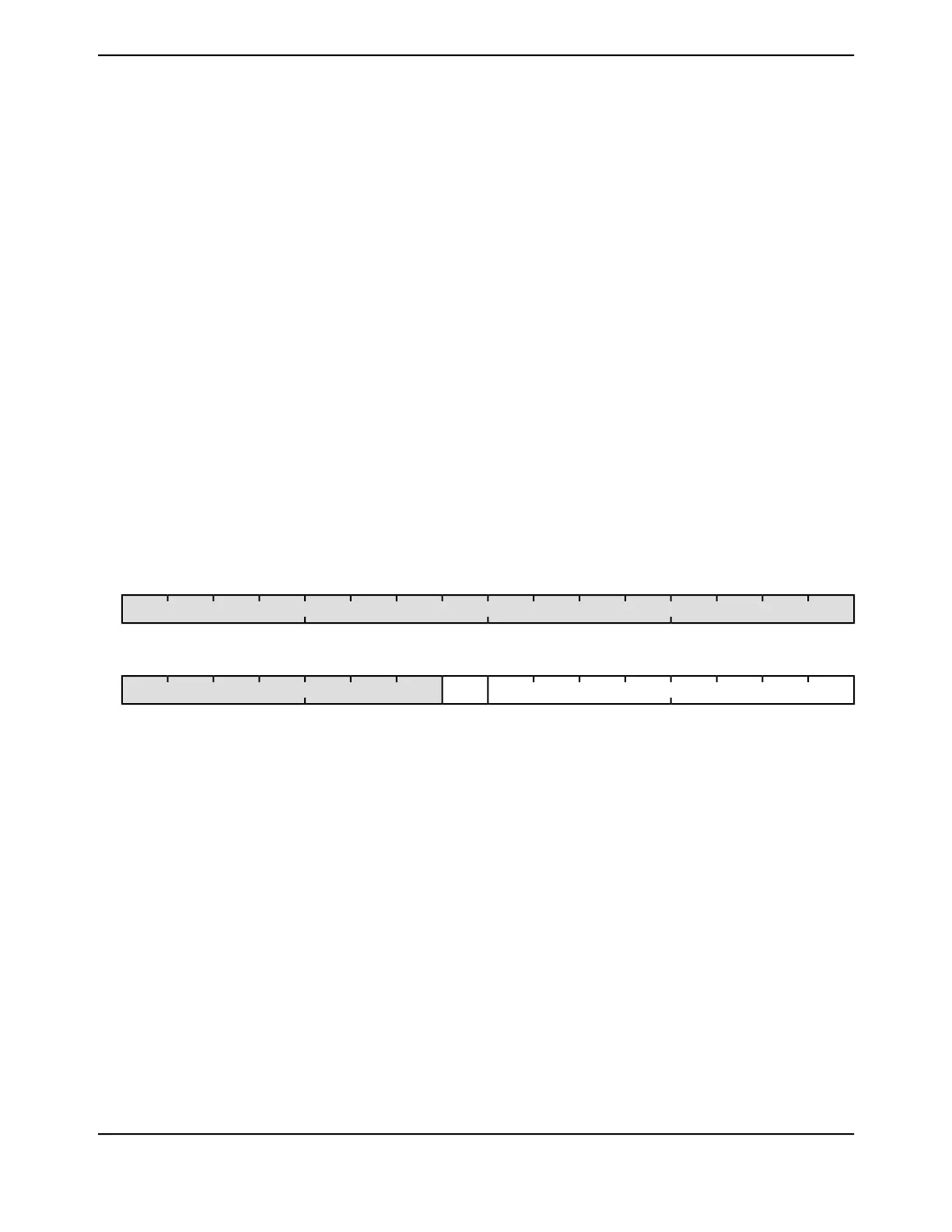

16171819202122232425262728293031

reserved

ROROROROROROROROROROROROROROROROType

0000000000000000Reset

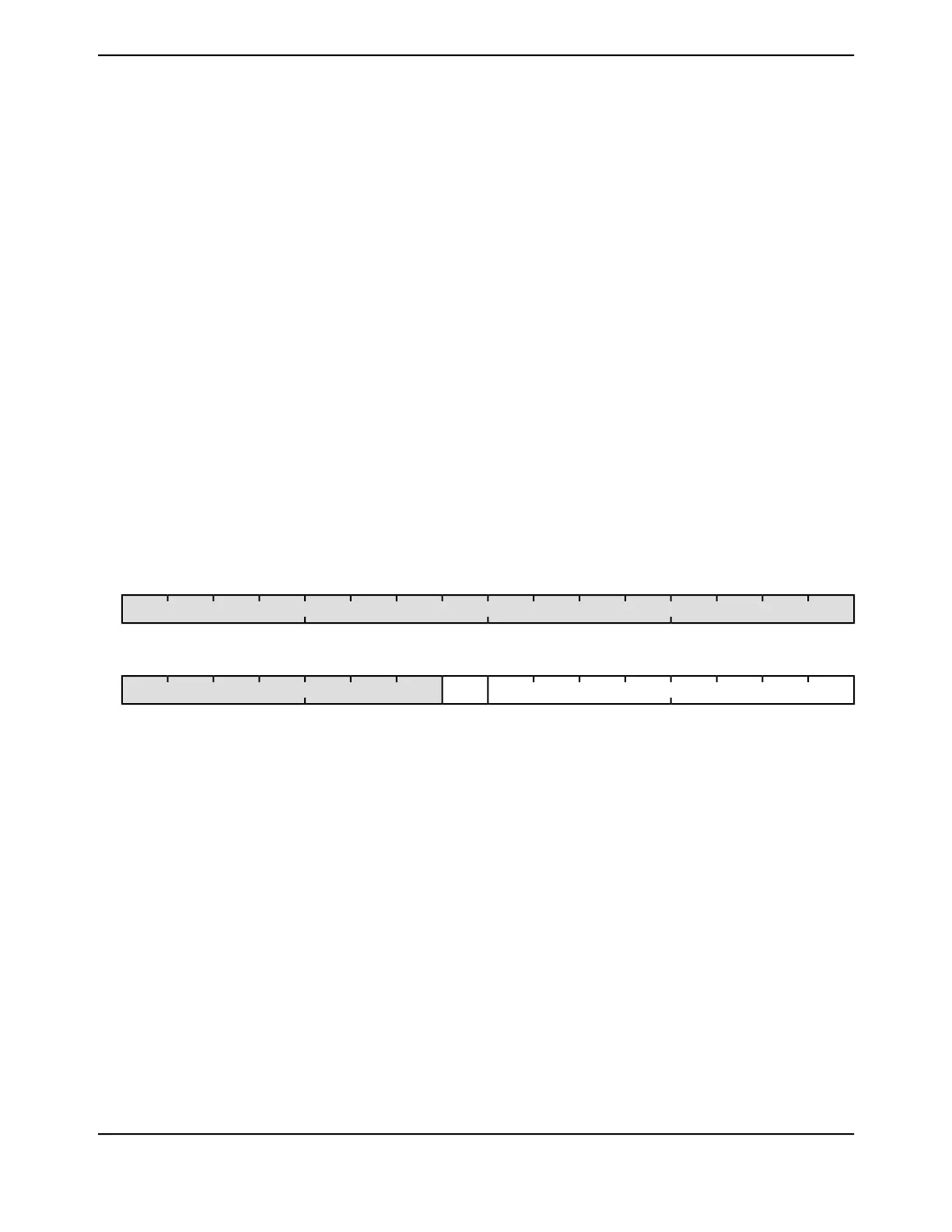

0123456789101112131415

RISDMARISreserved

ROROROROROROROROROROROROROROROROType

0000000000000000Reset

DescriptionResetTypeNameBit/Field

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0ROreserved31:9

GPIO µDMA Done Interrupt Raw Status

DescriptionValue

A µDMA done interrupt has not occurred.0

A µDMA done interrupt has occurred and an interrupt has been

triggered and is pending.

1

This bit is cleared by writing a 1 to the DMAIC bit in the GPIOICR register.

0RODMARIS8

765June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...