Register 5: QSSI Clock Prescale (SSICPSR), offset 0x010

The SSICPSR register specifies the division factor which is used to derive the SSInClk from the

system clock. The clock is further divided by a value from 1 to 256, which is 1 + SCR. SCR is

programmed in the SSICR0 register. The frequency of the SSInClk is defined by:

SSInClk = SysClk / (CPSDVSR * (1 + SCR))

The value programmed into this register must be an even number between 2 and 254. The

least-significant bit of the programmed number is hard-coded to zero. If an odd number is written

to this register, data read back from this register has the least-significant bit as zero.

QSSI Clock Prescale (SSICPSR)

QSSI0 base: 0x4000.8000

QSSI1 base: 0x4000.9000

QSSI2 base: 0x4000.A000

QSSI3 base: 0x4000.B000

Offset 0x010

Type RW, reset 0x0000.0000

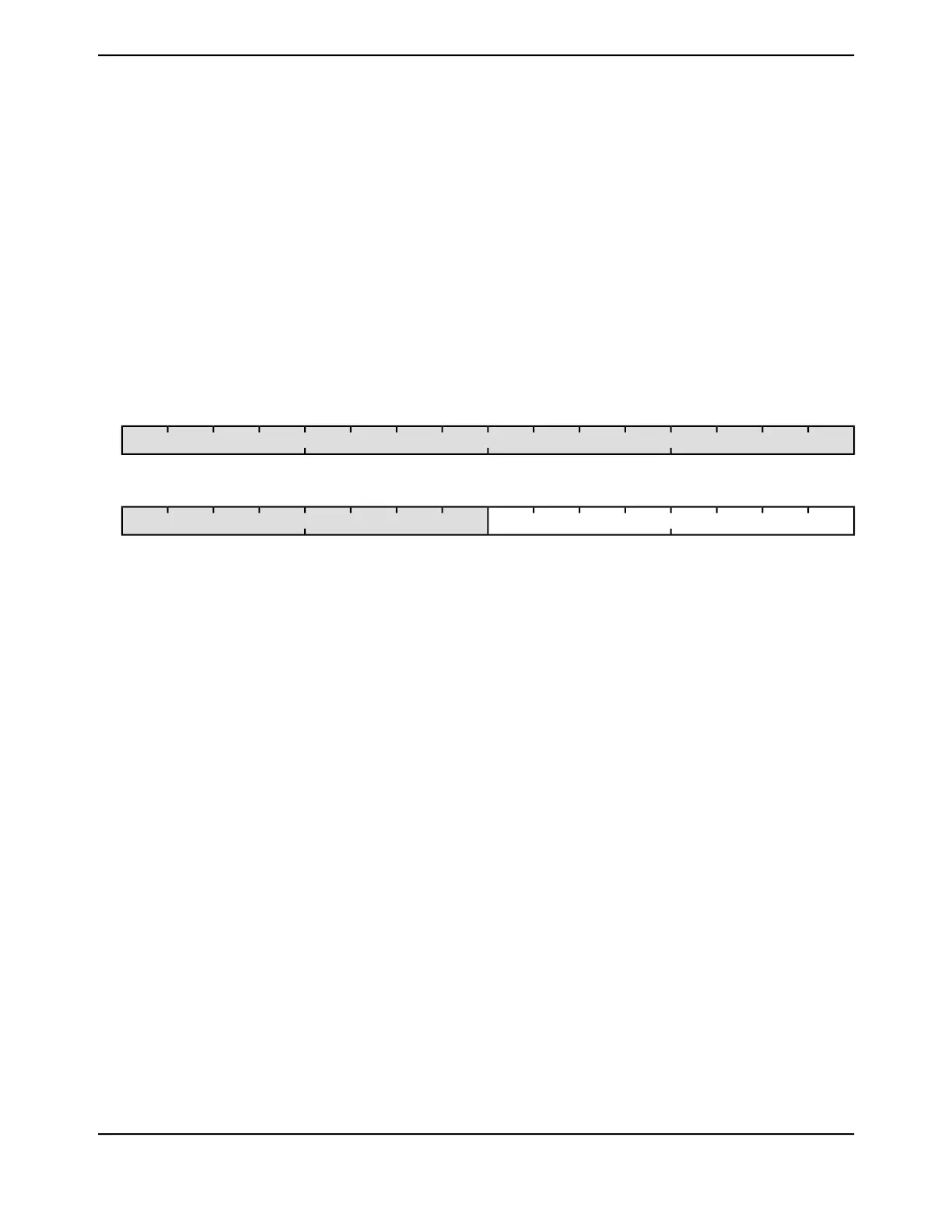

16171819202122232425262728293031

reserved

ROROROROROROROROROROROROROROROROType

0000000000000000Reset

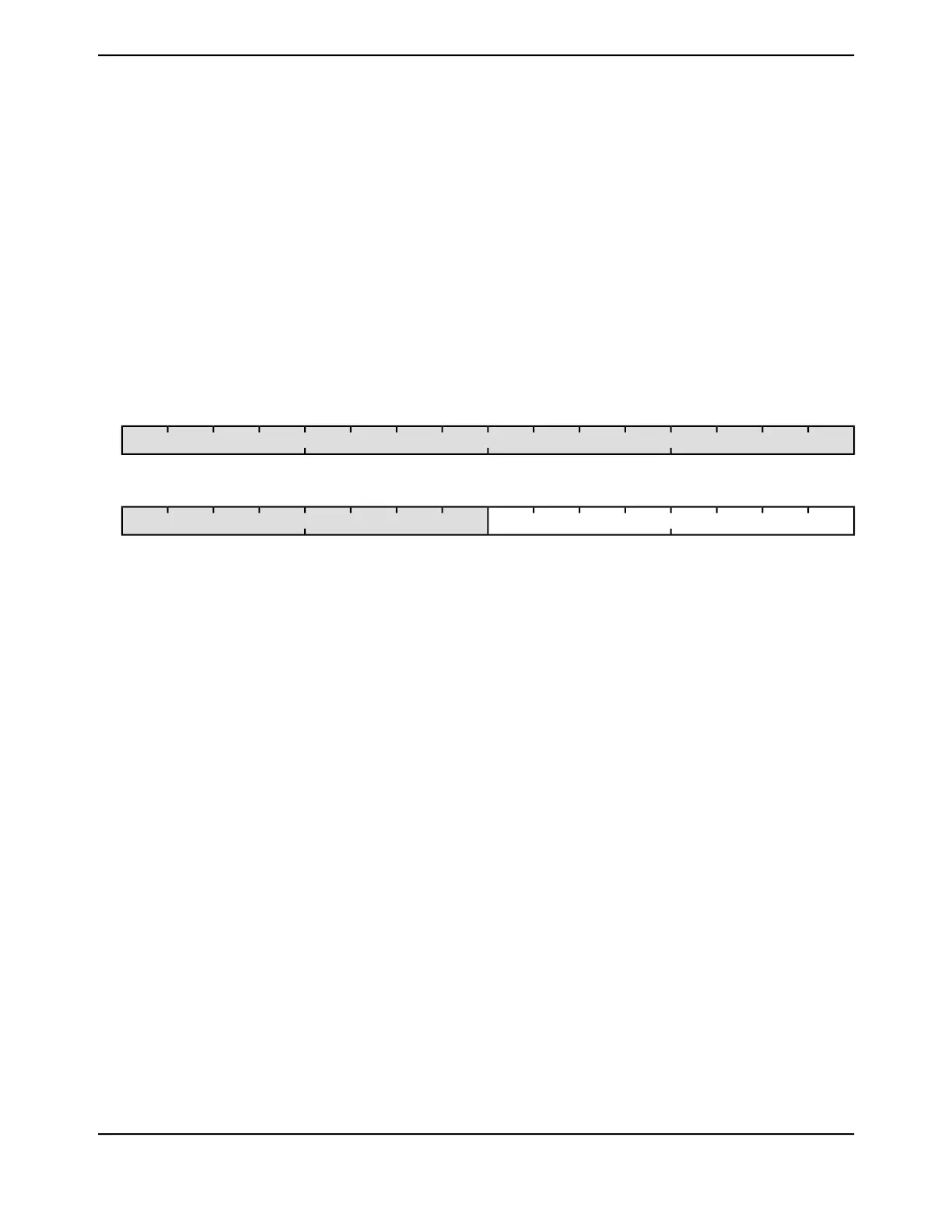

0123456789101112131415

CPSDVSRreserved

RWRWRWRWRWRWRWRWROROROROROROROROType

0000000000000000Reset

DescriptionResetTypeNameBit/Field

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x00ROreserved31:8

QSSI Clock Prescale Divisor

This value must be an even number from 2 to 254, depending on the

frequency of SSInClk. The LSB always returns 0 on reads.

0x00RWCPSDVSR7:0

June 18, 20141252

Texas Instruments-Production Data

Quad Synchronous Serial Interface (QSSI)

Loading...

Loading...