Register 4: Hibernation Control (HIBCTL), offset 0x010

This register is the control register for the Hibernation module. This register must be written last

before a hibernate event is issued. Writes to other registers after the HIBREQ bit is set are not

guaranteed to complete before hibernation is entered.

Note: Writes to this register have special timing requirements. Software should make use of the

WRC bit in the HIBCTL register to ensure that the required synchronization has elapsed.

While the WRC bit is clear, any attempts to write this register are ignored. Reads may occur

at any time.

Note that once tamper is enabled, the following HIBCTL clock configuration bits and bus write stall

bit are locked and cannot be modified:

■ OSCSEL

■ OSCDRV

■ OSCBYP

■ VDD3ON

■ CLK32EN

■ RTCEN

Hibernation Control (HIBCTL)

Base 0x400F.C000

Offset 0x010

Type RW, reset 0x8000.2000

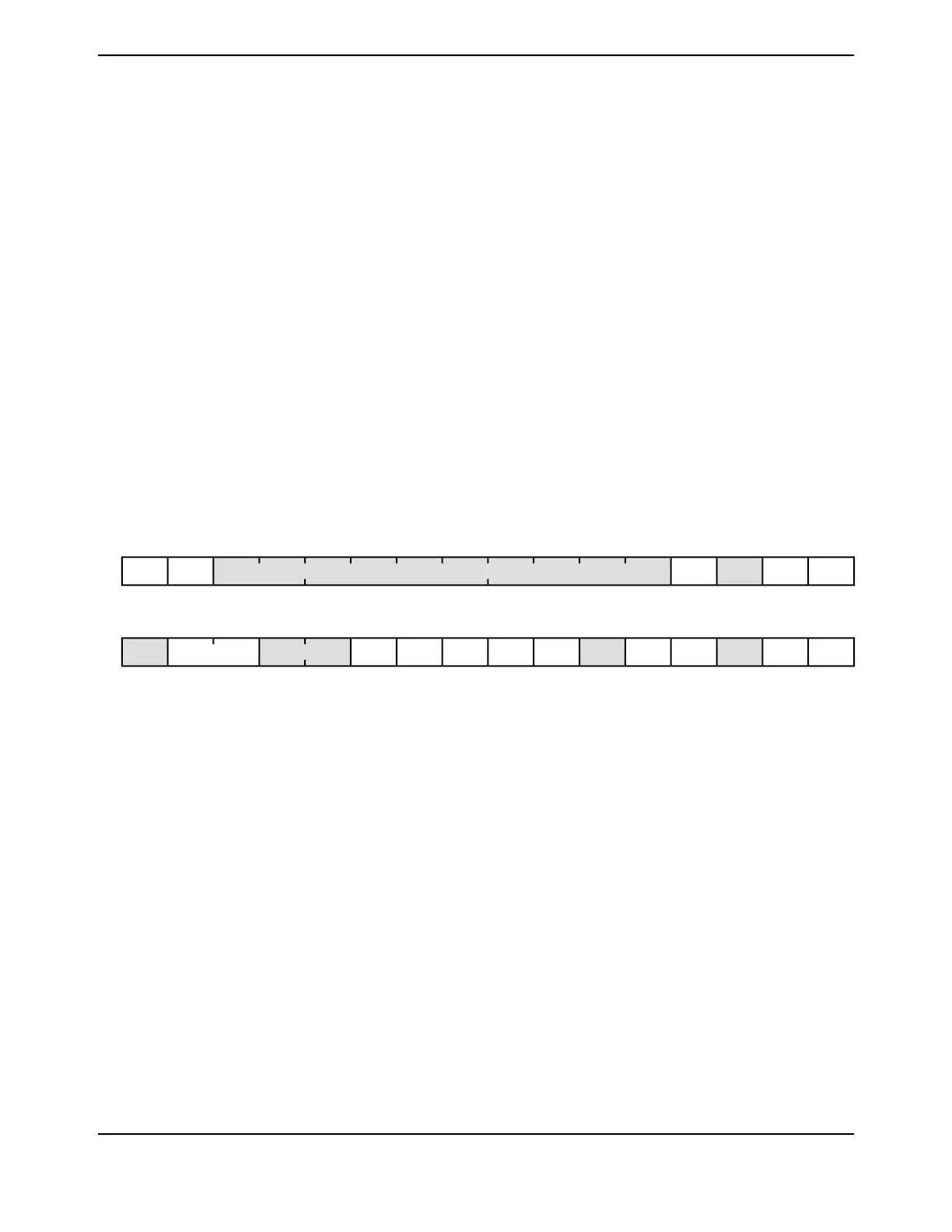

16171819202122232425262728293031

OSCBYPOSCDRVreservedOSCSELreservedRETCLRWRC

RWRWRORWRORORORORORORORORORORWROType

0000000000000001Reset

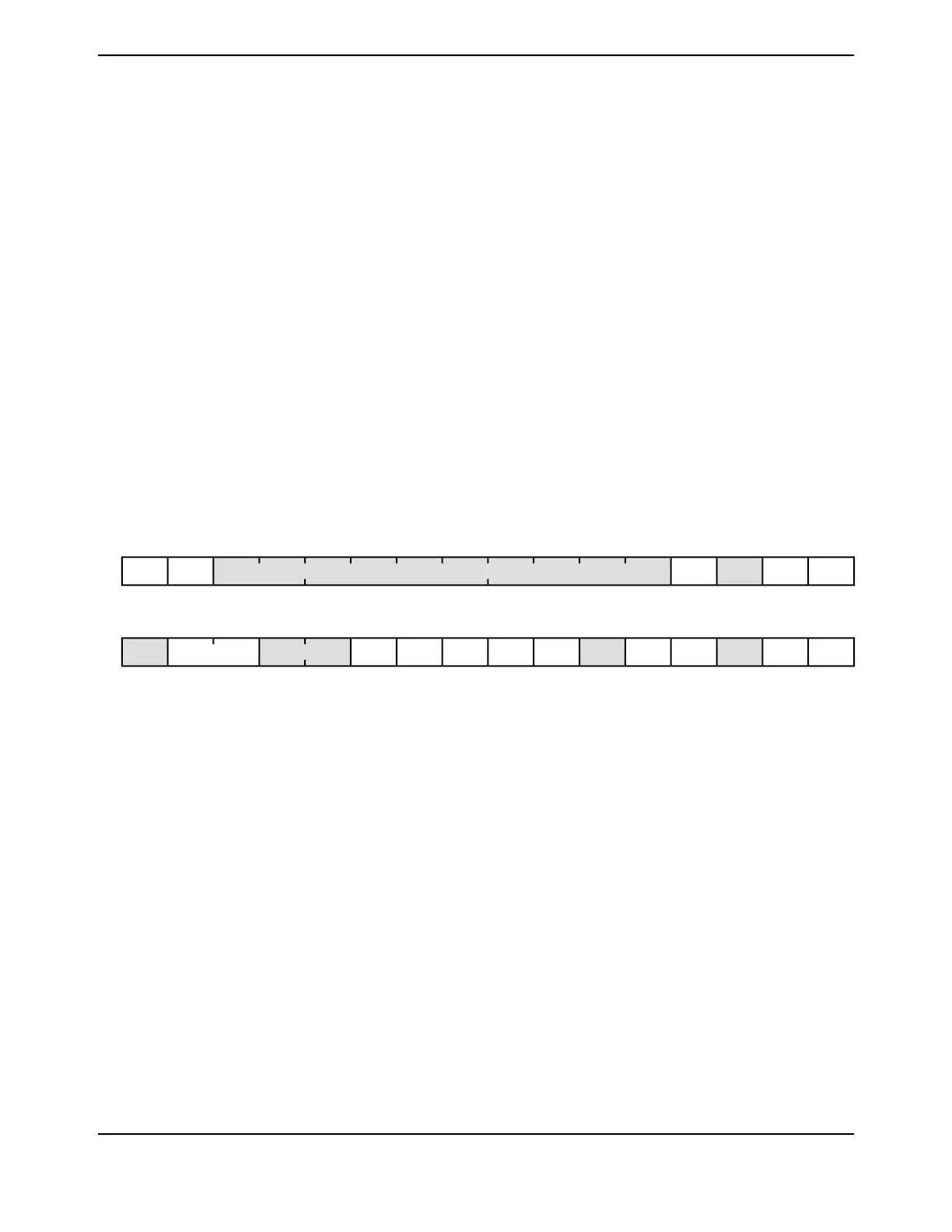

0123456789101112131415

RTCENHIBREQreservedRTCWENPINWENreservedCLK32ENVABORTVDD3ONBATWKENBATCHKreservedVBATSELreserved

RWRWRORWRWRORWRWRWRWRWRORORWRWROType

0000000000000100Reset

DescriptionResetTypeNameBit/Field

Write Complete/Capable

DescriptionValue

The interface is processing a prior write and is busy. Any write

operation that is attempted while WRC is 0 results in

undetermined behavior.

0

The interface is ready to accept a write.1

Software must poll this bit between write requests and defer writes until

WRC=1 to ensure proper operation. An interrupt can be configured to

indicate the WRC has completed.

The bit name WRC means "Write Complete," which is the normal use of

the bit (between write accesses). However, because the bit is set

out-of-reset, the name can also mean "Write Capable" which simply

indicates that the interface may be written to by software. This difference

may be exploited by software at reset time to detect which method of

programming is appropriate: 0 = software delay loops required; 1 = WRC

paced available.

1ROWRC31

557June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...