Register 12: UART Masked Interrupt Status (UARTMIS), offset 0x040

The UARTMIS register is the masked interrupt status register. On a read, this register gives the

current masked status value of the corresponding interrupt. A write has no effect.

UART Masked Interrupt Status (UARTMIS)

UART0 base: 0x4000.C000

UART1 base: 0x4000.D000

UART2 base: 0x4000.E000

UART3 base: 0x4000.F000

UART4 base: 0x4001.0000

UART5 base: 0x4001.1000

UART6 base: 0x4001.2000

UART7 base: 0x4001.3000

Offset 0x040

Type RO, reset 0x0000.0000

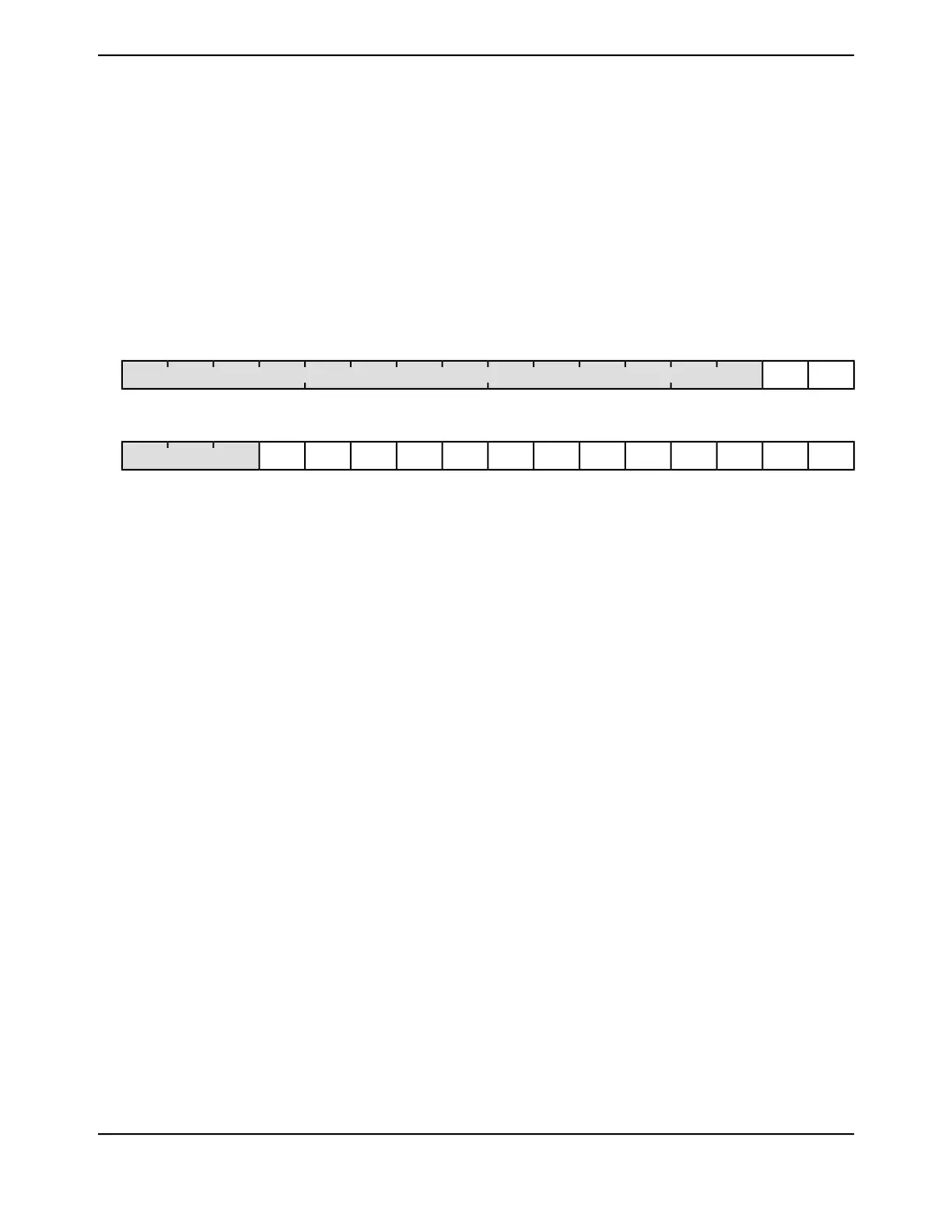

16171819202122232425262728293031

DMARXMISDMATXMIS

reserved

ROROROROROROROROROROROROROROROROType

0000000000000000Reset

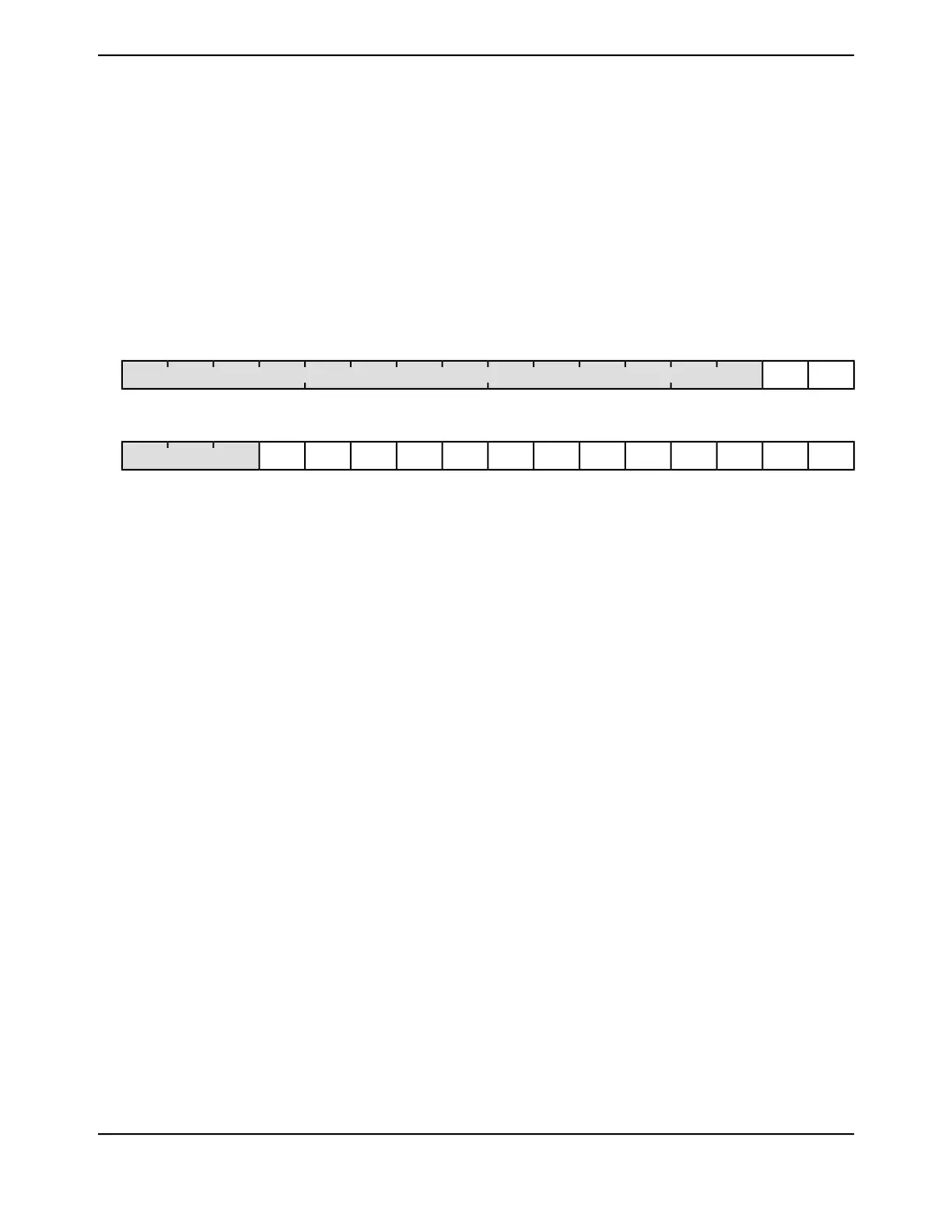

0123456789101112131415

RIMISCTSMISDCDMISDSRMISRXMISTXMISRTMISFEMISPEMISBEMISOEMISEOTMIS9BITMISreserved

ROROROROROROROROROROROROROROROROType

0000000000000000Reset

DescriptionResetTypeNameBit/Field

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0ROreserved31:18

Transmit DMA Masked Interrupt Status

DescriptionValue

An interrupt has not occurred or is masked.0

An unmasked interrupt was signaled due to the completion of

the transmit DMA.

1

This bit is cleared by writing a 1 to the DMATXIC bit in the UARTICR

register.

0RODMATXMIS17

Receive DMA Masked Interrupt Status

DescriptionValue

An interrupt has not occurred or is masked.0

An unmasked interrupt was signaled due to the completion of

the receive DMA.

1

This bit is cleared by writing a 1 to the DMARXIC bit in the UARTICR

register.

0RODMARXMIS16

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0ROreserved15:13

June 18, 20141202

Texas Instruments-Production Data

Universal Asynchronous Receivers/Transmitters (UARTs)

Loading...

Loading...