Register 49: Ethernet MAC PPS Control (EMACPPSCTRL), offset 0x72C

This register is used to control the EN0PPS signal output.

Note: The PTP reference clock referred to below is MOSC clock in course update mode and in

fine correction mode, is the clock tick at which the system time gets updated.

Ethernet MAC PPS Control (EMACPPSCTRL)

Base 0x400E.C000

Offset 0x72C

Type RW, reset 0x0000.0000

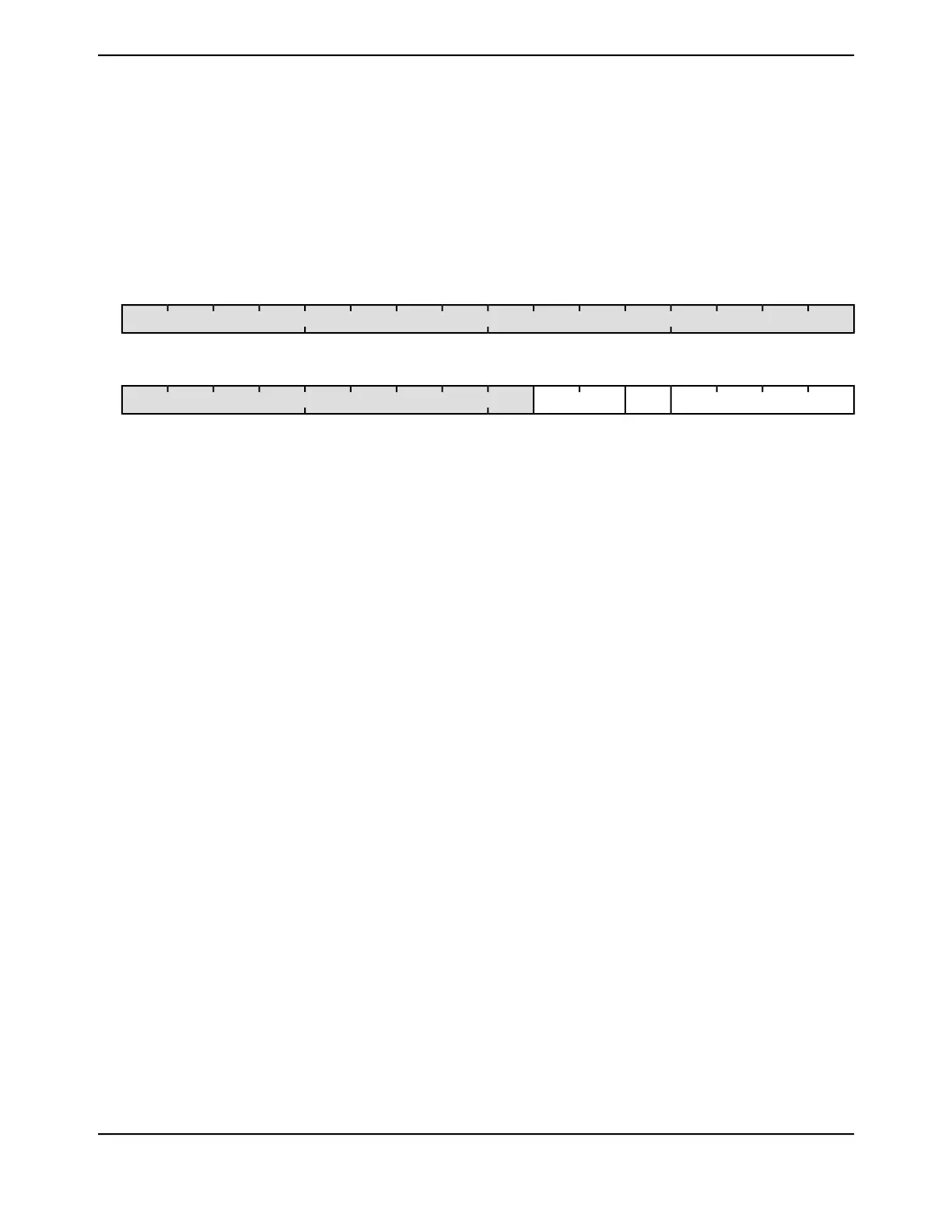

16171819202122232425262728293031

reserved

ROROROROROROROROROROROROROROROROType

0000000000000000Reset

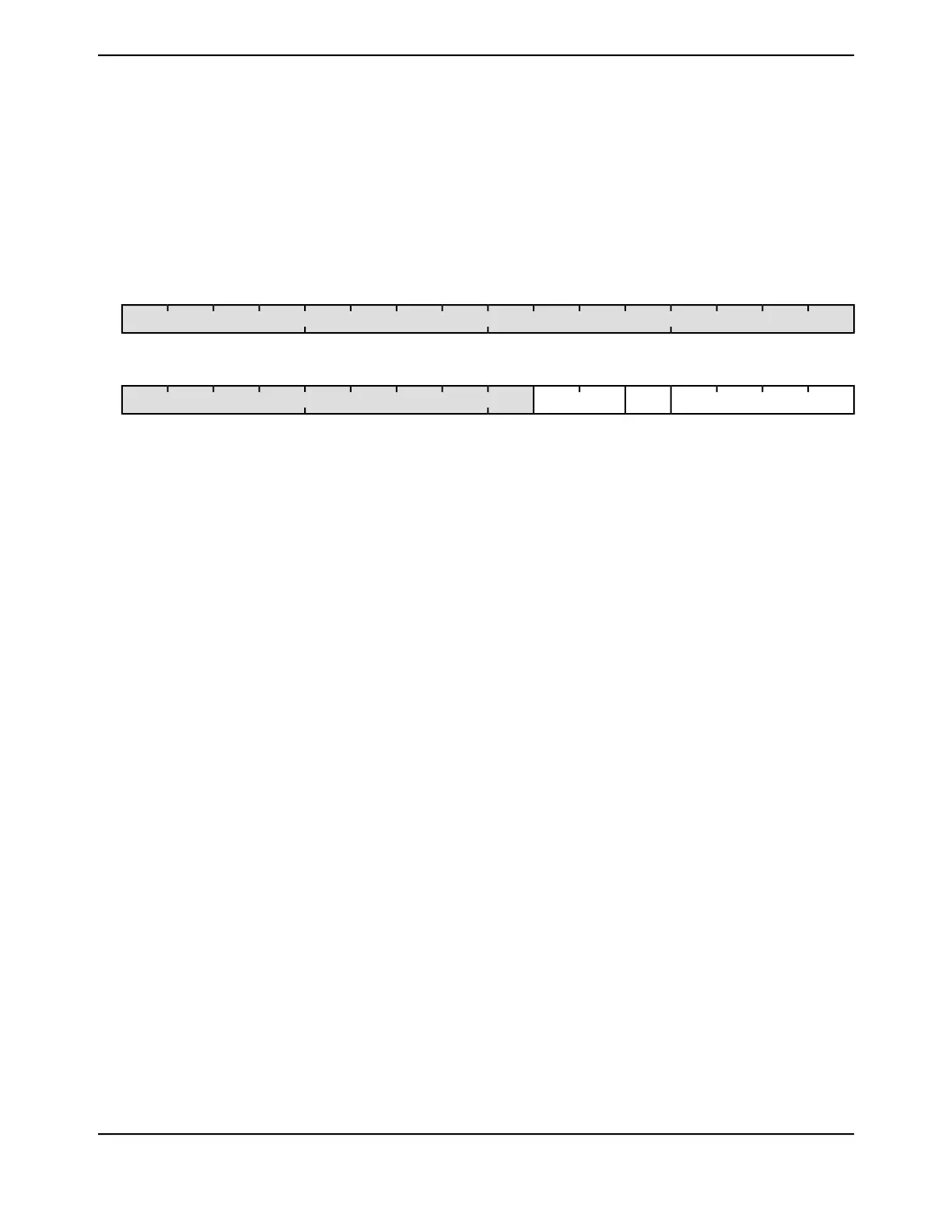

0123456789101112131415

PPSCTRLPPSEN0TRGMODS0reserved

RWRWRWRWROROROROROROROROROROROROType

0000000000000000Reset

DescriptionResetTypeNameBit/Field

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x0ROreserved31:7

Target Time Register Mode for PPS0 Output

This field indicates the Target Time registers (EMACTARGSEC and

EMACTARGNANO) mode for the EN0PPS output signal:

DescriptionValue

Indicates that the Target Time registers are programmed only

for generating the interrupt event.

0x0

Reserved0x1

Indicates that the Target Time registers are programmed for

generating the interrupt event and starting or stopping the

generation of the EN0PPS output signal.

0x2

Indicates that the Target Time registers are programmed only

for starting or stopping the generation of the EN0PPS output

signal. No interrupt is asserted.

0x3

0x0ROTRGMODS06:5

Flexible PPS Output Mode Enable

DescriptionValue

Bits[3:0] function as PPS output frequency control (PPSCTRL).0x0

Bits[3:0] function as PPS Command (PPSCMD).0x1

0x0ROPPSEN04

June 18, 20141548

Texas Instruments-Production Data

Ethernet Controller

Loading...

Loading...