In quad chip select mode (CSCFGEXT is 0x1 and CSCFG is 0x1 or 0x2 in the EPIHBnCFG2 register),

both the peripheral and the memory space must be enabled. In the EPIADDRMAP register, the

EPADR field is 0x3, the ERADR field is 0x3, and the ECADR field is 0x0. With this configuration, CS0n

asserts for the address range beginning at 0x6000.0000, CS1n asserts for 0x8000.0000, CS2n for

0xA000.0000, and CS3n for 0xC000.0000. Table 11-5 on page 828 gives a detailed explanation of

chip select address range mappings based on combinations of enabled peripheral and memory

space.

Note: Only one memory area can be mapped to a single chip select. Enabling multiple memory

areas for one chip select may produce unexpected results.

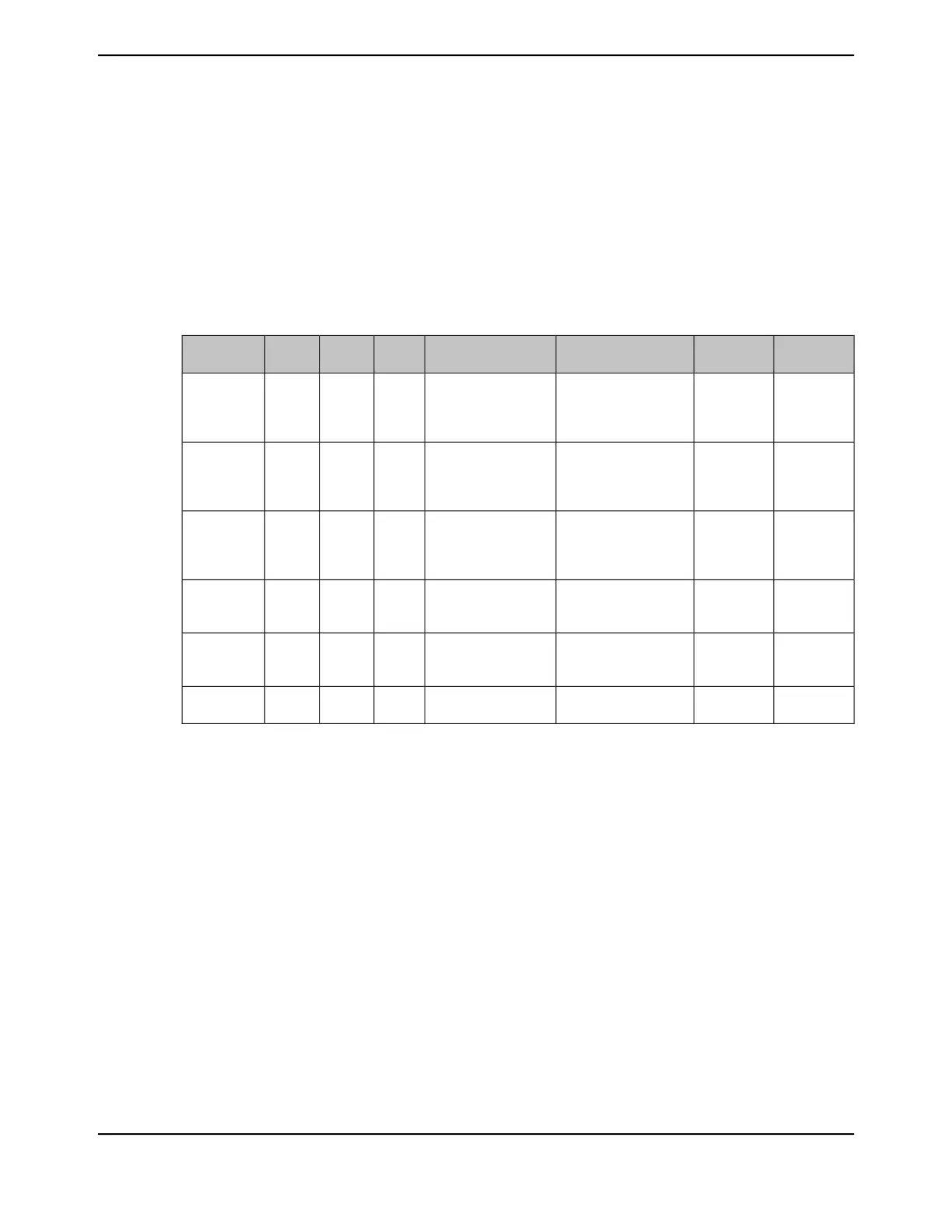

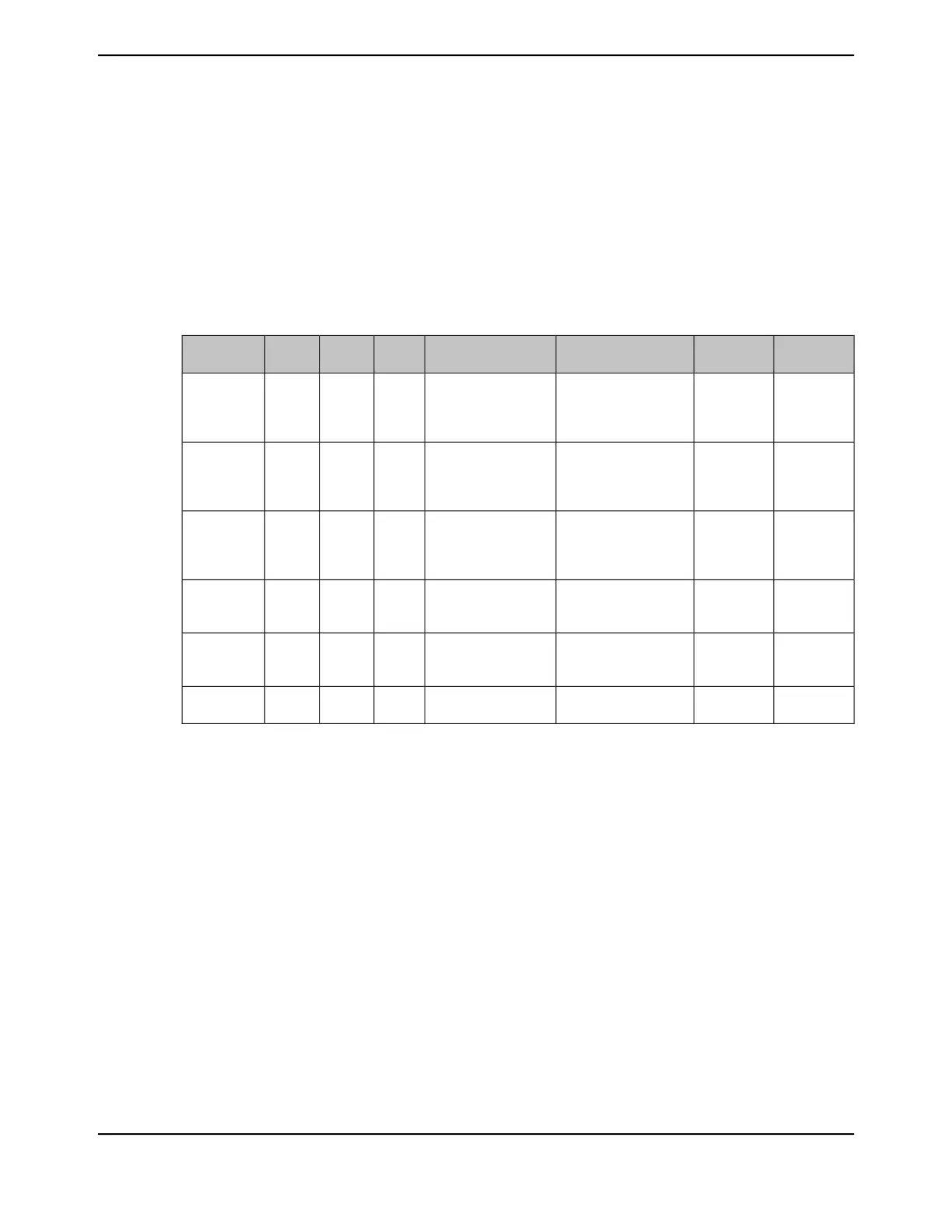

Table 11-5. Dual- and Quad- Chip Select Address Mappings

CS3CS2CS1CS0

a

ECADREPADRERADRChip Select

Mode

N/AN/AEPADR defined address

range (0xA000.000 or

0xC000.0000)

EPADR defined

address range

(0xA000.000 or

0xC000.0000)

0x00x1 or

0x2

0x0Dual-chip

select

N/AN/AERADR defined address

range (0x6000.000 or

0x8000.000)

ERADR defined

address range

(0x6000.000 or

0x8000.000)

0x00x00x1 or

0x2

Dual-chip

select

N/AN/AERADR defined address

range (0x6000.000 or

0x8000.000)

EPADR defined

address range

(0xA000.000 or

0xC000.0000)

0x00x1 or

0x2

0x1 or

0x2

Dual-chip

select

N/AN/AEPADR defined address

range (0xA000.0000 or

0xC000.0000)

ECADR defined

address range

(0x1000.000)

0x10x1 or

0x2

0x0Dual-chip

select

N/AN/AERADR defined address

range (0x6000.000 or

0x8000.000)

ECADR defined

address range

(0x1000.000)

0x10x00x1 or

0x2

Dual-chip

select

0xC000.00000xA000.00000x8000.00000x6000.00000x00x30x3Quad-chip

select

a. When CS0 & CS1 share address space, CS0 asserts when the MSB of the address is 0 and CS1, when the MSB of the

address is '1.'

The MODE field of the EPIHBnCFGn registers configure the interface for the chip selects, which

support ADMUX or ADNOMUX. See Table 11-6 on page 829 for details on which configuration

register controls each chip select. If the CSBAUD bit is clear, all chip selects are configured by the

MODE bit field of the EPIHBnCFG register.

If the CSBAUD bit in the EPIHBnCFG2 register is set in Dual-chip select mode, the 2 chip selects

can use different clock frequencies, wait states and strobe polarity. If the CSBAUD bit is clear, both

chip selects use the clock frequency, wait states, and strobe polarity defined for CS0n. Additionally,

if the CSBAUD bit is set, the two chip selects can use different interface modes. If any interface modes

are programmed to ADMUX, then dual chip select mode must include the ALE capability. In quad

chip select mode, if the CSBAUD bit in the EPIHBnCFG2 register is set, the 4 chip selects can use

different clock frequencies, wait states and strobe polarity. If the CSBAUD bit is clear, all chip selects

use the clock frequency, wait states, and strobe polarity defined for CS0n. If the CSBAUD bit is set,

the four chip selects can use different interface modes.

June 18, 2014828

Texas Instruments-Production Data

External Peripheral Interface (EPI)

Loading...

Loading...