Register 70: MPU Control (MPUCTRL), offset 0xD94

Note: This register can only be accessed from privileged mode.

The MPUCTRL register enables the MPU, enables the default memory map background region,

and enables use of the MPU when in the hard fault, Non-maskable Interrupt (NMI), and Fault Mask

Register (FAULTMASK) escalated handlers.

When the ENABLE and PRIVDEFEN bits are both set:

■ For privileged accesses, the default memory map is as described in “Memory Model” on page 103.

Any access by privileged software that does not address an enabled memory region behaves

as defined by the default memory map.

■ Any access by unprivileged software that does not address an enabled memory region causes

a memory management fault.

Execute Never (XN) and Strongly Ordered rules always apply to the System Control Space regardless

of the value of the ENABLE bit.

When the ENABLE bit is set, at least one region of the memory map must be enabled for the system

to function unless the PRIVDEFEN bit is set. If the PRIVDEFEN bit is set and no regions are enabled,

then only privileged software can operate.

When the ENABLE bit is clear, the system uses the default memory map, which has the same

memory attributes as if the MPU is not implemented (see Table 2-5 on page 107 for more information).

The default memory map applies to accesses from both privileged and unprivileged software.

When the MPU is enabled, accesses to the System Control Space and vector table are always

permitted. Other areas are accessible based on regions and whether PRIVDEFEN is set.

Unless HFNMIENA is set, the MPU is not enabled when the processor is executing the handler for

an exception with priority –1 or –2. These priorities are only possible when handling a hard fault or

NMI exception or when FAULTMASK is enabled. Setting the HFNMIENA bit enables the MPU when

operating with these two priorities.

MPU Control (MPUCTRL)

Base 0xE000.E000

Offset 0xD94

Type RW, reset 0x0000.0000

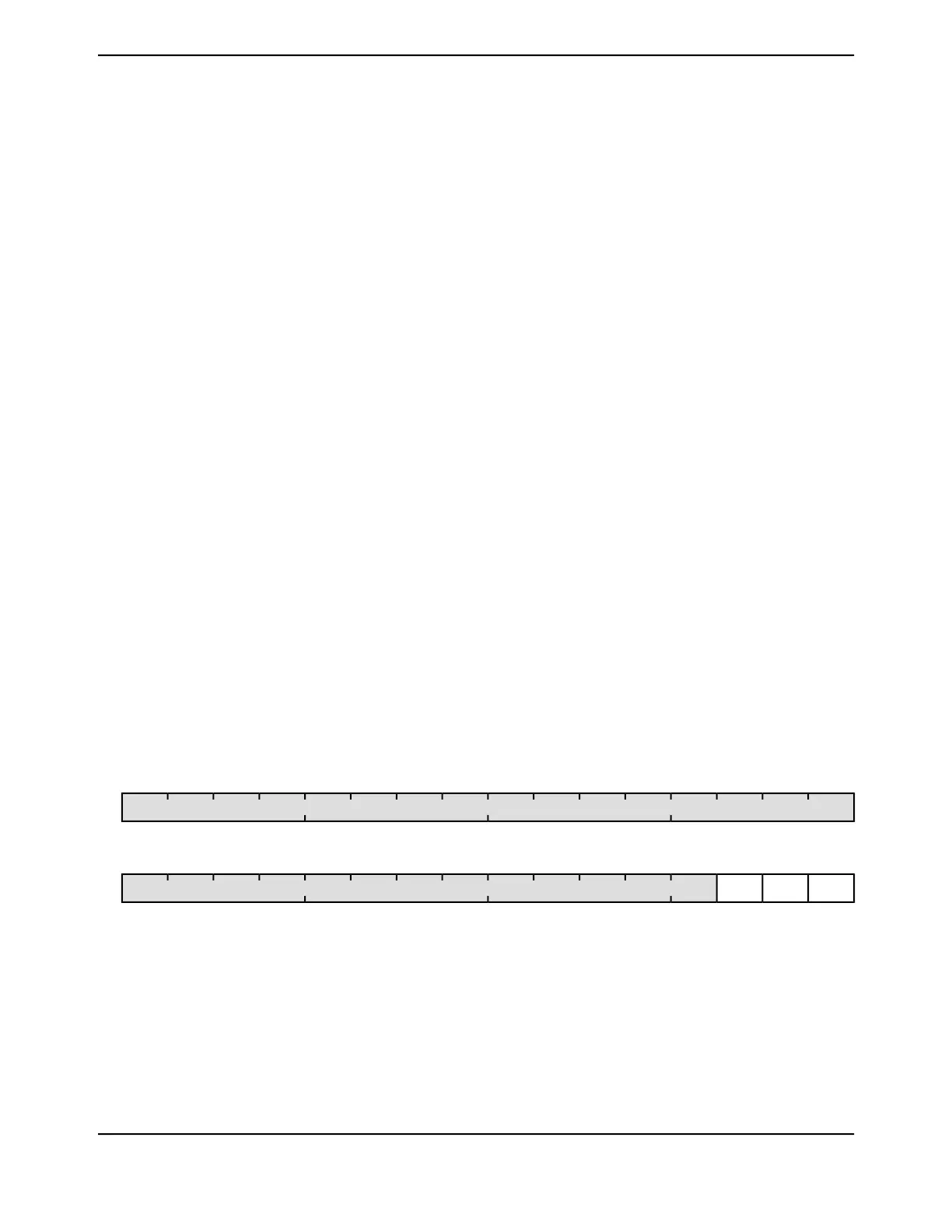

16171819202122232425262728293031

reserved

ROROROROROROROROROROROROROROROROType

0000000000000000Reset

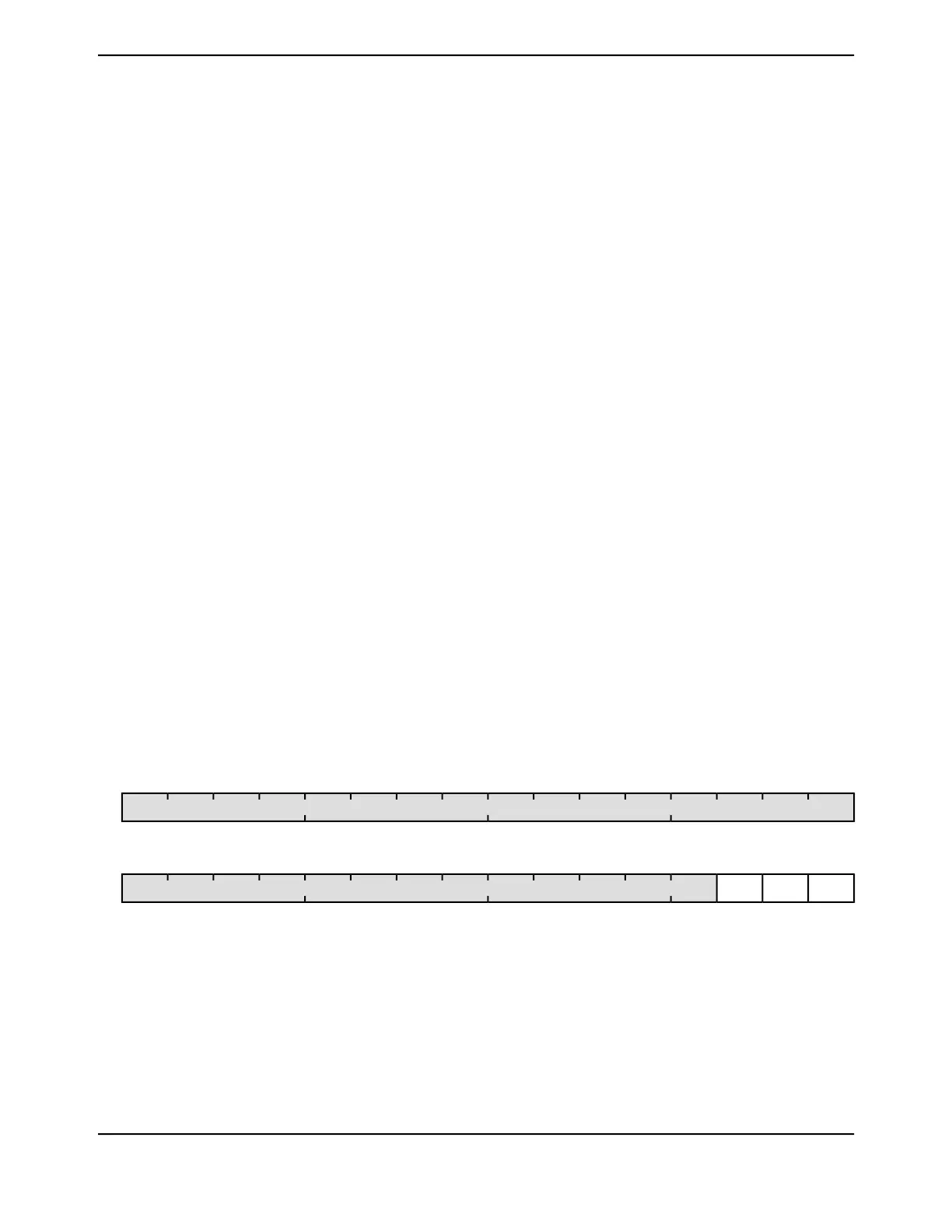

0123456789101112131415

ENABLE

HFNMIENA

PRIVDEFEN

reserved

RWRWRWROROROROROROROROROROROROROType

0000000000000000Reset

DescriptionResetTypeNameBit/Field

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x0000.000ROreserved31:3

June 18, 2014194

Texas Instruments-Production Data

Cortex-M4 Peripherals

Loading...

Loading...