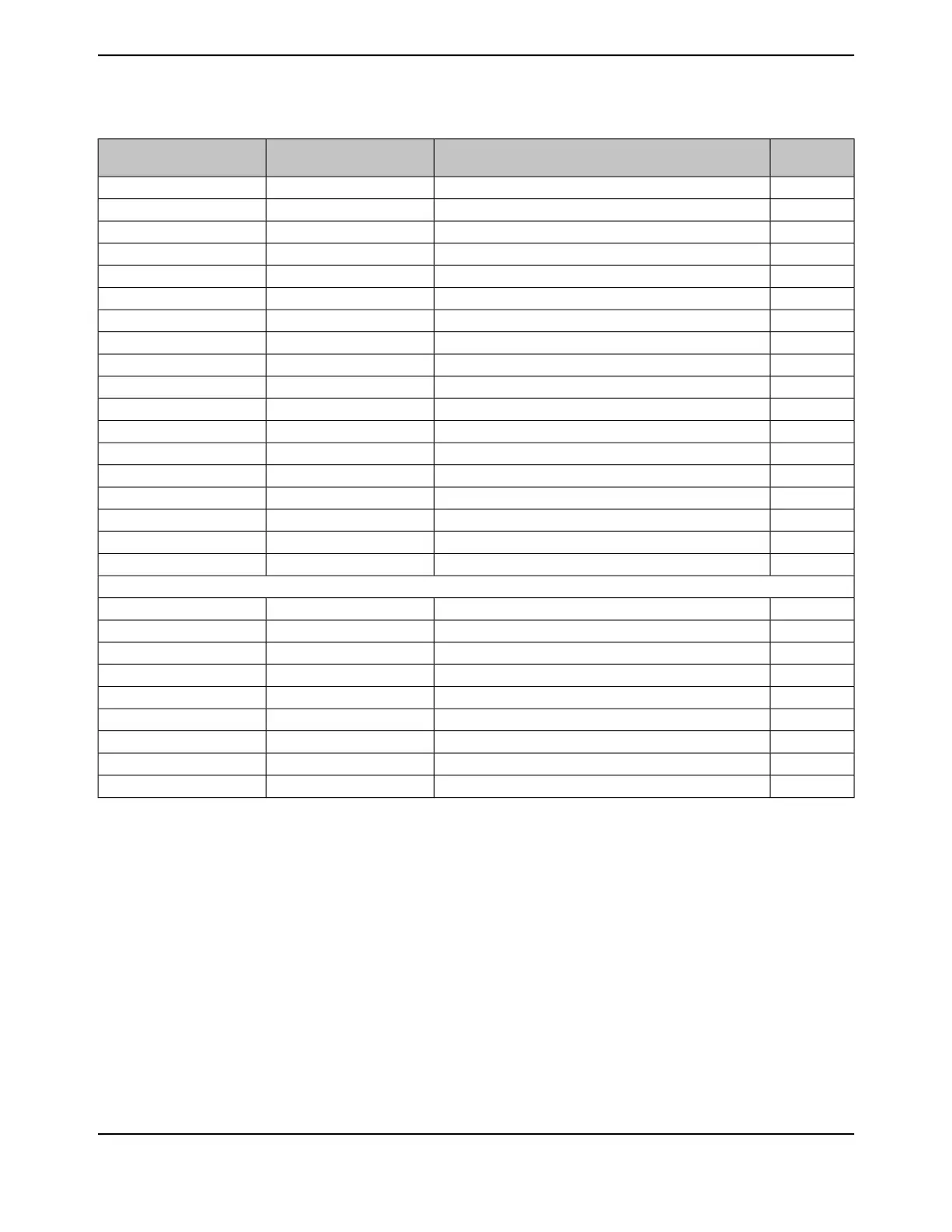

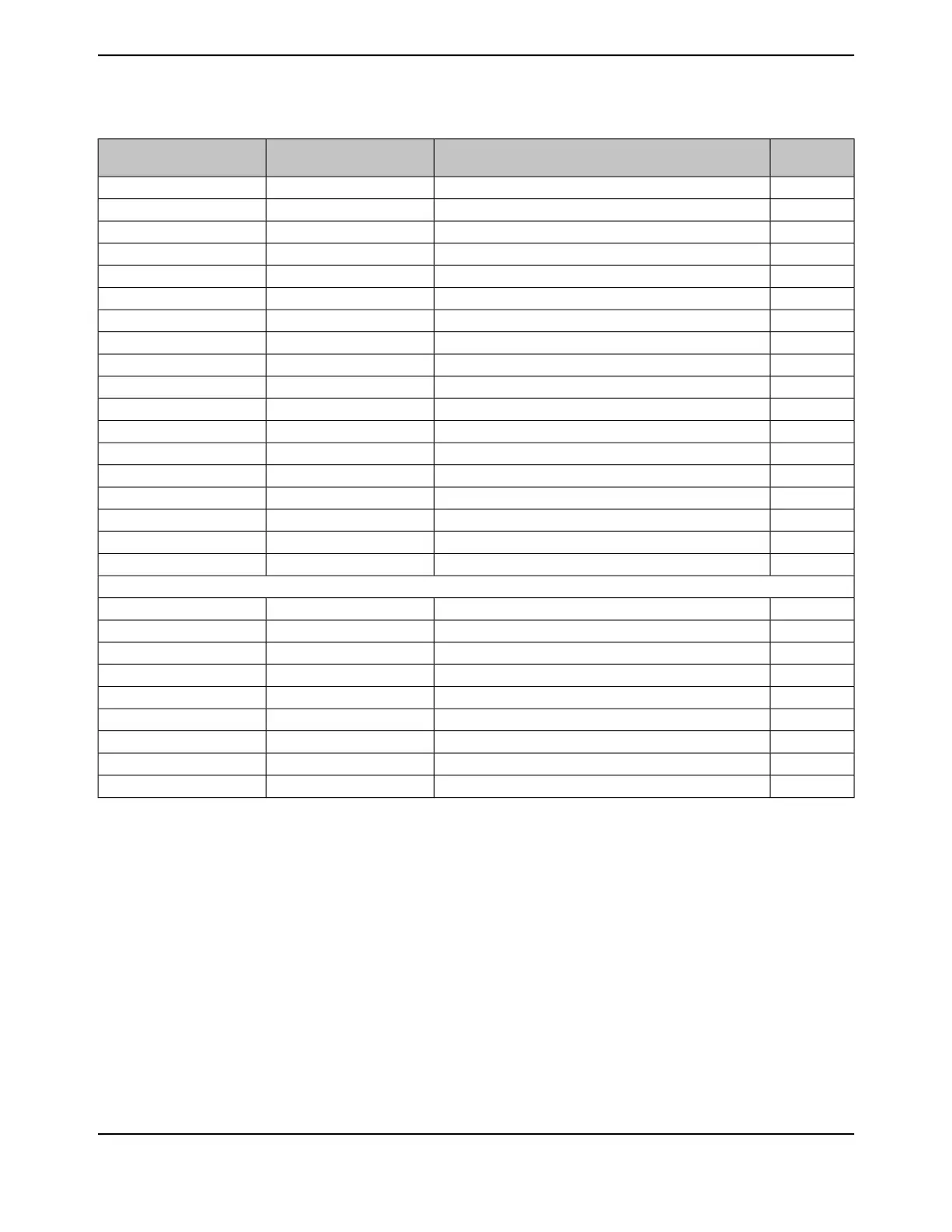

Table 2-4. Memory Map (continued)

For details,

see page ...

DescriptionEndStart

-Reserved0x400F.BFFF0x400F.A000

551Hibernation Module0x400F.CFFF0x400F.C000

621Flash memory control0x400F.DFFF0x400F.D000

247System control0x400F.EFFF0x400F.E000

701µDMA0x400F.FFFF0x400F.F000

-Reserved0x41FF.FFFF0x4010.0000

-Bit-banded alias of 0x4000.0000 through 0x400F.FFFF0x43FF.FFFF0x4200.0000

-Reserved0x4402.FFFF0x4400.0000

-CRC Module0x4403.0FFF0x4403.0000

-Reserved [4 kB]0x4403.1FFF0x4403.1000

-Reserved [8 kB]0x4403.3FFF0x4403.2000

-Reserved0x4403.EFFF0x4403.4000

-Reserved [4 kB]0x4403.FFFF0x4403.F000

-Reserved [64 kB]0x4404.FFFF0x4404.0000

-Reserved0x4405.3FFF0x4405.0000

1467EPHY 00x4405.4FFF0x4405.4000

-Reserved0x5FFF.FFFF0x4405.5000

-EPI0 mapped peripheral and RAM0xDFFF.FFFF0x6000.0000

Private Peripheral Bus

82Instrumentation Trace Macrocell (ITM)0xE000.0FFF0xE000.0000

82Data Watchpoint and Trace (DWT)0xE000.1FFF0xE000.1000

82Flash Patch and Breakpoint (FPB)0xE000.2FFF0xE000.2000

-Reserved0xE000.DFFF0xE000.3000

146Cortex-M4F Peripherals (SysTick, NVIC, MPU, FPU and SCB)0xE000.EFFF0xE000.E000

-Reserved0xE003.FFFF0xE000.F000

83Trace Port Interface Unit (TPIU)0xE004.0FFF0xE004.0000

82Embedded Trace Macrocell (ETM)0xE004.1FFF0xE004.1000

-

Reserved0xFFFF.FFFF0xE004.2000

2.4.1 Memory Regions, Types and Attributes

The memory map and the programming of the MPU split the memory map into regions. Each region

has a defined memory type, and some regions have additional memory attributes. The memory

type and attributes determine the behavior of accesses to the region.

The memory types are:

■ Normal: The processor can re-order transactions for efficiency and perform speculative reads.

■ Device: The processor preserves transaction order relative to other transactions to Device or

Strongly Ordered memory.

■ Strongly Ordered: The processor preserves transaction order relative to all other transactions.

June 18, 2014106

Texas Instruments-Production Data

The Cortex-M4F Processor

Loading...

Loading...