Register 15: EPI Non-Blocking Read Data 0 (EPIRPSTD0), offset 0x028

Register 16: EPI Non-Blocking Read Data 1 (EPIRPSTD1), offset 0x038

This register sets up a non-blocking read via the external interface. A non-blocking read is started

by writing to this register with the count (other than 0). Clearing this register terminates an active

non-blocking read as well as cancelling any that are pending. This register should always be cleared

before writing a value other than 0; failure to do so can cause improper operation. Note that both

NBR channels can be enabled at the same time, but NBR channel 0 has the highest priority and

channel 1 does not start until channel 0 is finished.

The first address is based on the corresponding EPIRADDRn register. The address register is

incremented by the size specified by the EPIRSIZEn register after each read. If the size is less than

a word, only the least significant bits of data are filled into the NBRFIFO; the most significant bits

are cleared.

Note that all three registers may be written using one STM instruction, such as with a structure copy

in C/C++.

The data may be read from the EPIREADFIFO register after the read cycle is completed. The

interrupt mechanism is normally used to trigger the FIFO reads via ISR or μDMA.

If the countdown has not reached 0 and the NBRFIFO is full, the external interface waits until a

NBRFIFO entry becomes available to continue.

Note: if a blocking read or write is performed through the address mapped area (at 0x6000.0000

through 0xDFFF.FFFF), any current non-blocking read is paused (at the next safe boundary), and

the blocking request is inserted. After completion of any blocking reads or writes, the non-blocking

reads continue from where they were paused.

The other way to read data is via the address mapped locations (see the EPIADDRMAP register),

but this method is blocking (core or μDMA waits until result is returned).

To cancel a non-blocking read, clear this register. To make sure that all values read are drained

from the NBRFIFO, the EPISTAT register must be consulted to be certain that bits NBRBUSY and

ACTIVE are cleared. One of these registers should not be cleared until either the other EPIRPSTDn

register becomes active or the external interface is not busy. At that point, the corresponding

EPIRADDRn register indicates how many values were read.

EPI Non-Blocking Read Data n (EPIRPSTDn)

Base 0x400D.0000

Offset 0x028

Type RW, reset 0x0000.0000

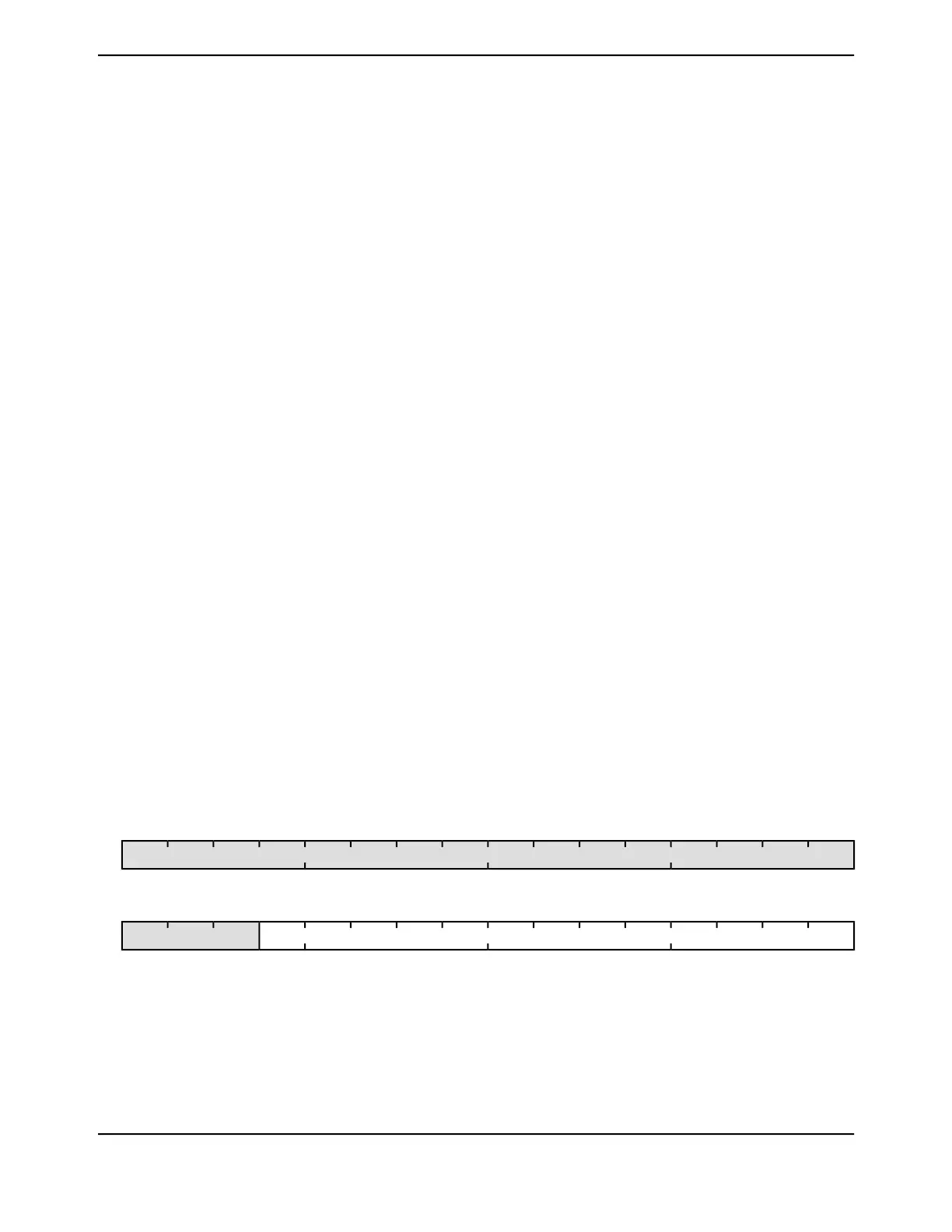

16171819202122232425262728293031

reserved

ROROROROROROROROROROROROROROROROType

0000000000000000Reset

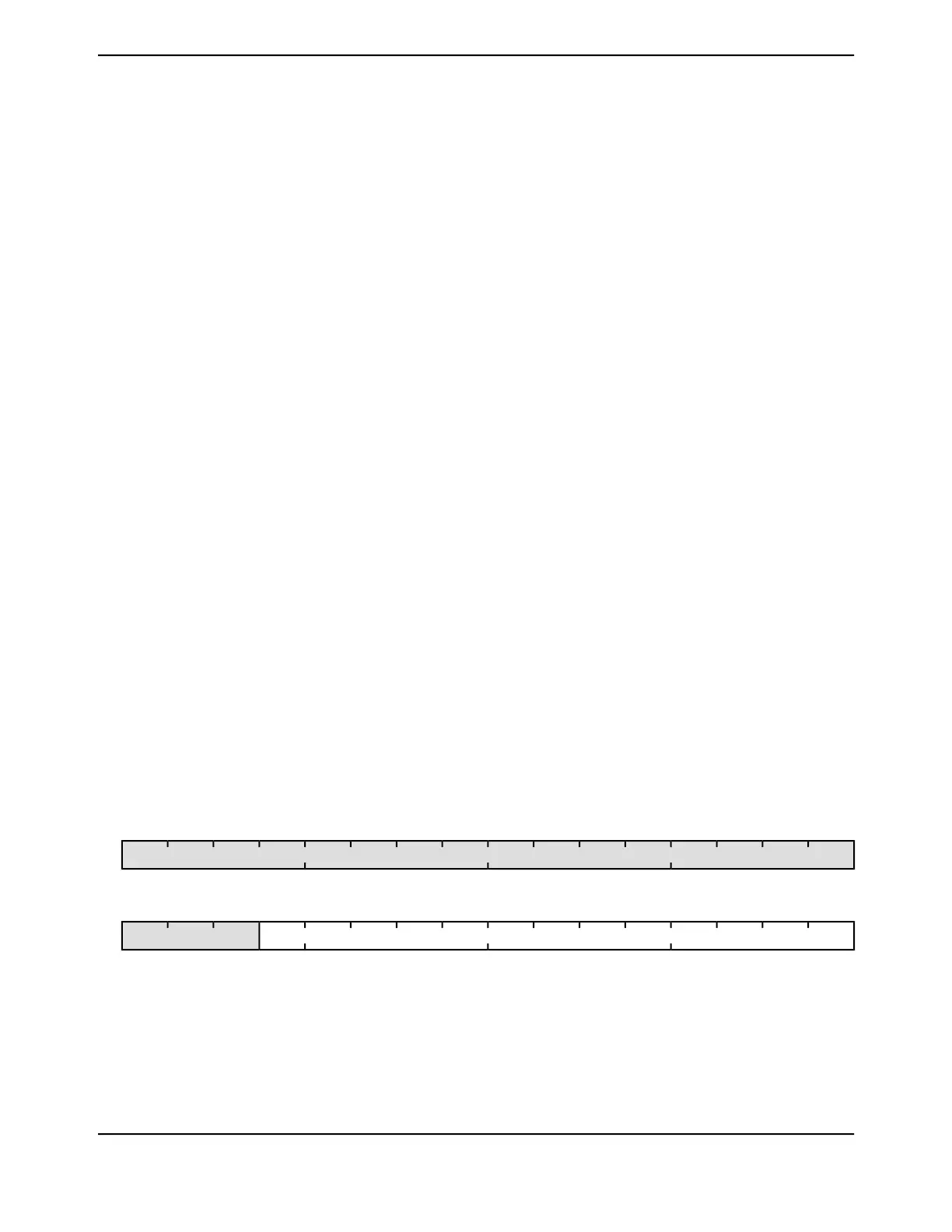

0123456789101112131415

POSTCNTreserved

RWRWRWRWRWRWRWRWRWRWRWRWRWROROROType

0000000000000000Reset

DescriptionResetTypeNameBit/Field

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x0000.0ROreserved31:13

897June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...