receive a Quick Command, it should be expecting such a command because it must write the

I2CSDR with a specific value when R/S is set.

18.3.2 Available Speed Modes

The I

2

C bus can run in Standard mode (100 kbps), Fast mode (400 kbps), Fast mode plus (1 Mbps)

or High-Speed mode (3.4 Mbps, provided correct system clock frequency is set and there is

appropriate pull strength on SCL and SDA lines). The selected mode should match the speed of

the other I

2

C devices on the bus.

18.3.2.1 Standard, Fast, and Fast Plus Modes

Standard, Fast, and Fast Plus modes are selected using a value in the I

2

C Master Timer Period

(I2CMTPR) register that results in an SCL frequency of 100 kbps for Standard mode, 400 kbps for

Fast mode, or 1 Mbps for Fast mode plus.

The I

2

C clock rate is determined by the parameters CLK_PRD, TIMER_PRD, SCL_LP, and SCL_HP

where:

CLK_PRD is the system clock period

SCL_LP is the low phase of SCL (fixed at 6)

SCL_HP is the high phase of SCL (fixed at 4)

TIMER_PRD is the programmed value in the I2CMTPR register (see page 1313). This value is

determined by replacing the known variables in the equation below and solving for TIMER_PRD.

The I

2

C clock period is calculated as follows:

SCL_PERIOD = 2 × (1 + TIMER_PRD) × (SCL_LP + SCL_HP) × CLK_PRD

For example:

CLK_PRD = 50 ns

TIMER_PRD = 2

SCL_LP=6

SCL_HP=4

yields a SCL frequency of:

1/SCL_PERIOD = 333 Khz

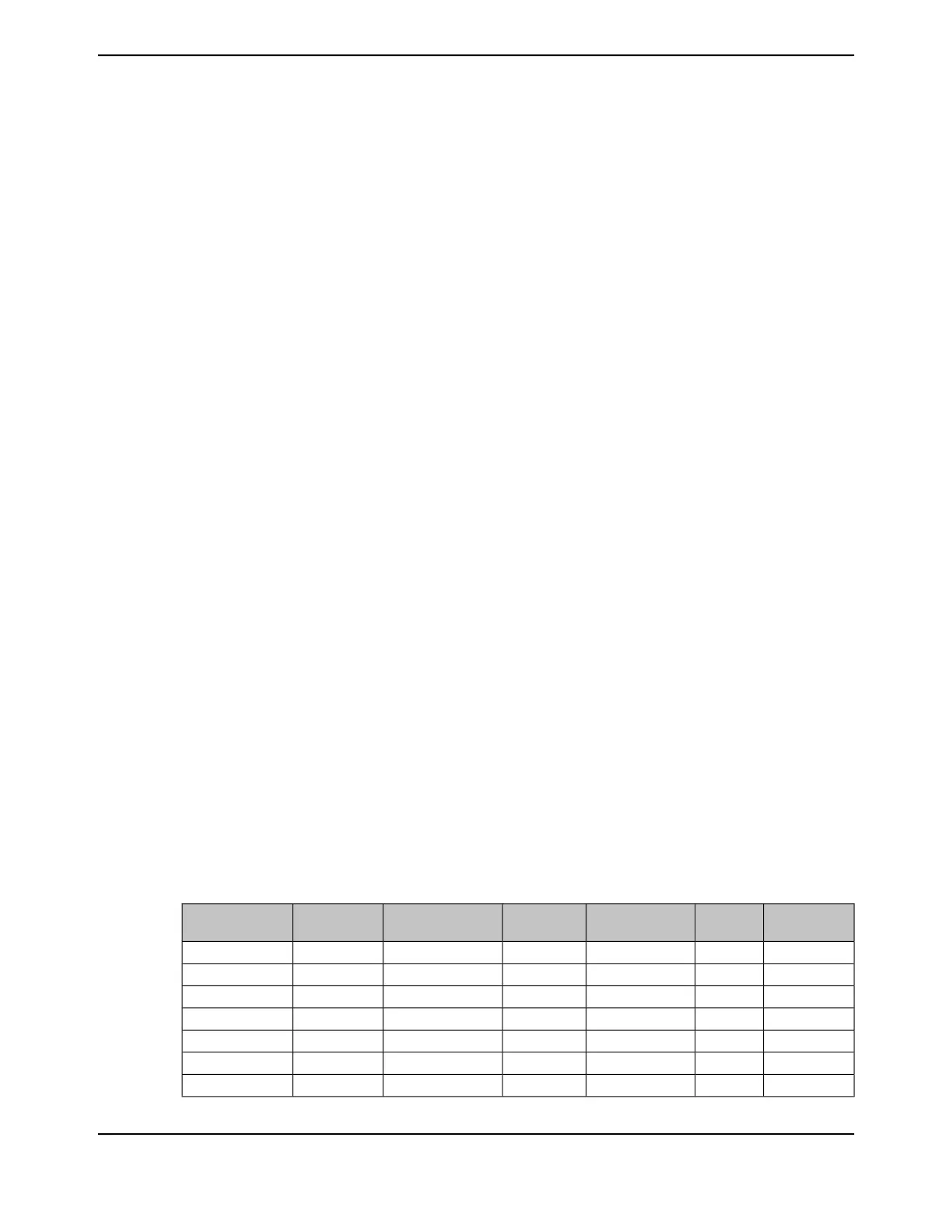

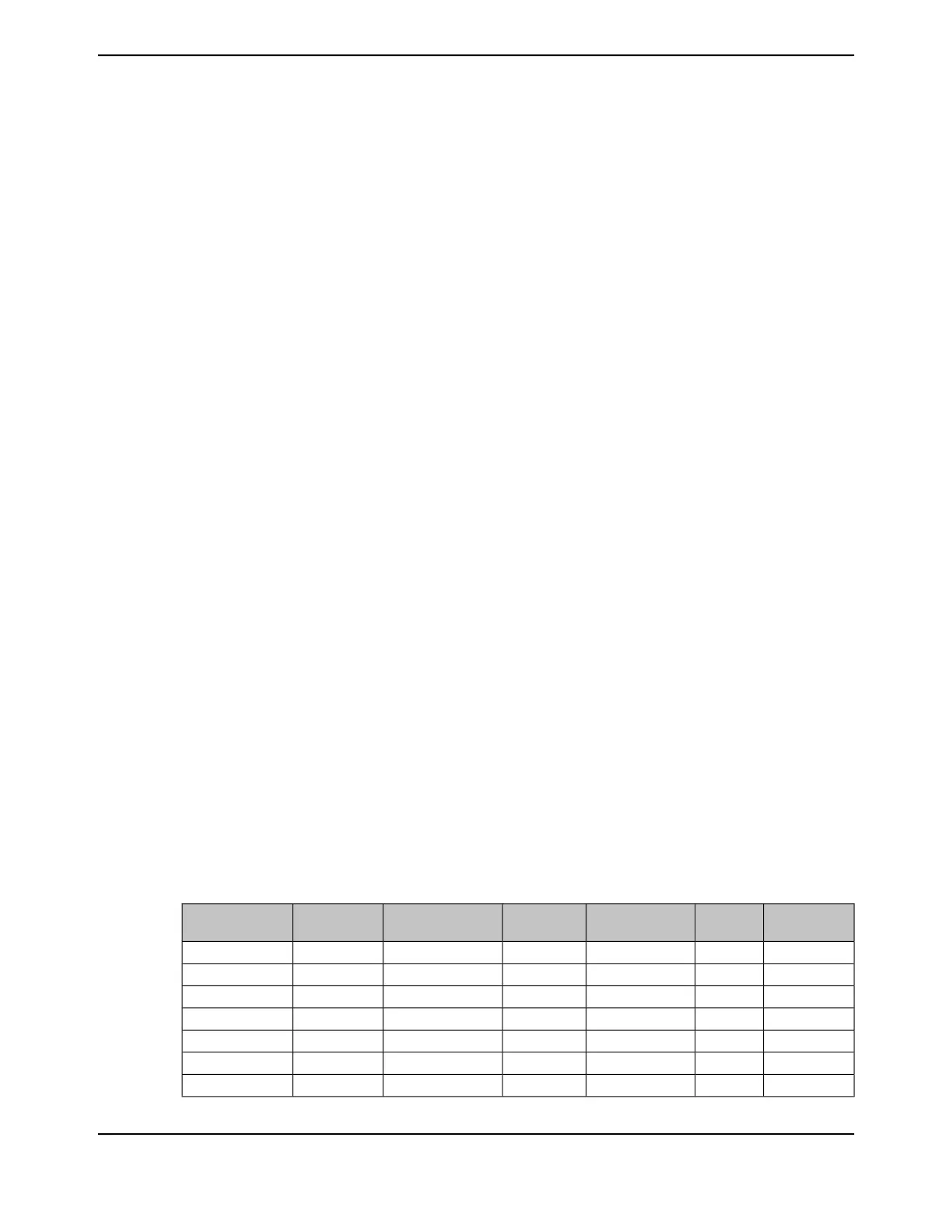

Table 18-2 gives examples of the timer periods that should be used to generate Standard, Fast

mode, and Fast mode plus SCL frequencies based on various system clock frequencies.

Table 18-2. Examples of I

2

C Master Timer Period Versus Speed Mode

Fast Mode

Plus

Timer

Period

Fast ModeTimer PeriodStandard ModeTimer PeriodSystem Clock

----100 Kbps0x014 MHz

----100 Kbps0x026 MHz

--312 Kbps0x0189 Kbps0x0612.5 MHz

--278 Kbps0x0293 Kbps0x0816.7 MHz

--333 Kbps0x02100 Kbps0x0920 MHz

--312 Kbps0x0396.2 Kbps0x0C25 MHz

--330 Kbps0x0497.1 Kbps0x1033 MHz

June 18, 20141284

Texas Instruments-Production Data

Inter-Integrated Circuit (I

2

C) Interface

Loading...

Loading...