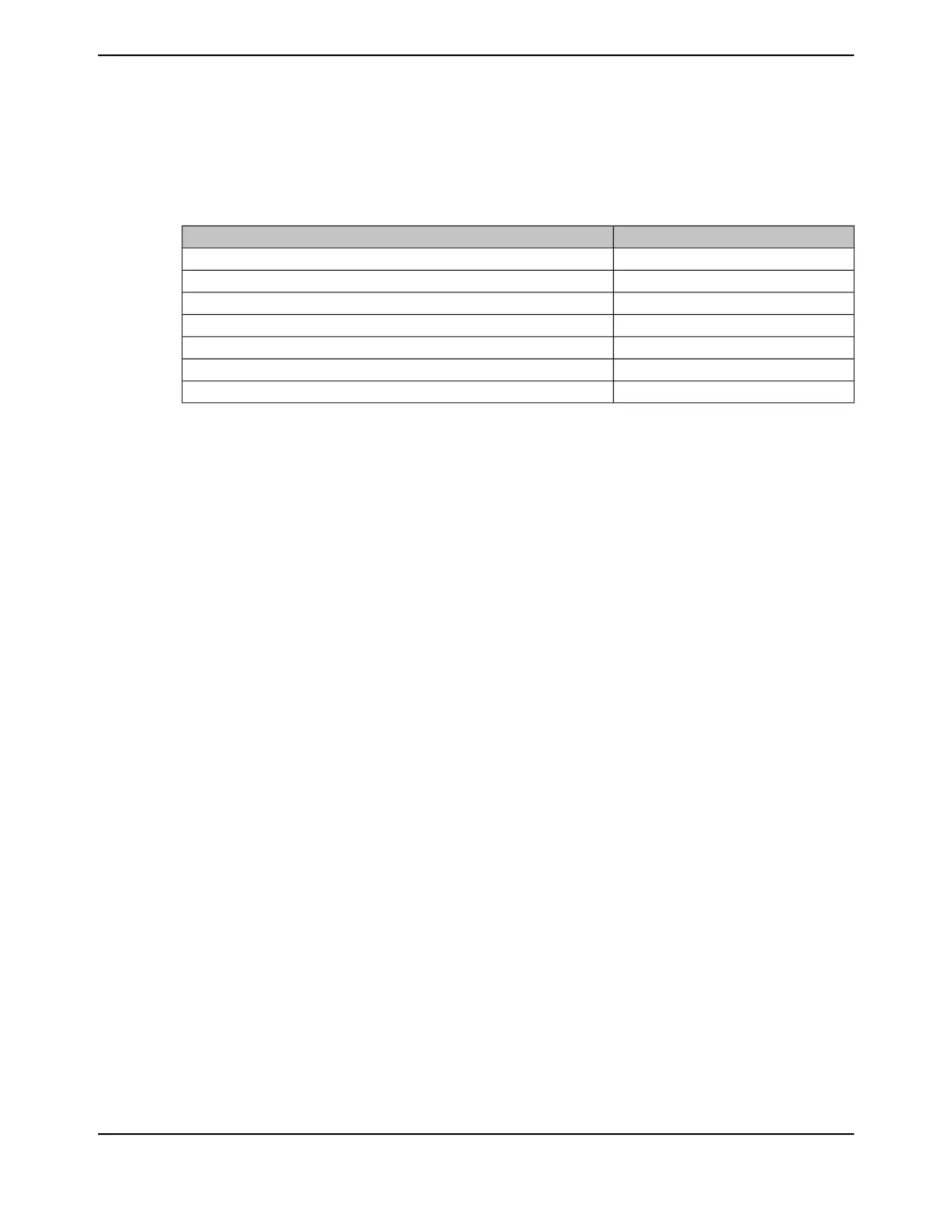

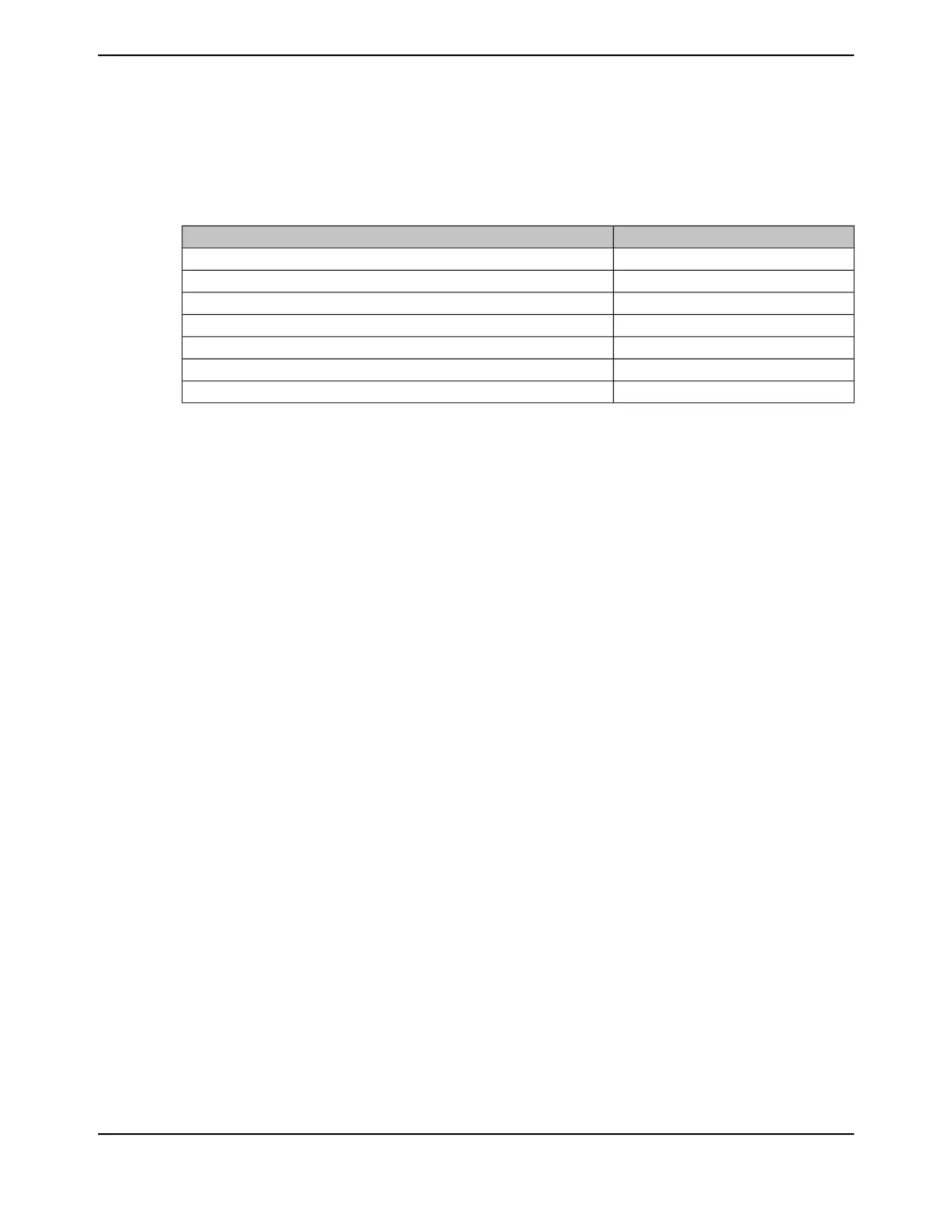

11.4.1 EPI Interface Options

There are a variety of memories and peripherals that can interface to the EPI module. Table

11-2 on page 822 shows the various configurations with their maximum performance.

Table 11-2. EPI Interface Options

Maximum FrequencyInterface

60 MHzSingle SDRAM

60 MHzSingle SRAM

55 MHzSingle PSRAM without iRDY signal use

52 MHzSingle PSRAM with iRDY signal use

60 MHzFPGAs, CPLDs, etc using General Purpose Mode

40 MHzMemory configurations with 2 chip selects

20 MHzMemory configurations with 4 chip selects

11.4.2 SDRAM Mode

When activating the SDRAM mode, it is important to consider a few points:

1. Generally, it takes over 100 μs from when the mode is activated to when the first operation is

allowed. The SDRAM controller begins the SDRAM initialization sequence as soon as the mode

is selected and enabled via the EPICFG register. It is important that the GPIOs are properly

configured before the SDRAM mode is enabled, as the EPI controller is relying on the GPIO

block's ability to drive the pins immediately. As part of the initialization sequence, the LOAD

MODE REGISTER command is automatically sent to the SDRAM with a value of 0x27, which

sets a CAS latency of 2 and a full page burst length.

2. The INITSEQ bit in the EPI Status (EPISTAT) register can be checked to determine when the

initialization sequence is complete.

3. When using a frequency range and/or refresh value other than the default value, it is important

to configure the FREQ and RFSH fields in the EPI SDRAM Configuration (EPISDRAMCFG)

register shortly after activating the mode. After the 100-μs startup time, the EPI block must be

configured properly to keep the SDRAM contents stable.

4. The SLEEP bit in the EPISDRAMCFG register may be configured to put the SDRAM into a

low-power self-refreshing state. It is important to note that the SDRAM mode must not be

disabled once enabled, or else the SDRAM is no longer clocked and the contents are lost.

5. Before entering SLEEP mode, make sure all non-blocking reads and normal reads and writes

have completed. If the system is running at 30 to 50 MHz, wait 2 EPI clocks after clearing the

SLEEP bit before executing non-blocking reads, or normal reads and writes. If the system is

configured to greater than 50 MHz, wait 5 EPI clocks before read and write transactions. For

all other configurations, wait 1 EPI clock.

The SIZE field of the EPISDRAMCFG register must be configured correctly based on the amount

of SDRAM in the system.

The FREQ field must be configured according to the value that represents the range being used.

Based on the range selected, the number of external clocks used between certain operations (for

example, PRECHARGE or ACTIVATE) is determined. If a higher frequency is given than is used,

then the only downside is that the peripheral is slower (uses more cycles for these delays). If a lower

frequency is given, incorrect operation occurs.

June 18, 2014822

Texas Instruments-Production Data

External Peripheral Interface (EPI)

Loading...

Loading...